Fターム[5F049PA11]の内容

受光素子−フォトダイオード・Tr (21,418) | 製造方法(工程) (2,065) | 熱処理 (139)

Fターム[5F049PA11]の下位に属するFターム

光アニール (23)

Fターム[5F049PA11]に分類される特許

101 - 116 / 116

アバランシェフォトダイオードの製造方法

【課題】拡散領域の形成が容易で、拡散領域を形成する際に誤差の発生を最小化することができるアバランシェフォトダイオードの製造方法を提供する。

【解決手段】本発明は、半導体基板上に、増幅層を含む複数の半導体層を順次形成する第1工程と、半導体層上における拡散領域の周辺部を形成しようとする部分に、増幅層と異なる拡散係数を有する拡散パターンを形成する第2工程と、拡散パターンを介して不純物を拡散させることによって、周辺部と中心部の深さが異なる拡散領域を形成する第3工程とを含むことを特徴とする。

(もっと読む)

紫外線検出素子

【課題】 燃焼制御に用いる発光強度検出素子として、可視光に感度を持たず、300度以上で安定に動作が可能な紫外線を高感度で検出できる小型の半導体受光素子を提供することである。

【解決手段】n形SiC基板に導電性酸化物層とオーミック電極を形成し、ダイオードを作製する。導電性酸化物層の直下又は周辺のn形SiC層に光が入射すると、前記ダイオードは紫外線検出素子として機能する。

(もっと読む)

固体撮像装置及びその製造方法

【課題】 画素が微細化された固体撮像装置の信号読み出し特性、暗電流特性及び白キズ特性を改善する。

【解決手段】 基板上101に、光電変換(PD)部106、フローティングディフュージョン(FD)部107、ゲート電極104及び埋め込み領域108を備える固体撮像装置の製造方法で、基板101上にゲート電極104を形成する工程と、基板101に不純物を導入してPD部106を形成する工程と、ゲート電極104及びPD部106を覆う絶縁膜109を形成する工程と、絶縁膜109をエッチングし、PD部106上にサリサイド化防止膜109bを残しながらゲート電極104の側面にサイドウォール109aを形成する工程と、PD部106の表層部に、少なくともサイドウォール109aをマスクとし且つサリサイド化防止膜109bを介してPD部106と反対導電型の不純物を導入し、埋め込み領域108を形成する工程とを備える。

(もっと読む)

固体撮像装置及びその製造方法

【課題】 単位画素の光電変換効率を向上させることができる固体撮像装置及びその製造方法を提供する

【解決手段】 光電変換部となるフォトダイオードPDの形成工程において、イオン注入によりフォトダイオードPDの電荷蓄積領域17を形成した後、熱拡散により電荷蓄積領域17を素子分離膜13の下方に延在し、かつ拡散層14に当接または近接するように形成する。これにより、画素内における光電変換部の電荷蓄積領域(面積)を増大できる。

(もっと読む)

光電変換素子及びこれを用いた表示装置

【課題】 p−MOSプロセスによって駆動回路と同時に作り込むことが可能で、しかも特性に優れた光電変換素子を提供する。

【解決手段】 p型不純物が注入された一対のp+領域4,5と、p+領域4,5の間に配されp+領域よりもp型不純物の濃度が低いp−領域(受光層10)とを有し、p−領域上にゲート絶縁6膜を介してゲート電極7が形成されてなるp−MOS構造の光電変換素子である。ゲート電極7の幅Wがp−領域の幅よりも小であり、ゲート電極下のp−領域が受光層10として機能するとともに、ゲート電極下から外れた部分のp−領域がLDD領域8,9として機能する。この光電変換素子を駆動回路用の薄膜トランジスタ(pチャンネルTFT)と同一基板上に作り込むことで、低コストで入力機能付き表示装置が実現される。

(もっと読む)

シリコン光素子の製造方法及びそれにより製造されたシリコン光素子、並びにそれを適用した画像入出力装置

【課題】シリコン光素子の製造方法及びそれにより製造されたシリコン光素子、並びにそれを適用した画像入出力装置を提供する。

【解決手段】シリコン基板を準備する工程と、基板一面の少なくとも一部位に、微小キャビティを持つ微小欠陥屈曲を形成するためのポリシリコンを形成する工程と、ポリシリコンが形成された基板の面を酸化させるシリコン酸化層の形成過程で、ポリシリコンと前記基板をなす物質との酸化率差に起因して、シリコン酸化層と基板との界面に微小キャビティを持つ微小欠陥屈曲を形成する工程と、シリコン酸化層のポリシリコンが形成されていた部位をエッチングして、シリコン酸化層の形成過程で、シリコン酸化層と基板との界面に形成された微小欠陥屈曲を露出させる工程と、露出された微小結合屈曲部分を基板と反対型にドーピングして、ドーピング領域を形成する工程と、を含むことを特徴とするシリコン光素子の製造方法。

(もっと読む)

シリコンウェハに結合することによる薄膜ゲルマニウムの赤外線センサの製造

【課題】ゲルマニウム結合後に高温プロセスの必要性のない、薄膜ゲルマニウム光検出器の製造方法を提供する。

【解決手段】本発明による薄膜ゲルマニウム光検出器を製造する方法は、シリコン基板を準備することと(12)、CMOSデバイスをシリコン基板上に製造することと(14)、ゲルマニウム基板を準備することと(30)、結合するために各基板の表面を準備することと(34)、ゲルマニウム基板を、CMOSを有するシリコン基板に結合して、結合構造を形成することと(38)、ゲルマニウム基板の一部分を結合構造から除去することと、PINダイオードをゲルマニウム基板に形成することと(46)、ゲルマニウム層の一部分をエッチングによって除去することと(52)、ゲルマニウム光検出器を完成させることと(64)を包含する。

(もっと読む)

能動領域の欠陥が低減されユニークな接触スキームを有する半導体デバイス

欠陥密度が低減された能動領域など所定のエピタキシャル領域を有した半導体デバイスを製作する方法は、

(a)第1の材料の単一結晶体の主表面上に、誘電性クラッド領域を形成する工程と、

(b)クラッド領域中に第1の深さまで延びる第1の開口を形成する工程と、

(c)第1の開口内において、第1の深さより深い第2の深さまで延び、単一結晶体の主表面の下にある部分を剥き出しにする、より小さい第2の開口を形成する工程と、

(d)各開口中およびクラッド領域の上部上に、第2の半導体材料の領域をエピタキシャル的に成長させる工程と、

(e)第2の開口内およびクラッド領域の上部上で成長したエピタキシャル領域に、欠陥を閉じ込め、第1の所定の領域が、第1の開口内に配置されて本質的に欠陥がないように、第2の開口の寸法を制御する工程と、

(f)デバイスの上部を平坦化して、クラッド層の上部の上に延在するエピタキシャル領域をすべて除去し、それによって第2の開口中に成長した第1の所定の領域の上部を、ぜひともクラッド領域の上部と同一平面にさせる工程と、

(g)デバイスの組み立てを完成させるために、追加の工程を実施する工程とを含む。さらに記述されるのは、この方法によって製造される光センサやMOSFETなどのユニークなデバイス、ならびにそれらデバイスの性能を高めるユニークな接触構成である。  (もっと読む)

(もっと読む)

固体撮像装置

【課題】暗電流および消費電力が増大するのを抑制しながら、電子の転送効率の低下を抑制することが可能な固体撮像装置を提供する。

【解決手段】この固体撮像装置は、n型シリコン基板8のn+型不純物領域12の深さよりも大きく、かつ、n型不純物領域10の深さよりも小さい深さを有するn型中間不純物領域11を含む電荷蓄積領域を備えている。

(もっと読む)

大口径受光部のための電極構造を有したフォトダイオード

本発明は、受光部を大口径化できるフォトダイオードの構造に関する。本発明によれば、光電変換のための化合物半導体の接合構造を有した受光部と、前記受光部一面の光入射領域にオーム接触された網構造の第1電極と、前記第1電極と対応するように前記受光部の他面に形成される第2電極とを含むフォトダイオードが開示される。 (もっと読む)

画像センサのための重水素化構造体およびその形成方法

光変換デバイスと、少なくとも1つの構造体とを有する画素セルは、光変換デバイスに隣接する重水素化材料を含む。  (もっと読む)

(もっと読む)

受光素子及び受光素子の製造方法

【課題】不良が発生しにくく生産性に優れるとともに低コストで実現することが可能な受光素子を提供する。

【解決手段】受光素子を、n型InP基板と、前記n型InP基板の上に積層されるn型InP緩和層と、前記n型InP緩和層の上に積層されるi型(n型)InGaAs光吸収層と、前記i型(n型)InGaAs光吸収層の上に積層されるn型InPキャップ層と、前記n型InPキャップ層より前記i型(n型)InGaAs光吸収層に至るまでp型不純物をイオン注入することにより形成され、前記i型(n型)InGaAs光吸収層とpn接合を形成するp型不純物領域とを有し、前記p型不純物領域の上部に前記p型不純物領域とオーミック接合するTi/Pt/Au電極が形成されてなり、前記オーミック電極がワイヤボンド用のアノード電極を兼ねる構造とする。

(もっと読む)

ゲルマニウム基板タイプ材料およびその手法

ゲルマニウム回路タイプの構造が促進される。一実施形態例では、多段階の成長およびアニール・プロセスを実施して、ヘテロエピタキシャルル・ゲルマニウムなどのゲルマニウム(Ge)含有材料を、シリコン(Si)またはシリコン含有材料を含む基板上に成長させる。いくつかの応用例では、ゲルマニウム含有材料の上面に向かって貫通する欠陥が全体的に抑制されて、欠陥が全体的にシリコン/ゲルマニウム境界面付近に閉じ込められる。これらの手法は、ゲルマニウムMOSコンデンサ、pMOSFET、およびオプトエレクトロニック・デバイスを含む、さまざまなデバイスに適用できる。  (もっと読む)

(もっと読む)

非結晶性シリコン垂直カラーフィルター

【課題】イメージセンサーの面積を縮小するとともに微細で簡単なセンサー回路を達成し、製造プロセスが容易な高感度のイメージサンサーを提供する。

【解決手段】半導体集積回路製造プロセスによって、半導体基板上に、少なくとも2つの垂直に積層した感光性センサーを有する垂直カラーフィルターセンサー群を形成する。各々のセンサーは異なるスペクトル応答を持つ。少なくとも1つのセンサーは結晶性シリコン以外の半導体材料、たとえばシリコンカーバイド、InxGa1−xN、III−V族半導体材料、ポリシリコン、またはアモルファスシリコンなどの少なくとも1つの層を含む。本発明の他の特徴は、垂直カラーフィルターセンサー群、およびこのような垂直カラーフィルターセンサー群とそれらのアレイの製造方法である。また少なくとも1つのセンサーは光子吸収領域およびアバランシェ・ゲイン領域を持つ。

(もっと読む)

高速CMOS共存Ge−オン−インシュレータ光検出器の構造および製作方法

【課題】SiCMOS技術と共存可能な高速高効率光検出器を作る問題に対処すること。

【解決手段】本構造は、薄いSOI基板の上のGe吸収層から成り、分離領域、交互になるn型およびp型コンタクト、および低抵抗表面電極を利用する。本デバイスは、下の基板で生成されたキャリアを分離するために埋込み絶縁物を利用して高帯域幅を、Ge吸収層を利用して広いスペクトルにわたった高量子効率を、薄い吸収層および狭い電極間隔を利用して低電圧動作を、さらに平面構造およびIV族吸収材料の使用によってCMOSデバイスとの共存性を、達成する。本光検出器を製作する方法は、薄いSOIまたはエピタキシャル酸化物へのGeの直接成長および高品質吸収層を達成するための後の熱アニールを使用する。この方法は、相互拡散に利用可能なSiの量を制限し、それによって、下のSiによるGe層の実質的な希釈を起こすことなく、Ge層をアニールすることができるようになる。

(もっと読む)

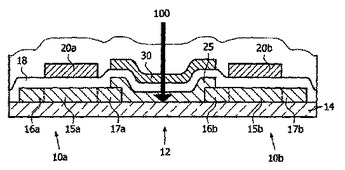

光センサーを備えたアクティブマトリックス型画素デバイス

基板に支持され、ポリシリコンTFT(10)及びアモルファスシリコン薄膜PINダイオード(12)を含む回路を有するアクティブマトリックス型画素デバイス、例えばEL表示装置、が提供される。ポリシリコンアイランドが形成された後に、アモルファスシリコン層がPINダイオード用に堆積されることにより、アモルファスシリコンは高温処理にさらされなくなる。TFTはドープされたソース/ドレイン領域(16a、17a)を有し、その一方(17a)はまた、ダイオードにN型又はP型のドープ領域を提供する。有利なことに、フォトダイオードに別個のドープ領域を設けることが不要になり、処理コストが削減される。反対導電型にドープされたソース/ドレイン領域(16b、17b)を有する第2のTFT(10b)が、ダイオードに他方のドープ領域(16b)を提供し、真性領域(25)が2つのTFT間にそれぞれのポリシリコンアイランドの各々に重なるように横方向に配置される。  (もっと読む)

(もっと読む)

101 - 116 / 116

[ Back to top ]