Fターム[5F049PA14]の内容

受光素子−フォトダイオード・Tr (21,418) | 製造方法(工程) (2,065) | エッチング (375)

Fターム[5F049PA14]に分類される特許

361 - 375 / 375

半導体受光素子およびその製造方法

【課題】 良好な高周波特性を有し、簡単な構成で歩留まりの高い半導体受光素子を構成する。

【解決手段】 Fe−InP基板24上にn−コンタクト層26を選択的に配設し、n−コンタクト層26の上にn−コンタクト層26側から、n−クラッド層28、光吸収層32、およびp−クラッド層36が順次積層された光導波路層16aを配設し、この光導波路層16aの周囲をn−クラッド層28上に配設されたFe−InPのブロック層38により埋め込み、光導波路層16aのp−クラッド層36と電気的に接続されたコンタクト電極18aとこのコンタクト電極18aからブロック層38の側壁上を経由してFe−InP基板24上に延在する引出電極部18bとこの引出電極部18bと接続されFe−InP基板24表面にSiN膜22を介して配設された電極パッド18cとを有するp電極18を備えたものである。

(もっと読む)

固体撮像素子

【課題】良質な光電変換層を有し、画素の高集積化が可能で、感度が高く、高度な色分離ができ、尚且つ偽色や残像が少ない固体撮像素子を提供すること。

【解決手段】Si基板に信号転送回路(図示せず)が形成された信号転送回路基板12(シリコン基板)上に、光電変換部14が設けられた固体撮像素子において、受光面側から、例えば440から480nmにバンドギャップを持つInAlPからなる第1光電変換層18(第1化合物半導体層:InAlP層)、520から580nmにバンドギャップを持つInGaAlPからなる第2光電変換層20(第2化合物半導体層:InGaAlP層)、及び、600nmより長波長側にバンドギャップを持つGaAsからなる第3光電変換層22(第3化合物半導体層:GaAs層)の光電変換層を積層させて、積層型の化合物半導体層からなる光電変換部14を構成する。

(もっと読む)

光学装置及び光学装置の製造方法

【課題】 同一基板上に形成された半導体レーザとフォトダイオード間でのリーク電流の低減を図る。

【解決手段】 {100}結晶面を主面とする同一半導体基板上に、共振器長方向を[0−11]結晶軸方向として半導体レーザLDと、フォトダイオードPDが結晶成長により近接して形成され、フォトダイオードPDが{111}B結晶面の傾斜面を有するように連続的に結晶成長された導電型の異なる第1の半導体層40及び第2の半導体層49からなり、pn接合が前記{111}B結晶面を除く第1の半導体層40の上面のみに形成され、{111}B結晶面が、前記半導体レーザLDからの出射光を反射する反射鏡33となり、半導体レーザLDとフォトダイオードPDとの間に高濃度不純物領域によるリーク電流阻止層48が設けられて成る。

(もっと読む)

格子界面を有する画素セル

画素セルであって、シリコン基板の中のフォトセンサと、前記フォトセンサの上に備えられ且つ前記シリコン基板との格子界面を有する酸化層と、を有する。および格子界面を有する画素セルを製作する方法。  (もっと読む)

(もっと読む)

パッシベーション層を備えた半導体素子および該半導体素子の製造方法

本発明は、AlxGayIn1-x-yAszSb1-zを含有し、ここでパラメータx, y, zは、バンドギャップが350meVよりも小さくなるよう選定されている半導体素子に関する。この場合、半導体素子はメサ形構造を有しており、このメサ形構造の少なくとも1つの側面に、少なくとも部分的にAlnGa1-nAsmSb1-mを含有するパッシベーション層が設けられており、ここでパラメータnは0.4〜1の範囲から選択され、パラメータmは0〜1の範囲から選択される。  (もっと読む)

(もっと読む)

フォトダイオードアレイ及びその製造方法

フォトダイオードアレイは、光の入射面側にpn接合型の複数のフォトダイオードがアレイ状に形成され、入射面の反対面が(100)面からなる半導体基板と、フォトダイオード同士に挟まれた領域に形成され、半導体基板の入射面側から反対面側までを貫通した貫通孔と、入射面から貫通孔の壁面を通じて反対面まで連なる導電体層とを備え、貫通孔は入射面側に入射面に対して略垂直に形成された垂直孔部と反対面側に形成された四角錐形状の孔部とが、半導体基板内部で連結されることによって形成されており、四角錐形状の孔部の壁面が(111)面となっていることを特徴とする。  (もっと読む)

(もっと読む)

集積されたピンダイオードおよび関連の回路構造を製造する方法

特に、埋め込まれた領域(20)と、埋め込まれた領域(20)に通じる端子領域(32)とを含む集積されたピンフォトダイオードを製造する方法に関する説明が与えられる。本発明による製造方法は、1つの伝導型のドーピングされた領域(20)を生成するステップと、基板から遠いドーピングされた領域(42)を生成するステップと、中間領域(30)を生成するステップと、少なくとも1つの導電性端子領域(32)を生成するステップとを含む。本製造方法は、ピンフォトダイオード(14)が単純な方法で集積されることを可能にする。さらに、ピンダイオードを製造するプロセスステップはまた、遮蔽ウェル(22、56)を製造するためにも利用され得る可能性がある。  (もっと読む)

(もっと読む)

半導体光素子とその製造方法

【課題】 有機材料膜のドライエッチング工程において、半導体基板上に残存する反応生成物を容易に除去する。

【解決手段】 有機材料膜のドライエッチング工程において、反応生成物を除去する目的でエッチングガスに添加されているフッ素系ガスのほかに、下部電極またはウェハ搬送用トレー上に設置された半導体基板の周辺に、フッ素を含有した部材を設け、部材自体からプラズマ中にフッ素(フッ素ラジカル)を生成させることで、半導体基板上に堆積した反応生成物を効率的かつ安定的に除去することができ、高品質な半導体光素子を実現できる。

(もっと読む)

光半導体装置およびその製造方法

【課題】同一基板に集積回路、受光素子およびマイクロミラーを搭載する光半導体装置において、受光素子上の反射防止膜の膜厚バラツキにより光電変換効率が低下する問題がある。

【解決手段】同一の半導体基板1に集積回路を構成するトランジスタ2、受光素子3およびマイクロミラー5を搭載する光半導体装置であって、受光素子3上に形成された反射防止膜16と、反射防止膜16上に形成され、反射防止膜16を露出する状態に開口された第1絶縁膜18と、第1絶縁膜18上に形成され、反射防止膜16上の第1絶縁膜18の開口の周辺部およびマイクロミラー5上の周辺部に残存されたエッチングストップ膜19とを有する。この構成によると、所望の膜厚に制御された反射防止膜16が受光素子3上に形成されるので、受光素子3の高感度化が図られる。

(もっと読む)

イメージセンサおよびイメージセンサを製造する方法

背面照射型イメージセンサ(14)の製造方法を開示する。本発明の方法は、第1および第2の表面(3,4)を有するウェハ(2)から出発し、第1表面(3)からウェハ(2)内に延在する感光性ピクセル領域(5)を設けるステップと、第1表面(3)を保護基板(7)に対向させて保護基板上にウェハ(2)を固定するステップとを具える。ウェハは、第1の材料の基板(8)と、光学透明層(9)と、半導体材料の層(10)とを具える。基板(8)を、光学透明層(9)を停止層として用いて、半導体材料の層から選択的に除去する。背面照射型イメージセンサでは、光は半導体層を透過して感光性ピクセル領域(5)に入射しなければならない。吸収損失を低減するために、半導体層(10)を比較的薄く均一に作製できると非常に有利である。半導体層の厚さを減少させると、感光性領域に入射する光が多くなり、このことがイメージセンサの効率改善につながる。 (もっと読む)

非結晶性シリコン垂直カラーフィルター

【課題】イメージセンサーの面積を縮小するとともに微細で簡単なセンサー回路を達成し、製造プロセスが容易な高感度のイメージサンサーを提供する。

【解決手段】半導体集積回路製造プロセスによって、半導体基板上に、少なくとも2つの垂直に積層した感光性センサーを有する垂直カラーフィルターセンサー群を形成する。各々のセンサーは異なるスペクトル応答を持つ。少なくとも1つのセンサーは結晶性シリコン以外の半導体材料、たとえばシリコンカーバイド、InxGa1−xN、III−V族半導体材料、ポリシリコン、またはアモルファスシリコンなどの少なくとも1つの層を含む。本発明の他の特徴は、垂直カラーフィルターセンサー群、およびこのような垂直カラーフィルターセンサー群とそれらのアレイの製造方法である。また少なくとも1つのセンサーは光子吸収領域およびアバランシェ・ゲイン領域を持つ。

(もっと読む)

垂直カラーフィルターセンサー群

【課題】高感度のカラーフィルターセンサーを微細に簡便なプロセスで製造すること。

【解決手段】半導体基板上に少なくとも2つの垂直に積層した感光性センサーを含む垂直カラーフィルターセンサー群を形成する。センサー群は、フィルターを通して又はフィルターから反射した放射線が少なくとも1つのセンサーへ伝播するようにセンサーに対して配置した少なくとも1つのフィルターを含む。フィルターは半導体集積回路製造プロセスによってセンサーで集積化された層を含む。また、センサー群はマイクロレンズを含む。本発明の他の観点は、垂直カラーフィルターセンサー群のアレイであり、それらの1部又はすべては少なくとも1つのフィルターまたはマイクロレンズ、および垂直カラーフィルターセンサー群とそれらのアレイの製造方法を含む。さらにセンサー群を集積化したウエハ同士の結合構造も含む。

(もっと読む)

半導体受光素子

半導体受光素子(アバランシェ・フォトダイオード)において、高性能な増倍特性を持つ増倍層を組み込んで、高感度な素子を得る。エッチングストッパー層にかかる電界を低減する構造を用いることで、より高性能な増倍特性を持つ増倍層(高い電界で増倍する増倍層)を利用できる。これを実現する第一の方法は、導電型の増倍層を用いることである。第2の方法は、第2の導電型の電界緩和層を組み込んだ構造とすることである。これらにより、増倍電界より低い電界をエッチングストッパー層に印加するような構造とする。 (もっと読む)

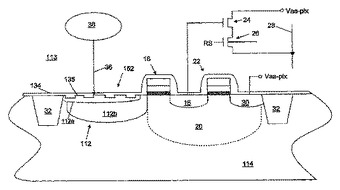

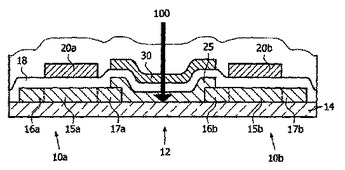

光センサーを備えたアクティブマトリックス型画素デバイス

基板に支持され、ポリシリコンTFT(10)及びアモルファスシリコン薄膜PINダイオード(12)を含む回路を有するアクティブマトリックス型画素デバイス、例えばEL表示装置、が提供される。ポリシリコンアイランドが形成された後に、アモルファスシリコン層がPINダイオード用に堆積されることにより、アモルファスシリコンは高温処理にさらされなくなる。TFTはドープされたソース/ドレイン領域(16a、17a)を有し、その一方(17a)はまた、ダイオードにN型又はP型のドープ領域を提供する。有利なことに、フォトダイオードに別個のドープ領域を設けることが不要になり、処理コストが削減される。反対導電型にドープされたソース/ドレイン領域(16b、17b)を有する第2のTFT(10b)が、ダイオードに他方のドープ領域(16b)を提供し、真性領域(25)が2つのTFT間にそれぞれのポリシリコンアイランドの各々に重なるように横方向に配置される。  (もっと読む)

(もっと読む)

埋込式導波路検出器

以下の段階が含まれる、検出器の作製方法である。上面を有する基板中にトレンチを形成する段階と;前記基板上及び前記トレンチ中に、第1ドープ半導体層を形成する段階と;前記第1ドープ半導体層上及び前記トレンチ中に延在して、第1ドープ半導体層の伝導度よりも低い伝導度を有する第2ドープ半導体層を形成する段階と;前記第2ドープ半導体層上及び前記トレンチ中に延在する第3ドープ半導体層を形成する段階と;前記第1、第2及び第3ドープ半導体層における、上面、実質的な平面を作製して前記トレンチ中の第1ドープ半導体層の上端を露出させるために、前記基板の表面で画定される平面よりも上方の部分を除去する段階と;前記第1ドープ半導体層への第1電気的コンタクトを形成する段階と;前記第3ドープ半導体層への第2電気的コンタクトを形成する段階と、を有する。

(もっと読む)

(もっと読む)

361 - 375 / 375

[ Back to top ]