Fターム[5F058BF38]の内容

Fターム[5F058BF38]の下位に属するFターム

Fターム[5F058BF38]に分類される特許

61 - 80 / 81

プラズマCVD成膜方法及びプラズマCVD成膜装置

【課題】N−H結合含有量の少ないプラズマCVD成膜方法を提供する。

【解決手段】真空雰囲気下で、ヘキサメチルジシラザンガスとアンモニアガスとアルゴンガスとをチャンバ12内に供給し、ウェハW表面にSiCN系膜の厚さ1〜10nm程度の薄膜を形成する。次いで、アルゴンガスを供給した状態で、さらに減圧し、ウェハWを加熱する。このアニール処理により、薄膜中のN−H結合が励起され、解離によりHが膜中から除去される。この薄膜形成処理と、アニール処理と、を繰り返し、所定厚さのSiCN系膜を成膜する。

(もっと読む)

成膜方法、成膜装置及び記憶媒体

【課題】比較的低温で成膜しても含有する炭素濃度を多くさせてクリーニング時のエッチングレートを比較的小さくできる絶縁膜を形成することができる成膜方法を提供する。

【解決手段】被処理体Wが収容されて真空引き可能になされた処理容器4内に、シラン系ガスと窒化ガスと炭化水素ガスとを供給して被処理体の表面にSiCN膜を形成する成膜方法において、シラン系ガスを供給する工程と炭化水素ガスを供給する工程とを少なくとも間欠的に交互に行う1サイクルを複数回繰り返して実行すると共に窒化ガスを供給する工程を適宜に行い、炭化水素ガスの供給工程の全部の期間、或いは一部の期間で炭化水素ガスをプラズマによって活性化するプラズマ活性化処理を行う。これにより、比較的低温で成膜しても含有する炭素濃度を多くさせてクリーニング時のエッチングレートを比較的小さくできる。

(もっと読む)

O3−TEOS酸化膜蒸着方法及び蒸着装置

【課題】O3−TEOS酸化膜の蒸着方法及びO3−TEOS酸化膜を含む所定の物質膜を蒸着するための蒸着装置を提供する。

【解決手段】O3−TEOS膜蒸着方法は、下部膜質依存性がある下部膜315上に、下部膜質依存性がなくなる高温下で第1のO3−TEOS酸化膜321を蒸着する段階と、第1のO3−TEOS酸化膜321上に蒸着速度が速い低温下で第2のO3−TEOS酸化膜323を蒸着する段階とを含む。したがって、O3−TEOS膜を高温及び低温の2段階の温度条件下で蒸着することにより、生産性が低下しない下部膜質依存性が除去されたO3−TEOSを得ることができる。さらに、単一の装置内に2以上のサセプタまたはヒーターを具備することにより、同一の装置内において相異なる温度にて所定の物質膜を蒸着することができる。

(もっと読む)

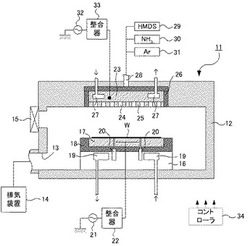

薄膜成膜装置

【課題】絶縁耐圧が良好であると同時に、隣接する半導体能動膜の所望のキャリア移動度を確保し得るゲート絶縁膜を有するTFTの製造方法に用いることができる薄膜成膜装置を提供する。

【解決手段】内部を真空雰囲気に維持することが可能な成膜チャンバー35と、プラズマを発生させるための高周波電界を生成する高周波電極32およびサセプタ電極34と、所定の周波数の高周波電力を供給するプラズマ励起電源31およびバイアス電源33と、図示されない加熱手段と、成膜チャンバー35内部にガス導入管36を介して所望のガスを供給するガス供給手段37と、成膜チャンバー35内を所望の圧力とするよう排気を行うガス排気手段38と、各部を制御する制御部39とを有する構成となっている。

(もっと読む)

半導体装置の製造方法

【課題】MOS界面の界面準位とバルクのゲート酸化膜中の欠陥とを共に提言し良質なゲート絶縁膜を得る。

【解決手段】基板1上に半導体層2を形成した後、プラズマCVD法によって第1のゲート酸化膜3を薄く生成する。次に、第1のゲート酸化膜3を形成したときよりも基板温度をより高くした状態で、第1のゲート酸化膜3の上に第2のゲート酸化膜4を形成する。基板温度が比較的低い状態で生成した第1のゲート酸化膜は、MOS界面の界面準位がより低減されており、基板温度が比較的高い状態で生成した第2のゲート酸化膜は、その酸化膜中の欠陥が低減されているから、結果的に、第1及び第2のゲート酸化膜3及び4からなるゲート酸化膜は、MOS界面の界面準位が低減され、且つゲート酸化膜中の欠陥が低減されたゲート酸化膜となり、良質なゲート酸化膜を形成することができる。

(もっと読む)

熱処理装置及び熱処理方法

【課題】縦型熱処理装置において処理ガスを適切な温度に調整して基板に供給し、良好な処理を行う。

【解決手段】その長さ方向に多数のガス供給孔が形成されたガス供給ノズルを、反応容器内にウエハボートに沿って起立するようにを設ける。ガス供給ノズルは例えば石英製の内管及び外管を含む二重管を備え、内管と外管との間が処理ガスの供給路として構成され、内管の中に熱処理炉のヒータとは独立して温度制御できる予備加熱ヒータが設けられる。例えばオゾンガスを供給する場合、予備加熱ヒータの温度を調整しておくことで、基板の表面に到達したときに活性種が形成されるようになる。

(もっと読む)

誘電膜及びその形成方法並びに誘電膜を備えた半導体メモリ素子及びその製造方法

【課題】静電容量を確保し、且つ漏れ電流特性を改善することができる誘電膜及びその形成方法並びに半導体メモリ素子及びその製造方法を提供すること。

【解決手段】誘電膜(50)は、少なくとも25の比誘電率を有する第1誘電膜(10)と、第1誘電膜(10)よりも結晶化率が低い物質を用いて第1誘電膜(10)の上に形成された第2誘電膜(20)と、第1誘電膜(10)と同じ物質を用いて第2誘電膜(20)の上に形成された第3誘電膜(30)とを備えており、半導体メモリ素子は、下部電極が形成された基板と、下部電極の上に形成された誘電膜(50)と、誘電膜(50)の上に形成された上部電極とを備える。

(もっと読む)

キャパシタおよびその製造方法、強誘電体メモリ装置の製造方法、アクチュエータの製造方法、並びに、液体噴射ヘッドの製造方法

【課題】 誘電体膜へのダメージを低減させることができるキャパシタの製造方法を提供する。

【解決手段】 本発明に係るキャパシタ10の製造方法は、

基板1の上方に下部電極4を形成する工程と、

下部電極4の上方に、強誘電体または圧電体からなる誘電体膜5を形成する工程と、

誘電体膜5の上方に上部電極6を形成する工程と、

少なくとも誘電体膜5を被覆するように酸化シリコン膜20を形成する工程と、を含み、

酸化シリコン膜20は、トリメトキシシランを用いて形成される。

(もっと読む)

半導体素子のトレンチ素子分離領域製造方法

【課題】本発明は、ギャップ充填特性に優れながら欠陥が発生しない半導体素子のトレンチ素子分離方法を提供する。

【解決手段】トレンチが形成された基板を高密度プラズマ化学気相蒸着装置にローディングする段階、基板を第1昇温する段階、装置に第1のバイアスパワーを印加してトレンチの内壁と底面に高密度プラズマ酸化膜ライナーを形成する段階、第1のバイアスパワーをオフし、基板を第2昇温する段階、第1のバイアスパワーより大きい第2のバイアスパワーを印加してトレンチ内部のギャップを充填する高密度プラズマ酸化膜を形成する段階、及び基板を装置からアンローディングする段階を含む。これにより、優秀なギャップ充填特性を確保でき、側壁酸化膜とライナーの分離及びバブル欠陥が発生せず、単純化された工程でSTIを完成できる。

(もっと読む)

成膜方法及び成膜装置

【課題】 カバレッジ性が良好であり、フッ素を含む薬液に対する耐性が大きいシリコン酸化膜を低い成膜温度で形成すること。

【解決手段】 処理容器内に被処理体を載置し、この処理容器内にTEOSガスと酸素ガスと水素ガスとを導入し、前記処理容器内を減圧雰囲気下でTEOSガスの分解温度よりも低い温度で加熱することにより、前記被処理体の上にシリコン酸化膜を形成する。TEOSガスは気相中での分解が抑えられ、被処理体の上に吸着する。一方水素ガスと酸素ガスとは、被処理体の上で水酸基活性種と酸素活性種とを生成し、これら活性種により被処理体に吸着されたTEOSが分解されて、こうして被処理体の上にシリコン酸化膜が形成される。

(もっと読む)

プラズマ成膜方法及び成膜構造

【課題】 基板上の成膜時間を短くするとともに、デバイスの特性低下を抑制すること。

【解決手段】 真空容器1内に高周波による電磁波を形成し、電磁波によって原料ガスのプラズマを発生させて、基板5上の成膜対象面に成膜を行なうプラズマ成膜方法において、電磁波をパルス状に形成するとともに、変調器16を用いて電極3のパルスの単位時間当たりのオン時間を膜厚方向で変更させるようにする。これにより、成膜によって形成される層間の界面を良好に保ち、デバイス特性の低下を抑制することができる。また、オン時間を適宜長くすることで、成膜時間を短縮することができる。

(もっと読む)

半導体のための引張り及び圧縮応力をもたせた物質

応力をもたせた膜が基板上に形成される。基板が処理ゾーンに置かれ、処理ゾーンに与えられたシリコン含有ガス及び窒素含有ガスを有する処理ガスのプラズマが形成される。窒素の如き希釈ガスを加えることもできる。堆積直後のままの応力をもたせた物質を、紫外線又は電子ビームに対して露出させることにより、その堆積物質の応力値を増大させることができる。それに加えて、又はそれとは別に、堆積中にその物質の応力値を増大させるために、窒素プラズマ処理を使用することができる。応力をもたせた物質を堆積させるためのパルス化方法も開示する。 (もっと読む)

半導体ウエハの処理方法及びシステム並びに半導体デバイスの製造方法

【課題】皮膜の品質を向上させた薄いゲート酸化皮膜のような絶縁皮膜或いは酸化皮膜が形成可能な半導体ウエハの処理方法を提供する。

【解決手段】酸化皮膜をプロセスチャンバ204内にて形成するために、ウエハ210を加熱するための熱源214に加えて、光源216により紫外線光等のような光のエネルギをウエハ210に照射することにより、皮膜の品質を向上させる。

(もっと読む)

銅相互接続配線およびこれを形成する方法

集積回路のための相互接続構造体における使用のための銅相互接続配線層(602)の表面上のキャッピング層(614)およびガスクラスタイオンビーム処理の適用による集積回路のための改良された集積相互接続構造体を形成する方法。低減された銅拡散と改善されたエレクトロマイグレーション寿命が結果として得られ、また選択的金属キャッピング技法の使用とそれらに付随する歩留まり問題とが回避される。 (もっと読む)

有機金属化学的気相成長法によるグレーディングPrxCa1−xMnO3薄膜の堆積方法

【課題】 適切な記憶装置動作のために膜厚を通して種々の構成でメモリ抵抗素子を製造可能なグレーディングPCMO薄膜の堆積方法を提供する。

【解決手段】 PCMO膜中に含まれるCa、Mn、及び、Prが、そのスイッチング特性において大きく影響するため、RRAM記憶装置に使用するためのグレーディングPCMO薄膜を実現させる方法として、堆積温度、気化温度のような堆積パラメータに関して、異なった堆積速度の作用を有するPr、Ca及びMnの前駆体を選択することによって、堆積処理中の個々の堆積パラメータを変化させることで、Pr、CaまたはMnの配分が傾斜したグレーディングPCMO薄膜を堆積する。

(もっと読む)

フッ素ドープ低誘電率絶縁膜を形成する方法

【課題】低誘電率及び高熱安定性を有するフッ素ドープ低誘電率シリコン酸化膜を形成する方法を与える。

【解決手段】容量結合プラズマCVDにより、低誘電率シリコン酸化膜を形成する方法は、シリコンソースガスとしてSiH4、フッ素ソースガスとしてSiF4、及び酸素ソースガスとしてCO2から成る処理ガスを、(SiH4+SiF4)/CO2が約0.02から約0.2の範囲となるような流量比で、かつ、全圧が約250Paから約350Paとなるように反応チャンバへ導入する工程と、約10MHzから約30MHzの周波数の第1RF電力及び約400kHzから約500kHzの周波数の第2RF電力を印加する工程であって、2つのRF電力を重畳させることにより、反応チャンバ内部にプラズマ反応場を生成するところの工程と、それぞれのガスの流量及びそれぞれのRF電力出力を制御する工程と、から成る。

(もっと読む)

ネガティブ・スパッタ・イオン・ビーム源を使用して酸化物薄膜を形成する方法

処理チャンバ内の基板に対面するスパッタ・ターゲットの表面上に仕事関数還元剤を導入し、酸素ガスとインサート・ガスとを処理チャンバ内に供給し、酸素ガスと不活性ガスとをイオン化することによって複数の電子を生成し、スパッタ・ターゲットから複数の陰荷電イオンを解離させ、イオン化された酸素ガスで反応した陰荷電イオンから酸化物薄膜を基板上に形成する、酸化物薄膜の形成方法。本発明は、広い範囲での応用に適しているが、特に、高充填密度、高屈折率、低応力性、低表面粗度に関して、望ましい特質を持った酸化物薄膜を形成するのに適している。 (もっと読む)

窒化珪素膜の製造方法及び半導体装置の製造方法

【課題】 窒化珪素膜の塩素不純物量の低減を実現し、ウェットエッチ耐性の高い窒化珪素膜の形成を可能とした窒化珪素膜の製造方法及びこの製造方法を備えた半導体装置の製造方法を提供することを目的とする。

【解決手段】 基体の表面に窒化珪素膜を形成する窒化珪素膜の製造方法であって、珪素と塩素とを含む第1のガスを前記基体の表面に供給する第1の工程と、窒素を含む第2のガスを前記基体の表面に供給する第2の工程と、水素を含む第3のガスを前記基体の表面に供給する第3の工程と、をこの順に繰り返すことを特徴とする窒化珪素膜の製造方法を提供する。

(もっと読む)

半導体素子のパッシベーション膜形成方法及び半導体素子のパッシベーション膜構造

【課題】 本発明は、選択ソースラインと共通ソースライン間の漏れ電流を著しく減少させることが可能な半導体素子のパッシベーション膜形成方法及び半導体素子のパッシベーション膜構造を提供することを目的としている。

【解決手段】 半導体基板上に金属配線を形成する段階と、前記金属配線上にプラズマによる損傷を緩衝することが可能な第1パッシベーション膜のバッファ酸化膜を形成する段階と、前記バッファ酸化膜上に第2パッシベーション膜の高密度プラズマ(HDP)膜を形成する段階と、前記第2パッシベーション膜上に第3パッシベーション膜を形成する段階とを含んで半導体素子のパッシベーション膜を形成する構成としたことを特徴とする。

(もっと読む)

窒化ケイ素の熱化学気相堆積

処理領域と、基板支持体と、ガス分配システムと、ガス混合領域と、フェースプレートに固定されたアダプタリングを所望の温度に加熱するように配置された加熱素子と、温度制御排気システムとを備えた装置。また、ビス(第三級ブチルアミノ)シランを蒸発させ、ビス(第三級ブチルアミノ)シランとアンモニアを処理チャンバへ流し、アダプタリングと少なくとも2つのブロッカープレーで画成された追加の混合領域を有する2つの反応種を合わせ、アダプタリングを加熱し、ビス(第三級ブチルアミノ)シランをガス分配プレートを通って処理領域に流す方法と装置。 (もっと読む)

61 - 80 / 81

[ Back to top ]