Fターム[5F064BB22]の内容

ICの設計・製造(配線設計等) (42,086) | ICの機能 (7,082) | アナログ信号処理 (1,283) | 増幅器、アンプ (207)

Fターム[5F064BB22]の下位に属するFターム

センスアンプ (95)

演算増幅器、オペアンプ (54)

Fターム[5F064BB22]に分類される特許

1 - 20 / 58

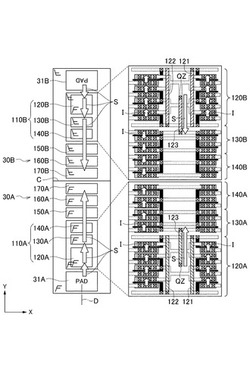

半導体装置

【課題】複数の回路ブロックの特性を正確に一致させる。

【解決手段】例えば、端子31A,31Bと、これら端子間に設けられた回路110A,110Bを備える。回路110Aは端子31Aに接続され、端子31Aから端子31Bへ向かって配置されたセル120A,130A,140Aを含む。回路110Bは端子31Bに接続され、端子31Bから端子31Aへ向かって配置されたセル120B,130B,140Bを含む。セル120A,120Bのレイアウトは、形状、サイズ及び向きがトランジスタレベルで同一である。セル130A,130B及びセル140A,140Bのレイアウトは、形状及びサイズが同一であり、トランジスタの向きが180°相違している。これにより各セルを対称配置しつつ、センシティブなセル120A,120Bにおいては電流方向の違いによる特性差が生じない。

(もっと読む)

半導体集積回路の設計方法

【課題】アナログ回路動作で発生するトランジスタ劣化による特性変動を正確に予測できるようにする。

【解決手段】半導体集積回路に含まれるトランジスタを抽出した後、抽出されたトランジスタのゲート絶縁膜に印加される電界強度の大きさに基づいて、当該トランジスタに適用するストレスバイアス条件を分類する。次に、前記ストレスバイアス条件の分類に応じて、前記トランジスタの劣化後の特性を求めた後、当該劣化後のトランジスタ特性を用いて、前記半導体集積回路の回路シミュレーションを行う。

(もっと読む)

半導体集積装置

【課題】SiPのチップ間を接続するための端子数が増加する。

【解決手段】パッケージ内部に第1の半導体チップと第2の半導体チップが集積される半導体集積回路であって、前記第1の半導体チップは、第1の通信部と、複数のアナログ回路とを備え、前記第2の半導体チップは、第2の通信部と、前記複数のアナログ回路の特性調整用データを格納するメモリ部とを備え、前記第1の通信部と前記第2の通信部とがシリアルデータ通信線で接続され、前記シリアルデータ線を経由して前記第1の半導体チップが備える複数のアナログ回路の特性調整用データをそれぞれ複数のアナログ回路に転送する半導体集積回路。

(もっと読む)

半導体電力増幅器

【課題】ビアホールの数を少なくしてもループ発振などの特性劣化が生じにくい半導体電力増幅器を提供する。

【解決手段】半導体電力増幅器は、ゲート電極Gと、ドレイン電極Dと、前記ゲートフィンガー電極に対向して配置されるソースフィンガー電極横手方向の両サイドに引き出される2つのソース電極Sと、を有するユニットFETと、前記ユニットFETが、前記ソース電極間を結ぶ略直線方向に複数個並列配置され、隣り合うユニットFET間に存在する2つのソース電極の両方を共通して高周波グランド面と接続する第1の接地インダクタンス値を有する第1のビアホール18Kと、隣り合うユニットFETが存在しない側のソース電極上に配置され、接地インダクタンスを等しくするために前記高周波グランド面に接続する第2の接地インダクタンス値を有する第2のビアホール18Dと、を有する。

(もっと読む)

半導体装置

【課題】隣接する2つのトランジスタ同士が接続された構成を有し、省スペースと電流集中による信頼性の低下の抑制とを両立させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタ101と接続された第1のバス111、第2のトランジスタ102と接続された第2のバス112と、第1のバス111と第2のバス112との間に形成され、第1のバス111と第2のバス112とを接続するバス間配線121とを備えている。バス間配線121は、第1のバス111における第2のバス112と対向する辺の一部及び第2のバス112における第1のバス111と対向する辺の一部と接続されている。第1のコンタクトパッド131は、第1のバス111の一部と接続され、第2のコンタクトパッド132は、第2のバス112の一部と接続されている。

(もっと読む)

貫通電極を有する積層構造の半導体装置、半導体メモリ装置、半導体メモリ・システム及びその動作方法

【課題】貫通電極を有する積層構造の半導体装置、半導体メモリ装置、半導体メモリ・システム及びその動作方法を提供する。

【解決手段】複数の半導体レイヤ間で伝送される情報の衝突を防止する構造を有する半導体装置であり、該半導体装置は、第1温度情報を出力する第1温度センサ回路を含む少なくとも1つの第1半導体チップと、貫通電極に電気的に連結されずに、第1温度センサ回路に電気的に連結される第1バンプと、第1半導体チップの貫通電極に電気的に連結される第2バンプと、を具備する半導体装置であることを特徴とする。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】良好な伝送性能と小さい配置面積を両立可能なデータバスを備える半導体装置を提供する。

【解決手段】本発明の半導体装置は、配線層M1、M2と、複数のデータ入出力端子と、N本のデータ線(DU、DL)を含むデータバスとを備え、N本のデータ線は所定の配線長の長短に応じた2種類のデータ線群を含む。配線層M1、M2にはデータ線(DL、DU)の各々に隣接する複数のシールド線(Sa、Sb、Sc)が配置され、各データ線(DL、DU)は、配線層M1、M2の積層方向で互いに重ならない位置に配置される。このような配線構造により、各データ線(DL、DU)の間のカップリング容量を抑え、データバスのクロストークを防止することができる。

(もっと読む)

半導体集積回路のノイズ耐性評価方法およびノイズ耐性評価装置

【課題】大規模な半導体集積回路であってもノイズ耐性評価が短時間で可能なノイズ耐性評価方法を提供する。

【解決手段】回路ネットリストを作成する第1のステップS11と、能動素子を受動素子回路に置き換えて置換回路ネットリストを作成する第2のステップS12と、トランジスタの制御端子に該当する制御ノードを抽出する第3のステップS13と、ノイズ注入ノードを設定する第4のステップS14と、所定周波数のノイズを設定し、互いに異なる制御ノードとノイズ注入ノード間の経路のインピーダンスを計算する第5のステップS15と、制御ノード、ノイズ注入ノードおよび経路の各組み合わせにおけるインピーダンスのリストを作成する第6のステップS16と、インピーダンスの最小値から半導体集積回路のノイズ耐性を判定する第7のステップS17とを有してなるノイズ耐性評価方法100とする。

(もっと読む)

クロック分配回路及びその回路を含む半導体回路装置

【課題】

半導体チップを製造する際の製造バラツキ又は半導体チップ内の半導体回路の動作条件による、複数の最終バッファから出力される複数のクロック間の位相差を軽減することが可能なクロック分配回路を提供することを目的とする。

【解決手段】

回路装置内に配置されたクロック分配回路であって、リング状のクロック配線と、前記クロック配線に接続し、自己発振により、前記クロック配線内に第1クロック信号を発生させる発振回路と、前記回路装置内において、2以上の場所それぞれに、配置され、第2クロック信号を出力する2以上の位相調整回路と、を備え、前記位相調整回路それぞれは、配置場所に応じた位相を有する前記第1クロック信号を受け取り、前記位相調整回路それぞれが受け取った前記第1クロック信号間の位相差よりも、前記位相調整回路それぞれが出力する前記第2クロック信号間の位相差を減じる調整を行うことを特徴とするクロック分配回路。

(もっと読む)

半導体集積回路装置

【課題】制御信号の系統を整理して、不定信号伝播防止回路等の検討漏れの危険性を回避し、さらに、自動化ツールへの搭載へ向けた検討を容易にし、また、チップ内部での電源遮断制御を容易化することができる半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置において、各独立した電源領域AreaA〜AreaIごとに電源遮断の優先順を設け、優先順の高い回路がONしている場合にはそれより優先順の低い電源領域はOFFにできないという規則を設けて、設計方法の容易化を図る。また、各独立した電源領域AreaA〜AreaI内において、さらに別の電源を印加できる領域を設け、その領域に中継バッファ(リピータ)やクロックバッファ、情報退避用の情報保持ラッチを集積する。レイアウト上は、電源線の電流を分散させる目的でセルがロウ方向に並ぶ方向と垂直な方向にまとめてレイアウトすればよい。

(もっと読む)

半導体装置

【課題】MISFETにおけるAvt(Vtばらつき)のゲート幅依存性を考慮し、Vtミスマッチ及びVtばらつきを低減できるようにする。

【解決手段】半導体装置は、それぞれが半導体基板に形成され、ソースドレインを構成する拡散層205及び該拡散層205の上に形成されたゲート203を有し、且つ互いに並列接続された複数の単位MISFETから構成される複数のMISFET201、202を含む。MISFET201、202同士の間の閾値電圧のばらつきの標準偏差は、各MISFETにおける単位MISFETのそれぞれのゲート長とゲート幅との積の総和であるチャネル面積と同一の面積を有する単一のMISFET同士の間の閾値電圧のばらつきの標準偏差よりも小さい。

(もっと読む)

プログラマブル論理集積回路

【課題】 異なったLVTTL I/O規格に対して互換性を持つように集積回路の各I/Oを個別に再構成する回路を提供する。

【解決手段】 上述課題は1つのI/O電源電圧のみを用いて達成でき、この電圧は特定の用途に要求されるI/O電圧のうち最も高いものである。回路はI/Oセルの出力電圧を、適合されるべきLVTTL規格のVOHよりも高く最高VIHよりも低くなるように調節することによって動作する。I/Oセルは、I/O電源電圧とパッドの間に接続されるプルアップトランジスタと、該パッドの電圧と対応の規格に応じた基準電圧とを差動増幅する差動増幅器と、差動増幅器の出力信号と出力制御信号とにプルアップトランジスタを選択的にオン状態とするロジックゲートを備える。各I/Oセルは別個に再構成可能であるため、任意のI/Oを任意のLVTTL仕様に適合させることができる。

(もっと読む)

半導体集積回路

【課題】少なくともロジック回路ブロックを含む半導体集積回路において、半導体集積回路の電源用パッドとロジック回路ブロックの電源ラインとを接続する電源配線、及び/又は、半導体集積回路のグランド用パッドとロジック回路ブロックのグランドラインとを接続するグランド配線の抵抗値を下げる。

【解決手段】この半導体集積回路は、半導体基板と、半導体基板上にそれぞれの層間絶縁膜を介して形成され、半導体基板に形成された複数のトランジスタに接続されて複数のトランジスタと共に少なくともロジック回路ブロックを構成する複数の配線層と、複数の配線層が形成された半導体基板上に層間絶縁膜を介して形成され、複数の配線層における最大膜厚の5倍〜20倍の膜厚を有する最上層の配線層とを具備する。

(もっと読む)

プログラマブルロジックデバイスおよびそれを用いた電子機器

【課題】複数の機能を短時間で切りかえ可能なPLDを提供する。

【解決手段】PLD100は、n(nは2以上の整数)個のコンテキストを切りかえ可能である。マルチコンテキストメモリ20は、n個のコンテキストを定義するn個のコンフィギュレーションデータCONF1〜CONFnを不揮発的に記憶する。(m×n)個のメモリセルMはそれぞれが対応する制御ラインCLおよび対応するビットラインBLに割り当てられている。メモリセルMは、対応する制御ラインCLが選択されたとき、対応するビットラインBLを介してアクセス可能となる。m個のセンスアンプは、対応するビットラインBLに生ずる信号を、リコンフィギュアラブル回路10に出力する。

(もっと読む)

PLD回路、集積回路装置及び電子機器

【課題】消費電力を低減できるPLD回路、集積回路装置及び電子機器等を提供すること。

【解決手段】PLD回路は、各トランジスター列が直列接続されたプログラマブルな複数のトランジスターを有する第1〜第m(mは2以上の整数)のトランジスター列TA1〜TAmを含む。第1〜第mのトランジスター列TA1〜TAmの一端に第1の非直流電源VS1が供給される。第1〜第mのトランジスター列TA1〜TAmの各トランジスター列は、複数の入力信号XP(X1P〜XiP)、XN(X1N〜XiN)によってオン・オフされる。第1の非直流電源VS1の電圧により規定される第1のホールド期間に、第1〜第mのトランジスター列TA1〜TAmの他端のノードである第1〜第mのノードNA1〜NAmの電圧レベルを各々出力する。

(もっと読む)

半導体装置及び半導体装置のレイアウト設計方法

【課題】アナログ回路に利用される抵抗素子の配置領域面積を低減し、抵抗素子の相対精度を向上させる半導体装置及び半導体装置のレイアウト設計方法を提供する。

【解決手段】一の方向に並列配置されたトランジスタ素子(トランジスタ素子Q1及びトランジスタ素子Q2)と、トランジスタ素子上に層間絶縁膜(層間絶縁膜14)を介して形成された抵抗素子(抵抗素子R1及び抵抗素子R2)を有し、平面視において抵抗素子の長さ方向はトランジスタ素子のチャネル幅方向に直交する。

(もっと読む)

無線集積回路装置の製造方法、無線集積回路装置及び電子機器

【課題】効率的な動作試験ができる無線集積回路装置の製造方法、無線集積回路装置及び電子機器等を提供すること。

【解決手段】無線集積回路装置の製造方法は、ウェハー上に複数の無線集積回路装置100を形成し、複数の無線集積回路装置100のうちの少なくとも1つの無線集積回路装置を送信モード無線集積回路装置100aに設定し、複数の無線集積回路装置100のうちの送信モード無線集積回路装置100aを除く少なくとも1つの無線集積回路装置を受信モード無線集積回路装置100bに設定する。送信モード無線集積回路装置100aの送信回路により動作試験用の送信データを送信し、受信モード無線集積回路装置100bの受信回路により動作試験用の送信データを受信して動作試験を実行する。動作試験の完了後に複数の無線集積回路装置100をダイシングする。

(もっと読む)

集積回路装置及び電子機器

【課題】アナログ処理の特性の向上を図れる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、信号が入力されるパッドPANTと、パッドPANTを介して入力される信号についてのアナログ処理を行うアナログ回路と、アナログ回路の信号入力ノードとパッドPANTとの間に設けられるキャパシターCAを含む。パッドPANTとキャパシターCAの一端とが、最上層金属層ALEで形成されるパッド配線LNPにより接続される。

(もっと読む)

スパイラルコイルの配線構造および集積回路装置

【課題】 第1インダクターおよび第2インダクターを有する3ポートのスパイラルコイルにおける特性の対称性を確保し、かつ、3つのポートを、スパイラルコイルの中心を通る直線を基準として同じ側に配置すること。

【解決手段】 第1ポートと第3ポートとの間に設けられる第1インダクターと、第2ポートと前記第3ポートとの間に設けられる第2インダクターとを含むスパイラルコイルの配線構造であって、スパイラルコイルの中心を通る直線を基準として、前記第1ポートおよび第2ポートは同じ側に配置され、第1ポートから引き出される第1配線と、第2ポートから引き出される第2配線とが、スパイラルコイルの中心を通る直線を基準として、第1ポートおよび第2ポートの側において交差することによって第1交差部が設けられる。

(もっと読む)

ばらつき分布シミュレーション装置及び方法

【課題】プロセス変動が回路特性に及ぼす影響を予測可能とするシミュレーション方法を提供する。

【解決手段】MOSFETを有する半導体回路のばらつき解析用に、MOSFETのSPICEパラメータの設定値を算出する回路シミュレーション装置であって、当該回路シミュレーション装置は、MOSFETのばらつき特性に影響を及ぼす変数として、MOSFETの製造条件又は素子構造に関する変数を含み、当該変数により定義される物理量とSPICEパラメータとの間に物理的な相関を有する普遍的関数により構成された中間モデル式を記憶する記憶部101と、この中間モデル式に含まれる変数に関する情報を設定するための設定部102と、設定部に設定された情報と、記憶部に記憶された中間モデル式とに基づいて、SPICEパラメータの設定値を算出する算出部103と、上記半導体回路のプロセス変動依存性を出力する出力部104とを備える。

(もっと読む)

1 - 20 / 58

[ Back to top ]