Fターム[5F064DD10]の内容

ICの設計・製造(配線設計等) (42,086) | ICの構造(配線を除く) (6,653) | 素子、セル、ブロック等の配置、レイアウト (5,076) | 素子、セル、ブロックの形状 (355)

Fターム[5F064DD10]に分類される特許

1 - 20 / 355

スタンダードセル、および、半導体集積回路

半導体集積回路、半導体集積回路の設計方法及び設計装置並びにプログラム

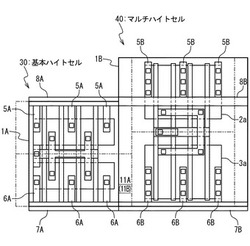

【課題】セルベースの半導体集積回路において、異なるセル高さを有するセルを効率良く配置するための技術を提供する。

【解決手段】半導体集積回路が、基準ハイトセル30、マルチハイトセル40、VDD電源配線、VSS電源配線を備え、マルチハイトセルは、Y軸方向に延伸するVDD側電源供給配線5B、VSS側電源供給配線6Bを備え、基準ハイトセルの高さをa、マルチハイトセルの高さをb、VDD、VSS電源配線の幅をwとしたときに、VSS側電源供給配線は、少なくとも、マルチハイトセルの下端からw/2高さ方向に離れた位置とマルチハイトセルの下端からb−a−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられ、VDD側電源供給配線は、少なくとも、マルチハイトセルの下端からa+w/2高さ方向に離れた位置とマルチハイトセルの下端からb−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられる。

(もっと読む)

局所優先方向アーキテクチャ、ツール、及び機器

【課題】「局所優先方向」配線モデルを使用してネットをルーティングするための機器を提供する。

【解決手段】本発明の一部の実施形態は、1つ又はそれよりも多くのEDAツール(プレーシング、ルーティングなどのような)と共に使用される「局所優先方向(LPD)」配線モデルを提供する。LPD配線モデルは、少なくとも1つの配線層が、各々が特定の配線層とは異なる優先方向を有する一組の領域を有することを可能にするものである。更に、各領域は、その組における少なくとも1つの他の領域の局所優先方向とは異なる局所優先方向を有する。更に、少なくとも2つの領域は、2つの異なる多角形形状を有し、その組における領域は、その組における別の領域を取り囲むことはない。

(もっと読む)

LSIのレイアウトパターン表示装置および表示方法

【課題】レイアウトパターン上で、直観的に回路素子を認識可能とし、回路素子間の信号の流れの把握を容易にする。

【解決手段】レイアウトパターン表示部400により、格納部200,300内に格納されているブロック/セルという階層構造をもったデータを展開して、画面上にレイアウトパターンを表示する。条件設定部800には、セル枠決定に用いる特定のレイヤーを示す情報がセル枠決定条件として設定されており、セル枠決定部600は、個々のセルについて、当該特定のレイヤーに収録されている図形を抽出し、抽出した図形の論理和図形を形成し、この論理和図形の外接矩形をセル枠として求める。端子図形生成部500は、求めたセル枠とセル間配線との交差位置に端子図形を生成する。レイアウトパターン表示部400は、セル枠と端子図形をレイアウトパターン上に重畳表示する。

(もっと読む)

クロック設計方法、クロック設計プログラム

【課題】半導体集積回路のクロック設計において、異なる2種類のクロック間の「セル遅延と配線遅延の比率α」の差を抑制する。

【解決手段】半導体集積回路は、第1クロック(CLK1)が供給される第1素子群と、第1クロック(CLK1)と異なる第2クロック(CLK2)が供給される第2素子群と、を備える。クロック設計方法は、第1クロック(CLK1)に関するクロックツリーシンセシスを実施することによって、第1クロックツリー構造10を作成するステップと、第1クロックツリー構造10の少なくとも一部を流用することによって、第2素子群に第2クロック(CLK2)を供給する第2クロックツリー構造20を作成するステップと、を含む。

(もっと読む)

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

半導体集積回路の設計装置及び半導体集積回路の設計方法

【課題】チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようにする。

【解決手段】熱解析部11は、設計する半導体集積回路のデータから熱解析を行い、温度分布を算出し、ベクトル生成部12は、算出された温度分布の温度勾配に応じたベクトルを生成し、ダミーパターン生成部13は、生成されたベクトルにしたがってダミーパターンを生成し、半導体集積回路のレイアウトデータに追加する。このようなダミーパターンを生成することで、温度分布が平均化され、チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようになる。

(もっと読む)

半導体装置

【課題】複数の回路ブロックの特性を正確に一致させる。

【解決手段】例えば、端子31A,31Bと、これら端子間に設けられた回路110A,110Bを備える。回路110Aは端子31Aに接続され、端子31Aから端子31Bへ向かって配置されたセル120A,130A,140Aを含む。回路110Bは端子31Bに接続され、端子31Bから端子31Aへ向かって配置されたセル120B,130B,140Bを含む。セル120A,120Bのレイアウトは、形状、サイズ及び向きがトランジスタレベルで同一である。セル130A,130B及びセル140A,140Bのレイアウトは、形状及びサイズが同一であり、トランジスタの向きが180°相違している。これにより各セルを対称配置しつつ、センシティブなセル120A,120Bにおいては電流方向の違いによる特性差が生じない。

(もっと読む)

原版データの生成方法、原版作成方法、原版データを作成するためのプログラム及び処理装置

【課題】 微細なパターンを精度よく形成する原版のデータを生成する生成方法を提供する。

【解決手段】 光源からの光を用いて原版を照明する照明光学系と、前記原版のパターンを基板に投影する投影光学系とを備える露光装置に用いられる原版のデータをコンピュータによって生成する生成方法であって、近似空中像に基づいて主パターンを決定し、補助パターンを挿入することで原版のデータを生成する生成方法を提供する。

(もっと読む)

レイアウト方法及び半導体装置の製造方法

【課題】ダブルパターニングによるトランジスタの特性ばらつきを抑える。

【解決手段】並列に配置される複数のゲート電極パターン10〜15を交互に、ダブルパターニングの第1の露光工程で形成する第1のパターン及び第2の露光工程で形成する第2のパターンとして設定し(ステップS1)、第1のパターンと第2のパターンとを並列に接続したトランジスタ対を含む回路をレイアウトすることで(ステップS2)、ダブルパターニングによるトランジスタの特性ばらつきが抑えられる。

(もっと読む)

撚り合わされた導線を有する集積回路インダクター

【課題】集積回路インダクターを提供すること。

【解決手段】第1の端子と、第2の端子と、第1の端子と第2の端子との間に連結された伝導性経路とを備え、伝導性経路は、集積回路上に複数の撚り合わされた伝導性線を含む、インダクター。撚り合わされた伝導性線は、集積回路上に少なくとも1つの金属層から形成された少なくとも第1の伝導性線と、集積回路上に少なくとも1つの金属層から形成された少なくとも第2の伝導性線とを含む、インダクター。

(もっと読む)

半導体集積回路のチップサイズ見積もり装置、及び半導体集積回路のチップサイズ見積もり方法

【課題】精度よく簡便にチップサイズを見積もることができる、半導体集積回路のチップサイズ見積もり装置、及び半導体集積回路のチップ見積もり方法を提供する。

【解決手段】回路の機能の実現に最小限必要なゲート数である最小機能ゲート数を入力する入力部1と、セルライブラリごとに所定の動作速度の達成に必要となるゲート数と前記最小機能ゲート数との比率である性能考慮ゲート数係数が予め設定された設定値保持部21と、前記最小機能ゲート数と前記性能考慮ゲート数係数とから算出されるゲート数を用いて前記回路の総面積を見積もる計算部22と、を備えたことを特徴とする。

(もっと読む)

半導体集積回路

【課題】フリップフロップにおけるアクティブ領域のレイアウトの凹凸を低減する。

【解決手段】半導体チップには、クロック領域CR1、ラッチ領域LR1およびバッファ領域BR1が設けられ、クロック領域CR1にはアクティブ領域AK5、AK6が形成され、ラッチ領域LR1にはアクティブ領域AK1、AK2が形成され、バッファ領域BR1にはアクティブ領域AK3、AK4が形成され、アクティブ領域AK1〜AK6の幅をそれぞれにおいて均一の幅として分割されている。

(もっと読む)

半導体装置

【課題】従来の入出力セルよりも回路面積の大きな入出力セルを面積効率良く配置する。

【解決手段】半導体装置において、複数の第1バッファセル31〜34は、基板の一辺に沿って1列に設けられる。複数の第2バッファセル21,22は、複数の第1バッファセルよりも基板の中央寄りの位置に、複数の第1バッファセルの配列方向に沿って1列に設けられる。複数の第1パッド81〜88は、複数の第1バッファセルの上部に上記配列方向に沿って1列に設けられる。複数の第2パッド61〜66は、複数の第1パッドよりも基板の中央寄りの位置に、上記配列方向に沿って1列に設けられる。複数の第2パッド61〜66は、各々が、複数の第1バッファセルのいずれか1つと個別に接続される複数の第3のパッド61,63,65,66と、各々が、複数の第2バッファセルのいずれか1つと個別に接続される複数の第4パッド62,64とを含む。

(もっと読む)

キャパシタおよび半導体装置

【課題】キャパシタの電極として機能する配線の延伸方向への電流供給を容易とすること。

【解決手段】第1金属層12と、前記第1金属層の膜厚方向に離間して設けられ、第1方向および前記第1方向に交差する第2方向に配列された複数の孔36を備えた第2金属層14と、前記第2金属層の膜厚方向で前記第1金属層とは反対側に離間して設けられ、前記第1方向および前記第2方向とは異なる方向に延伸し、第1配線と第2配線とが交互に設けられた複数の第1配線16aおよび複数の第2配線16bと、前記複数の第1配線と前記複数の第2配線との間に設けられた誘電体膜26と、前記複数の第1配線を、それぞれ前記複数の孔を通過し前記第1金属層に電気的に接続する複数の第1ビア配線32と、前記複数の第2配線を、それぞれ前記第2金属層に電気的に接続する複数の第2ビア配線34と、を具備するキャパシタ。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置において、レイアウトの面積効率の低下を抑制可能となる、マルチハイトセルのレイアウト構造を提供する。

【解決手段】標準論理セル10は、電源配線または接地配線となるメタル配線12を共有するようにY方向に隣接して配置された第1および第2回路領域A1,A2を備えている。X方向において、第1回路領域A1の両端部の位置x1a,x1bと第2回路領域A2の両端部の位置x2a,x2bとは、少なくともいずれか一方が異なっている。すなわち、標準論理セル10の外形形状CFは、第1および第2回路領域A1,A2の外形形状が矩形であるにもかかわらず、非矩形となっている。

(もっと読む)

半導体集積回路装置

【課題】セル高さが低減した場合であっても、容量セルの容量値を十分に確保可能なレイアウト構成を提供する。

【解決手段】第1の電源電圧を供給する電源配線11が第1の方向に延びており、電源配線11と平行に、第2の電源電圧を供給する電源配線12および第3の電源電圧を供給する電源配線13が延びている。容量素子16は、ソースおよびドレインに第1の電源電圧が与えられ、ゲートに第2または第3の電源電圧が与えられるトランジスタによって構成されている。容量素子16は電源配線11の下に、電源配線12側の領域から電源配線13側の領域にわたって形成されている。

(もっと読む)

半導体装置の製造方法、半導体装置、設計方法、設計装置、及び、プログラム

【課題】集積度及び歩留まりの低下を抑制しつつ、アニール処理に起因した素子の特性ばらつきを軽減する。

【解決手段】半導体基板1上に素子2、3、5を形成する素子形成工程と、素子形成工程の後、半導体基板1上に、選択的に、半導体基板1よりも高い光吸収率を有するか、又は、半導体基板1への光の吸収率を向上させる機能を有する加熱安定化膜7を形成する加熱安定化膜形成工程と、加熱安定化膜7を有する面側から半導体基板1に光を照射し、半導体基板1に注入された不純物を活性化するアニール工程と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】周辺回路領域を整形された形状とすることによりチップ面積を縮小する。

【解決手段】Y方向に延在する複数のデータバスDBがピッチP1でX方向に配列されたメモリセル領域40と、対応する複数のデータバスDBにそれぞれ接続された複数のバッファ回路BCが設けられたバッファ領域61とを備える。バッファ領域61上においては、Y方向に延在する複数のデータバスDBがピッチP2でX方向に配列され、ピッチP2はピッチP1よりも小さい。本発明によれば、データバスDBの配列ピッチをバッファ領域上において縮小していることから、他の回路ブロックに割当可能な面積を十分に確保することが可能となる。これにより、当該回路ブロックの幅拡大や形状の変形が不要となることから、無駄な空きスペースが生じにくく、チップ面積を縮小することが可能となる。

(もっと読む)

パターン作成方法および半導体装置の製造方法

【課題】高歩留まり且つ低コストで半導体装置を製造することができるパターン作成方法を提供すること。

【解決手段】実施形態によれば、パターン作成方法が提供される。パターン作成方法では、設計パターンに応じた基板上パターンを形成できるよう前記基板上パターンに応じたマスクパターンを作成する際に、前記設計パターン間が満たす必要のある相対関係に基づいて、前記設計パターン間に対応するマスクパターン間が前記相対関係を満たすよう前記マスクパターンを作成する。

(もっと読む)

1 - 20 / 355

[ Back to top ]