Fターム[5F064EE27]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 多層配線 (2,699) | コンタクト手段 (1,033)

Fターム[5F064EE27]に分類される特許

1,021 - 1,033 / 1,033

GHz帯伝送の中距離配線構造、GHz帯伝送の中距離配線構造に接続するドライバ回路およびレシーバ回路

【課題】 GHz帯伝送を行う場合に、伝送線路の特性インピーダンスを整合することによりTEM波の伝送を維持することができる。

【解決手段】 1つの半導体チップ内、1つの基板内、1つのシステムを構成する2つのブロック、1つのシステムを構成する2つのブロック間を中継する中継回路、の少なくとも1つに設けられたドライバ回路とレシーバ回路とを接続するツイストペア線路71は、特性インピーダンスが100Ωから135Ωの範囲でTEM波を維持する1対のペア線路73と、ペア線路73を覆いペア線路73から空中に放射されるエバーネッセント波を封じ込める金属からなるシールド部79とを有することで、特性インピーダンスを整合してGHz帯の差動信号を伝送する。

(もっと読む)

集積回路の設計方法、集積回路の設計方法に用いる設計支援プログラム及び集積回路設計システム

【課題】 ホトマスクを生産せず試作を作成することができるといったホトマスクレス試作方式の長所と量産時に試作時のパターン情報をそのまま使用することができるといったホトマスク試作方式の長所を併せ持つホトマスクレス試作方式とホトマスク試作方式を融合したホトマスクレス・ホトマスク融合方式を実現した集積回路の設計方法、集積回路の設計方法に用いる設計支援プログラム及び集積回路設計システムを提供する。

【解決手段】 パターン情報に基づいてホトマスクを用いることなく集積回路を作成するホトマスクレス工程及びパターン情報に基づいてホトマスクを用いて集積回路を作成するホトマスク工程に用いることができる共用設計環境下でホトマスクレス工程及びホトマスク工程に対応した試作用のパターン情報に基づき集積回路の試作をホトマスクを用いず作成し評価を経て必要に応じて改良を加え共通パターン情報を作成し、当該共通パターン情報に改良を加えることなく必要に応じて形式的変換を行って量産用のホトマスクを生成して使用する。

(もっと読む)

パッド下に素子を備える手法によるウェハの有効利用

半導体構造(20)のパッドエリア(21)下に能動素子(25)を組み込むことにより、シリコンエリアのより効率的な利用を可能とする。パッドエリア(21)は、上方に第1の金属層(23)を備えた基板(22)を含む。第2の金属層(26)は第1の金属層(23)の下とする。能動素子(25)は基板内であって、第2の金属層(26)の下に備えられる。誘導体層(24)は第1の金属層(26)と第2の金属層(23)とを分離する。誘導体層(24)内のビア(27)は第1の金属層(23)と第2の金属層(26)とを電気的に接続する。ビア(27)は能動素子(25)と接続する。隣接金属層(424、425、426)を第1の金属層(23)と第2の金属層(26)の間に配置してもよい。  (もっと読む)

(もっと読む)

構造体及びレーザヒューズのプログラミング

レーザヒューズを製作する方法及び構造体と、レーザヒューズをプログラミングする方法とを提供する。レーザヒューズは、第1自己不活性化導電性材料で充填された2つのビア(820a及び820b)を有する第1誘電体層(807)を含む。ヒューズリンク(810’)は第1誘電体層(807)の上部に位置する。ヒューズリンク(810’)は2つのビア(820a及び820b)を電気的に接続し、レーザビームに当てられた後に電気抵抗を変える特性を持つ第2材料を含む。2つのメサ(825a,830a及び825b,830b)は、ヒューズリンク(810’)上、並びに2つのビア(820a及び820b)の真上に位置する。2つのメサ(825a,830a及び825b,830b)は各々、第3自己不活性化導電性材料を含む。レーザヒューズは、レーザビームをヒューズリンク(810’)に向けることによりプログラミングされる。ヒューズリンク(810’)上のレーザビームの衝撃に応えて、ヒューズリンク(810’)を吹き飛ばすことなく、ヒューズリンク(810’)の電気抵抗が変わるようにレーザビームが制御される。このような電気抵抗の変化は感知され、デジタル信号へ変換される。

(もっと読む)

(もっと読む)

検査パッド構造を有する集積回路および検査方法

半導体装置(10)は、ワイヤボンディングのために周囲に多数のボンド・パッド(24)を有する。半導体装置(10)は、モジュール(12)およびその他の回路を有するが、モジュール(12)は検査のために他の回路よりも遥かに長い時間を必要とする。比較的少数のボンド・パッド(20)、モジュール・ボンド・パッド(20)が、少なくとも部分的に、内蔵自己検査(BIST)(16)回路を有する半導体装置によるモジュール検査のために必要である。これらのモジュール・ボンド・パッド(22)の機能性は、半導体装置(10)の上面上および内部に二重化されており、モジュール検査パッド(22)は周辺のボンド・パッド(24)よりも遥かに大きい。検査のために大きなパッド(22)を有することにより、プローブ・ニードルを長くすることができ、したがって並行検査機能が向上する。機能性の二重化は、モジュール・ボンド・パッド(20)およびモジュール検査パッド(22)が互いに短絡しなくてよいように、検査パッド・インターフェースを介して達成する。  (もっと読む)

(もっと読む)

製造を容易にする設計

【課題】製造容易性を改善するために、既存の超小型装置設計を変更する技術を提供する。

【解決手段】これらの技術により、設計者は、設計に於けるデータに関連した製造基準を受領する。次に、関連した設計データが識別されて、超小型装置設計者へ供給され、該設計者は、製造基準に基づいて設計変更を選択することが出来る。このようにして、設計者は、超小型装置の元の設計に於いて、半導体ファンドリからの製造基準を直接的に包含させることが出来る。

(もっと読む)

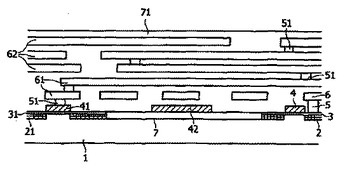

機密性を要する半導体製品、特にスマートカード・チップ

機密性を要する半導体製品、特にスマートカード・チップを提供するため、チップ設計によって実現されうる電気的に活性な構造(2、3、4、5、6)が、例えばシリコンからなるウェーハ(1)内及びウェーハ(1)上に、回路機能の形態で製造されるだけでなく、残りの領域に、それらの下に置かれた機密性を要する回路構造を解析するリバース・エンジニアを大幅に妨げる、互いに絶縁された充てん構造のさらなる導電性部分(42、61、62)(タイル)が設計プログラムによって形成される。形成された部分を説明された偶然の信号経路と連結するための形成された部分間のコンタクトは、「手で」、又は、当該設計プログラムと対応するルーティング・プログラムとの組合せによって配置されることができる。充てん導電性部分はさらに、さらなる回路機能(例えば解析回路)を提供するために、トランジスタ、ダイオード、抵抗器又はコンデンサなどの回路構成部品に接続されてもよい。  (もっと読む)

(もっと読む)

斜めストライプを有するパワーグリッド構造を形成するための方法及び装置

【課題】集積回路で使用される斜めストライプを有するパワーグリッド構造を形成するための方法及び装置を提供する。

【解決手段】斜め電力ストライプ及び斜め接地ストライプを有するICのパワーグリッド構造を規定して生成する方法。ストライプが、得られるICの下部境界に対して45°又は135°の斜め方向に配置されることになるように、ストライプは、ICレイアウトのx座標軸に対してそれぞれ45°又は135°の斜め方向に配置される。斜めの電力及び接地ストライプは、斜め信号配線に有益である。ストライプは、ICの一つの層に亘って又はICの一つよりも多い層に亘って配置することができる。斜め電力ストライプは、ICの層上に様々な幅及び/又は様々な間隔幅を有することができる。斜め接地ストライプも、ICの層上に様々な幅及び/又は様々な間隔幅を有することができる。

(もっと読む)

クロストークノイズを低減するバス配線を備える電気回路装置、電気回路装置のバス配線の配線方法、電気回路装置のバス配線の配線システム

【課題】束配線を備える電気回路装置、特に半導体集積回路装置のバス配線のクロストークノイズを低減する配線レイアウトを提供すること。

【解決手段】複数の機能ブロックで共通に使用されるバス信号を伝達するバス配線が束状に配置されるバス配線を備える電気回路装置において、前記バス配線を構成する各個別配線(A0〜A7)は3以上であって、互いに隣接する個別配線間で配線経路変更点3,4,…において各個別配線を入れ替えるようにした。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】半導体素子の発熱に起因する半導体集積回路装置の温度上昇を低減する。

【解決手段】多層配線構造を備えた半導体集積回路装置において、多層配線構造を構成する接続孔及び金属配線層と同じ導電材料からなり、信号伝送用の接続孔及び金属配線層(領域C参照)とは異なる経路で上層側に延びる熱伝導部33,35,37を備えている(領域A,E,F参照)。領域Aにおいて、完全空乏型SOIトランジスタのゲート動作により発生した熱は、コンタクト層19、メタル配線層M1、ビア層21、メタル配線層M2に伝導され、さらに熱伝導部33を介して最上層のメタル配線層M6まで伝導され、絶縁層17の上面側から放熱される。これにより、半導体集積回路装置の温度上昇を低減することができる。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】 機能マクロの電源接続構造に関わらず、機能マクロを回転配置してもマクロ内電源接続端とチップレベル電源配線との接続を可能としたLSIのレイアウト設計方法を提供する。

【解決手段】 回路接続情報に基づいて、機能マクロを含む所定の素子パターンをチップ領域上の所定位置に配置する第1工程P1と、第1電源配線レイアウト情報を生成する第2工程P2と、同電位電源接続端及び同電位電源配線の有無を調べる第3工程P3と、同電位電源接続端及び同電位電源配線のレイアウト情報を抽出する第4工程P4と、第1接続孔レイアウト情報を生成する第5工程P5と、電源開放端の有無を調べる第6工程P6と、全ての電源開放端のレイアウト情報を抽出する第7工程P7と、電源開放端を所望のチップレベル電源配線に接続するための修正レイアウト情報を生成する第8工程P8とを含む。

(もっと読む)

半導体装置とその製造方法およびモノリシックマイクロ波集積回路

【課題】 強度低下や寸法増大を抑えながら、バイアホールの接地インダクタンスを低減できる半導体装置とその製造方法およびMMICを提供する。

【解決手段】 このマイクロ波帯用増幅器GaAsMMICは、その接地電極8が、3個のバイアホール11からなるバイアホール群12を有し、この3個のバイアホール11は、その内側に充填されたメッキ金属10aが近接されて形成され、その相互作用によって高周波的な電磁界結合が発生して、接地インダクタンスが低減された。

(もっと読む)

半導体集積回路

【課題】 機能マクロの電源配線のレイアウト又は位置が多少変わっても、新たに設計し直すことなく、機能マクロの電源配線と半導体集積回路の電源配線とを接続する。

【解決手段】 電源配線2は、複数の低電位側電源配線2Gと複数の高電位側電源配線2Vとからなり、電源配線5は、複数の低電位側電源配線5Gと複数の高電位側電源配線5Vとからなる。電源端子31は、複数がそれぞれ等間隔に配置されるとともに、低電位側電源配線2Gと低電位側電源配線5Gとを接続する矩形状の低電位側電源端子31Gと、高電位側配線2Vと高電位側電源配線5Vとを接続する矩形状の高電位側電源端子31Vとからなる。低電位側電源端子31Gと高電位側電源端子31Vとは、互いに隣接するように配置されている。

(もっと読む)

1,021 - 1,033 / 1,033

[ Back to top ]