Fターム[5F064GG10]の内容

ICの設計・製造(配線設計等) (42,086) | 製造プロセス技術 (798) | その他 (111)

Fターム[5F064GG10]に分類される特許

1 - 20 / 111

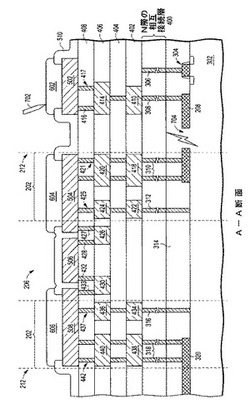

半導体ダイ上にフィーチャをめっきするためのヒューズバス

【課題】半導体ダイ上に相互接続部又はボンドパッドなどのフィーチャ構造を電気めっきする方法を提供する。

【解決手段】方法は半導体基板の上方に複数のヒューズ(208)を形成する工程と、半導体基板の上方の複数の相互接続層(400〜408)と、該複数の相互接続層の上面の複数の相互接続パッド(502)とを形成する工程と、を含む。シールリング(202)が、半導体基板(302)と、前記複数の相互接続パッド(502)と、前記複数のヒューズ(208,320)とに形成された能動回路を包囲する。各ヒューズ(208,320)は、対応する相互接続パッド(502)とシールリング(202)とに電気的に接続される。各ヒューズ(208)が導通状態にあるとき、該ヒューズは対応する相互接続パッド(502)をシールリング(202)に電気的に接続する。

(もっと読む)

原版データの生成方法、原版作成方法、原版データを作成するためのプログラム及び処理装置

【課題】 微細なパターンを精度よく形成する原版のデータを生成する生成方法を提供する。

【解決手段】 光源からの光を用いて原版を照明する照明光学系と、前記原版のパターンを基板に投影する投影光学系とを備える露光装置に用いられる原版のデータをコンピュータによって生成する生成方法であって、近似空中像に基づいて主パターンを決定し、補助パターンを挿入することで原版のデータを生成する生成方法を提供する。

(もっと読む)

レイアウト方法及び半導体装置の製造方法

【課題】ダブルパターニングによるトランジスタの特性ばらつきを抑える。

【解決手段】並列に配置される複数のゲート電極パターン10〜15を交互に、ダブルパターニングの第1の露光工程で形成する第1のパターン及び第2の露光工程で形成する第2のパターンとして設定し(ステップS1)、第1のパターンと第2のパターンとを並列に接続したトランジスタ対を含む回路をレイアウトすることで(ステップS2)、ダブルパターニングによるトランジスタの特性ばらつきが抑えられる。

(もっと読む)

半導体装置および半導体装置設計方法

【課題】半導体基板においてダミーパターンの配置密度を高める。

【解決手段】半導体基板104には、配線パターン102とダミーパターン106がレイアウトされる。配線パターン102の周囲にはマージン領域がレイアウトされ、マージン領域の周囲にダミー領域がレイアウトされる。このダミー領域に、複数のダミーパターン106がレイアウトされる。ダミーパターン106は、ダミー領域の延伸方向に配列される。マージン領域とダミー領域は、配線パターン102を基準として交互にレイアウトされる。

(もっと読む)

偏在率算出方法、半導体装置の製造方法及びプログラム

【課題】レイアウトデータからCu残が発生しやすい品種やレイヤであるか否かを判定することのできる偏在率算出方法を提供する。

【解決手段】CPUは、検証レイヤにおいて所定サイズの検証エリア毎にパターン密度を算出するステップS13と、算出されたパターン密度を複数の密度範囲に分別し、各々の密度範囲に属するパターン密度の分布を示す複数の密度マップMAP0〜MAP7を生成するステップS14とを実行する。また、CPUは、各密度マップMAP0〜MAP7に所定量のプラスシフトを加えるステップS15と、パターン密度の密度差が第1基準値以上となる組み合わせの密度マップMAP0〜MAP7を重ね合わせ、両密度マップで重複した領域を抽出するステップS16とを実行する。CPUは、その抽出した領域の総面積を算出するステップS17と、算出した総面積と第2基準値とを比較するステップS18とを実行する。

(もっと読む)

半導体集積回路の設計方法、設計プログラム、及び設計支援装置

【課題】半導体集積回路の設計TATを短縮する。

【解決手段】本発明による半導体集積回路の設計方法は、コンピュータ装置10によって実行される半導体集積回路の設計方法であって、論理セル500と配線セル400をチップ上に配置するステップと、論理セル500内のゲート505に対するアンテナルール122を配線セル400の第1アンテナ用ライブラリ101に追加することで、第1アンテナ用ライブラリ101を第2アンテナ用ライブラリ201に変更するステップと、配線セル400と他の論理セル510を第1配線550で接続するステップと、第2アンテナ用ライブラリ201に規定されたアンテナルール122に従い、ゲート505の面積に対する前記第1配線550の面積の比を検証する第1検証ステップとを具備する。

(もっと読む)

パターン作成方法および半導体装置の製造方法

【課題】高歩留まり且つ低コストで半導体装置を製造することができるパターン作成方法を提供すること。

【解決手段】実施形態によれば、パターン作成方法が提供される。パターン作成方法では、設計パターンに応じた基板上パターンを形成できるよう前記基板上パターンに応じたマスクパターンを作成する際に、前記設計パターン間が満たす必要のある相対関係に基づいて、前記設計パターン間に対応するマスクパターン間が前記相対関係を満たすよう前記マスクパターンを作成する。

(もっと読む)

半導体装置

【課題】2個のビアを用いた配線接続構造を、ホットスポットが生じにくい構造によって実現する。

【解決手段】第1配線層において第1方向に延びる第1配線11と、第1配線層の上層または下層の配線層に形成された接続対象配線30とを電気的に接続するために、第1および第2のビア21,22が設けられている。そして、第1配線11の第2端部11bから、第1方向と直交する第2方向に第3配線13が延びており、さらに第3配線13から、第1方向において第1配線11と反対の向きに第4配線14が延びている。すなわち、第1、第3、第4配線11,13,14によってクランク状の配線が形成されている。そして、第3配線13の配線幅W3は、第1配線11における端部11a,11b間の部分の配線幅W1以上である。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ(FUSE)を備えた半導体装置の信頼性を向上する。

【解決手段】半導体基板11の主面上に形成にされた多層配線を構成する層M1〜M6のうちの層M4に設けられた電気溶断型の救済用のヒューズ4aおよび試験用のヒューズ4bと、ヒューズ4aの近傍であって層M2および層M6に設けられた一対の導電板10aと、ヒューズ4bの近傍であって層M3および層M5に設けられた一対の導電板10bとから構成する。ヒューズ4bと導電板10bとの間が、ヒューズ4aと導電板10aとの間より近いものとする。

(もっと読む)

半導体装置

【課題】裏面FIB加工における場所特定を容易にする。

【解決手段】半導体装置は、第1方向および前記第1方向に直交する第2方向の平面内に広がる第1導電型の半導体基板60の表面上に形成された回路部65と、前記半導体基板内の表面側に形成され、前記回路部を構成し、素子として機能する、前記第1導電型と異なる第2導電型の複数のウェル61と、前記半導体基板内の表面側に形成され、前記回路部を構成せず、素子として機能しない、前記第2導電型の複数のダミーウェル62と、を具備する。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化されても高精度を維持できるキャパシタを提供する。

【解決手段】キャパシタは、平面上に交互に配列した、直線状で第1の長さを有し第1の方向に延在する第1の電極パターンと、直線状で前記第1の長さより短い第2の長さを有し、前記第1の方向に延在する第2の電極パタ―ンと、前記第1の電極パターンに第1の電圧を、第1のビアプラグを介して供給する第1の配線パタ―ンと、前記第2の電極パターンに第2の電圧を、第2のビアプラグを介して供給する第2の配線パタ―ンと、を備え、前記第1および第2の電極パターンをそれぞれの前記第1の方向で比較した場合、前記第1の電極パターンの第1の端部が、前記第1の端部に対応する前記第2の電極パターンの第2の端部よりも突出しており、前記第1の電極パターンの前記第1の端部に対向する第3の端部が、前記第3の端部に対応する前記第2の電極パターンの第4の端部よりも突出している。

(もっと読む)

半導体装置

【課題】コンタクトパッドを含む所定領域内に形成できる配線数を増加させることができ、設計レイアウトの自由度を向上させることができるパターンレイアウトを有する半導体装置を提供する。

【解決手段】第1方向に所定ピッチでラインとスペースが交互に配列された第1配線パターンと、第1配線パターンのライン間に配置され、所定ピッチの3倍の幅を有するコンタクトパッド30Bとを有する。第1配線パターンのラインとコンタクトパッドとの間隔は所定ピッチであり、所定ピッチは100nm以下である。

(もっと読む)

半導体装置、パターンレイアウト作成方法および露光マスク

【課題】 高集積化に有効な複数の配線パターンを含む配線パターン群を備えた半導体装置を提供すること。

【解決手段】 同一の配線用途のN(N≧3)本の配線パターンを含む配線パターン群を含む。N本の配線パターンの各々は別の層の配線郡内の配線パターンと電気的に接続するための接続領域を含む。N本の配線パターンは、配線パターンN1と、配線パターンN1の長手方向と異なる一方向に配置された二つ以上の配線パターンNi(i≧2)を含む。二つ以上の配線パターンNiはiの値が大きいほど配線パターンN1から離れた位置に配置され、二つ以上の配線パターンNiは少なくとも一つ以上のパターンNp(2≦p<N)と少なくとも一つ以上の配線パターンNq(p<q≦N)を含む。少なくとも一つ以上の配線パターンNpはpの値が大きいほど長手方向の寸法が長く、少なくとも一つ以上の配線パターンNqは、qの値が大きいほど、長手方向の寸法が短い。

(もっと読む)

半導体装置、その製造方法およびプログラミング方法

【課題】プログラミングの通電を必要最小限とすることができ、ヒューズヴィアの切断不良による論理回路の歩留りの低下も改善することができる半導体装置を提供する。

【解決手段】ヒューズヴィアの切断の要否が未定の部分にはヴィア切断型電気ヒューズ3が形成されており、切断の必要が確定している部分にはヒューズヴィアが省略されたヴィア切断型電気ヒューズ5が形成されている。

(もっと読む)

半導体装置

【課題】面積の増加を抑えつつ、ヒューズ構造体のデータの保持量を増加する。

【解決手段】半導体装置100は、基板(不図示)上に形成されたヒューズ構造体120を含む。ヒューズ構造体120は、第1の配線(122)および第2の配線(124)と、これらを接続するビア123とから構成された電気ヒューズ121と、一端がビア123の側方にビア123に接続して形成された抵抗配線128と、を含む。電気ヒューズ121のビア123は、基板の積層方向において、第1の配線(122)との接続箇所から抵抗配線128との接続箇所までの間に、面内方向の断面積が第2の配線(124)との接続箇所から抵抗配線128との接続箇所までの面内方向の断面積よりも小さい箇所を有する。

(もっと読む)

半導体装置のレイアウト検証方法と装置及びプログラム

【課題】Diffusionラウンディングの影響を防ぐためにトランジスタの特性変動量を定量的に考慮した最適な設計基準に基づく設計の検証を可能とする方法の提供。

【解決手段】拡散層1において第1の辺3と第2の辺4で確定されるコーナー部に形成されるDiffusionラウンディング5の形状を数式で表現し、コーナー部に隣接するゲート幅WのトランジスタTrに関して、第2の辺とゲートの間隔をX1とし、Diffusionラウンディングによるゲート幅の誤差をΔWとし、Diffusionラウンディングの形状パラメータとΔWとX1の関係と、トランジスタTrの特性変動率とゲート幅の変動率の関係とから、第2の辺とゲートの間隔X1の設計基準値を導出し、レイアウト情報からコーナー部に隣接して配設されるトランジスタのゲートと第2の辺の間隔を抽出し、抽出したゲートと第2の辺の間隔が、基準値を満たすか否か判定する。

(もっと読む)

半導体集積回路装置

【課題】設計工数をほとんど掛けないで、CMP対策及び短時間光アニール対策の両対策に最適化されたダミーパターンを有する半導体集積回路装置を提供すること。

【解決手段】基板上に、メモリマクロ領域10及び機能回路領域20を有する半導体集積回路装置1において、機能回路領域20間、及び、メモリマクロ領域10と機能回路領域20との間に配置されるとともにダミーパターン41を含むダミーパターン領域40を備え、ダミーパターン41は、前記メモリセルアレイ領域におけるメモリセルパターン11の拡散層12、13及びゲート電極14と同等のパターンであり、ダミーパターン領域40におけるダミー拡散層42、43及びダミーゲート電極44の面積率は、メモリセルアレイ領域における拡散層12、13及びゲート電極14の面積率と同等以上である。

(もっと読む)

半導体装置の製造方法、半導体装置の検査方法、及び半導体装置

【課題】半導体装置の検査において、電極パッドの配列、スクライブ領域の幅に影響されることなくプローブカードを共有化し、プローブカードの製作費用を低減する。

【解決手段】基板20はチップ領域100、スクライブ領域200および電極パッド300を備えている。チップ領域100は基板20上の第1の方向に沿って、スクライブ領域200により互いに分離されるように並んでいる。電極パッド300は第1の方向に沿って周期性をもって配列している。接続用電極パッド320はチップ領域100に形成され、ダミー電極パッド340は少なくともスクライブ領域200に形成されている。電極パッド300の間隔はスクライブ領域200の幅よりも狭い。電極パッド300の配列と平行な方向における、チップ領域100とスクライブ領域200を合わせた幅は、電極パッド300間隔の整数倍である。

(もっと読む)

マスクレイアウト作成方法、マスクレイアウト作成装置、リソグラフィ用マスクの製造方法、半導体装置の製造方法、およびコンピュータが実行可能なプログラム

【課題】コヒーレンスマップ法を使用して補助パターンを作成する場合に、その配置精度を向上させることが可能なマスクレイアウト作成方法を提供する。

【解決手段】リソグラフィ工程で危険点となる可能性の高い設計レイアウトを設定し、設定した設計レイアウトに対して、マスクレイアウトを生成するコヒーレンスマップカーネルを設定し、設定されたコヒーレンスマップカーネルと設計レイアウトとに基づいて、コヒーレンスマップを作成し、コヒーレンスマップから補助パターンを抽出・整形してマスクレイアウトを生成し、マスクレイアウトの最適度を評価するコスト関数COSTを定義し、当該コスト関数を使用して、生成したマスクレイアウトを評価し、コスト関数で評価されるマスクレイアウトが最適となるまで、コヒーレンスマップカーネルのパラメータおよびコヒーレンスマップから補助パターンを抽出・整形する際のパラメータの少なくとも一方を変更する。

(もっと読む)

アンチヒューズ構造およびアンチヒューズ構造の製造方法

【課題】低い印加電圧(3V以下)で導通状態を変更可能なアンチヒューズ素子(アンチヒューズ構造)を提供する。

【解決手段】本発明のアンチヒューズ構造100は、第一配線3と、前記第一配線3上に順次積層された、不純物を含有した第一の多結晶シリコン膜6、第一のタングステンシリサイド膜7、第一の窒化タングステン膜8からなる第一のアンチヒューズ部20aと、前記第一のアンチヒューズ部20a上に接続された第二配線10と、を具備してなることを特徴とする。

(もっと読む)

1 - 20 / 111

[ Back to top ]