Fターム[5F064HH10]の内容

ICの設計・製造(配線設計等) (42,086) | 設計、製造における計算機技術 (6,629) | ソフトウェア(プログラム)関係 (5,214) | 評価、検査、試験、監視 (946)

Fターム[5F064HH10]に分類される特許

161 - 180 / 946

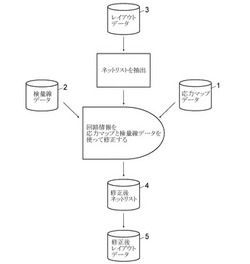

ネットリスト作成方法、回路シミュレーション方法、半導体集積回路装置の設計方法及び半導体集積回路装置の製造方法

【課題】パッケージにより生じる回路特性のバラツキを簡便にかつ正確に予測する。

【解決手段】設計されたレイアウトデータと、パッケージに起因してシリコンチップに加わる応力値の分布を示す応力マップデータと、シリコンチップに搭載される各素子について、応力値と素子の特性変動量の関係を示す検量線データとを用いる。レイアウトデータから素子の種類、位置、方向、大きさのうち1つ以上の情報を読み取る。その素子の位置での応力値を応力マップデータから読み取る。その応力値に対するその素子の特性変動量をその素子に対応する検量線データから読み取る。その特性変動量に基づいてその素子の特性を修正してネットリストの作成を行なう。

(もっと読む)

検証プログラム、検証方法、および検証装置

【課題】中間ノード直下に形成される空乏層による影響を再現してシミュレーション精度の向上を図ること。

【解決手段】検証装置は、NMOSに関する回路モデルである等価回路400内から、接合抵抗RJLGSおよび接合容量CJGSと、接合抵抗RJLGDおよび接合容量CJGDとを備える並列回路と、並列回路と基板電極とを接続する接続抵抗Rdepを検出する。つぎに、検証装置は、接合抵抗RJLGSおよび接合抵抗RJLGDと、接続抵抗Rdepとが振幅の変化に与える影響を示す第1の係数を算出し、接合容量CJGSとCJGDと接続抵抗Rdepとが位相の変化に与える影響を示す第2の係数を算出する。そして、第1の係数と第2の係数との合計値により接合容量CJG(=CJGS=CJGD)を補正する。

(もっと読む)

エレクトロマイグレーション検証装置

【課題】検証精度を高めることのできるエレクトロマイグレーション検証装置を提供する。

【解決手段】前記複数の矩形図形が段差状に接続されている部分をオフセット接続部として識別し、前記オフセット接続部を示すオフセット接続部データを生成する、識別部と、前記オフセット接続部データに基づいて、前記オフセット接続部における最小配線幅を算出し、前記最小配線幅を示す最小幅データを生成する、最小幅算出部と、前記オフセット接続部を流れる電流値と、前記最小配線幅とに基づいて、前記オフセット接続部における電流密度を算出し、算出された電流密度を示す電流密度データを生成する、電流密度算出部と、前記電流密度データに基づいて、前記電流密度を予め設定された基準値と比較し、比較結果に基づいて、エレクトロマイグレーションが発生するか否かを判定する、判定部と、を具備する。

(もっと読む)

半導体集積回路のレイアウト装置、及び半導体集積回路のレイアウト方法

【課題】TATの増加を抑えることのできる、半導体集積回路のレイアウト装置を提供する。

【解決手段】色分けスタンダードセルデータに基づいて、前記複数のパターン部分のなかからセルの外周部に配置された外周パターン部分を識別し、前記外周パターン部分が他のパターンの形成に影響を与える範囲を示す制約エリアを設定し、前記制約エリアを前記各フォトマスクと対応付けて示す制約データを生成し、前記制約データを前記スタンダードセルと対応付けて前記セルライブラリに登録する、制約データ生成部と、セルライブラリを参照し、半導体チップ上に複数の前記スタンダードセルをレイアウトし、チップレイアウトデータを生成する、チップ配置設計部と、前記チップレイアウトデータ及び前記制約データを取得し、前記チップレイアウトデータにおいて、同一のフォトマスクにおいて前記制約エリアが重なるか否かを判定する、色分け隣接評価部と、前記制約エリアが重なった場合に、前記チップレイアウトデータを修正する、隣接配置修正部とを具備する。

(もっと読む)

設計装置、設計方法、及び設計プログラム

【課題】タイミング違反の修正の問題を解消する。

【解決手段】設計装置10は、クロックツリーを生成するクロックツリー生成部121と、クロックツリー生成部121により生成されたクロックツリーに対応する回路データについて、セットアップタイミングを考慮せずにホールド違反を修正するように、遅延素子を論理的に挿入する論理修正部122と、論理修正部122の処理結果に基づいて、半導体集積回路のレイアウトを修正するレイアウト修正部123と、レイアウト修正部123により修正された半導体集積回路のレイアウトを出力する出力部124と、を備える。

(もっと読む)

設計装置

【課題】消費電力を低減し、誤動作を防止することができるフリップフロップ回路を設計するための設計装置を提供することを課題とする。

【解決手段】第1の入力信号、第1のイネーブル信号及び第1のクロック信号を入力する第1のフリップフロップ回路の第1の設計データに対して、第1のクロック信号の周波数の2倍以上の周波数のクロック信号で第1の静的タイミング解析を行う第1の静的タイミング解析部(S11)と、第1の静的タイミング解析の結果が合格の場合には、第1の設計データを入力し、第1のフリップフロップ回路を第2のフリップフロップ回路に変換した第2の設計データを生成する第1の変換部(S13)とを有し、第1のフリップフロップ回路はクロックゲーティング回路を有さず、第2のフリップフロップ回路はクロックゲーティング回路を有する設計装置が提供される。

(もっと読む)

半導体集積回路の設計装置、及び、半導体集積回路の設計方法

【課題】配線長やビア数に起因する不良の流出を削減すること。

【解決手段】本発明では、複数のセルと複数の信号線とを含む回路の接続を表す第1の回路情報に基づいてレイアウトを実行し(S21)、その回路情報を第2の回路情報とすると共に、レイアウトの実行結果から、複数の信号線の各々の配線長と、複数の信号線の各々が経由するビアホールの数であるビア数とを抽出する(S22)。第2の回路情報に対して故障シミュレーションを実行し、故障の検出ができないノードである故障未検出ポイントを抽出する(S23)。故障未検出ポイントのそれぞれに対して、配線長及びビア数を用いて重み付けを施し(S24)。故障未検出ポイントの中から、重み付けの結果を表す算出値が設定値を超える故障未検出ポイントを選択し、その故障未検出ポイントに対してテストポイントを挿入する(S25)。

(もっと読む)

半導体装置及びその配置配線方法

【課題】プリミティブセルに用いる金属配線層を増やすことなくプリミティブセルを小型化する。

【解決手段】素子形成領域に複数の回路素子によってプリミティブセルを構成する場合に、素子形成領域に前記プリミティブセルを構成するために必要な第1導電型の第1半導体ウェル領域及び第2導電型の第2半導体ウェル領域を並列的に複数個形成し、その上に前記素子形成領域の延在方向に一定ピッチで規則的に複数のゲート配線を配置したとき、形成された前記第1半導体ウェル領域及び前記第2半導体ウェル領域にL字型に屈曲された形状があるとき、これをL字形の屈曲部分を隣のウェル領域に延長してT字形の形状とし、延長した部分に、ソース電極とドレイン電極が共に電源ライン又はグランドラインに接続するダミーMOSトランジスタを構成し、プリミティブセルを構成する素子の接続を一層の金属配線層の金属配線を用いて行う。

(もっと読む)

レイアウト装置及びレイアウト方法

【課題】クロックツリー設計において、簡潔なスキュー調整をすることができるレイアウト装置及びレイアウト方法を提供すること。

【解決手段】本発明にかかるレイアウト装置1は、想定スキュー値記憶部141、遅延挿入部133、遅延調整部134を備える。想定スキュー値記憶部141は、クロックツリーの段数に応じて予め定められた想定スキュー値を格納する。遅延挿入部133は、想定スキュー値が要求スキュー値以下である場合、当該クロックツリーの最上位側に遅延調整バッファ206を挿入する。遅延調整部134は、クロックツリーのスキュー値が要求スキュー値以下となるように、クロックツリーの配線後に、遅延調整バッファ206の遅延を調整する。

(もっと読む)

集積回路における相互接続レイアウトのための方法および装置

実施形態は、集積回路(IC)を設計する方法(たとえば、コンピュータで実現される方法)に関する。この実施形態において、基板(402)上の集積回路の導電層(404−1,404−2,404−3,404−4,404−5)を記述するレイアウトデータ(400)が、集積回路のための設計仕様データに従って生成される。導電層は、ボンディングパッド(406)の最上層を含む。レイアウトデータにおける金属構造体(408)が変更されて、各々のボンディングパッド(406)の下の閾値体積内の導電層(404−1,404−2,404−3,404−4,404−5)の重畳した平面内における金属密度を最大化する。レイアウトデータ(400)の記述は、集積回路を製造するための1以上のマスクに生成される。重畳した平面内における金属密度を最大化することにより、相互接続体における誘電性材料(412)を通る縦方向チャネルが減少される、あるいはなくなる。したがって、α粒子が容易に相互接続体を貫通して下部の基板(402)に達することができなくなり、メモリセルにおけるシングルイベントアップセットのようなソフトエラーを減少させる。  (もっと読む)

(もっと読む)

クロックジッタ抑制方法及びプログラム

【課題】クロックジッタ抑制方法及びプログラムにおいて、比較的短時間、且つ、比較的低コストでプログラマブルデバイス等の半導体集積回路のクロックジッタを確実に抑制することを目的とする。

【解決手段】クロックバッファに接続された記憶素子に論理値を設定し、記憶素子の閾値電圧を可変設定し、半導体集積回路内の解析対象となる対象回路を動作させた状態で記憶素子に保持されている値を読み出し、閾値電圧と、読み出された値が前記論理値と反転関係にある記憶素子と、読み出しの対象となった各記憶素子の位置情報に基づいて、クロックバッファの電源電圧のノイズの影響度と一定以上のノイズの影響を受ける箇所を特定し、する解析処理を行い、解析処理の結果に基づいて半導体集積回路の構成要素の配置と配線の制約条件を作成し、ノイズが低減するように制約条件の配置を変更して再配置する再配置処理、又は、制約条件の配線を変更して再配線する再配線処理を行うように構成する。

(もっと読む)

スキャンフリップフロップ追加システム及びスキャンフリップフロップ追加方法

【課題】設計工数の増大や設計の後戻りが発生していた。

【解決手段】既存スキャンパスの複数のFFの接続情報を含む論理接続情報と、追加FFと論理接続情報のFFのレイアウト、スキャンイン端子、スキャンアウト端子とを接続するネットの情報を含むレイアウト情報と、ネットの単位配線長当たりの遅延時間を計算する情報を含む遅延ライブラリ情報と、ネットの遅延を制約する遅延制約情報とを入力し、それら情報を参照し、追加FFの挿入先を決定する追加先決定手段と、追加された追加FFを既存スキャンパスに挿入するように論理接続情報を更新する論理接続情報更新手段と、更新された論理接続情報を参照し、接続が変更されたスキャンイン端子、スキャンアウト端子間の配線を行いレイアウト情報を更新する再配線手段と、それら更新された情報を出力するするFF追加システム。

(もっと読む)

半導体集積回路の設計方法

【課題】半導体集積回路の電源パッドの配置を決定するためのTATをより短縮した半導体集積装置の設計方法を提供する。

【解決手段】半導体集積回路の設計方法としてのCAD設計ツール5は、半導体チップに電源電位を供給する電源パッドの供給可能電流量に基づき、各電源パッドに対し、それぞれ供給する電力の基準値となる電力基準値としての消費電力基準値を設定し、半導体チップ領域を、当該領域が消費電力基準値以下の消費電力の分割領域となるまで分割し、半導体チップの内部回路に電源電位を供給する電源配線のうち、分割領域としての確定エリアの中心に最も近い電源配線の上に電源パッドを配置する。

(もっと読む)

半導体集積回路自動開発システム

【課題】半導体製品の開発における人の介在による時間的損失を抑制する

【解決手段】既開発製品データベース(6)と、既開発製品データベース(6)に格納された対策を実行シェルの形態に自動生成する第1のプログラム(13)と、実行シェルを自動で起動する第2のプログラム(14)とを具備する半導体集積回路自動開発システム(1)を構築する。ここにおいて、半導体集積回路自動開発システム(1)は、配置配線設計の工程を実行した結果に対する結果検証し、結果検証の結果で問題があった場合に、既開発製品データベース(6)と自動照合を行う。そして。自動照合の結果に対応した対策である実行シェルを、第1のプログラム(13)により生成し、生成された実行シェルを、問題の生じた工程に戻って第2のプログラム(14)により実行する。

(もっと読む)

半導体デバイスパターン検証方法およびその検証プログラム

【課題】計算負荷を低減でき、計算時間を低減できる半導体デバイスパターン検証方法および検証プログラムを提供する。

【解決手段】半導体デバイスパターン検証方法は、マスクパターンを算出する第1工程<ST11>、半導体基板上に形成されるフォトレジストの形状を算出する第2工程<ST12>、図形演算処理を用いて一律リサイズを行い、擬似的な仮加工形状に限定して算出する第3工程<ST13>、設計パターンが前記半導体基板上に形成されるか否かについて図形検証を行い、危険箇所候補を検出する第4工程<ST14>、危険箇所候補の加工シミュレーションを行い、部分加工形状を算出する第5工程<ST15>を具備する。

(もっと読む)

再構成可能メモリを利用した半導体集積回路の設計装置、設計方法および、プログラム

【課題】記憶容量およびポート位置が可変な再構成可能メモリを利用して、小面積かつ高性能な半導体集積回路を実現する。

【解決手段】論理モジュールとメモリブロックからなるネットリストに関する情報と、排他的に利用されるメモリブロックに関する情報とで構成される、共有可能なメモリブロックの集合に関する情報を入力する入力部101と、ネットリストに関する情報に基づいて、論理モジュールとメモリブロックの配置位置を決定するフロアプランニング部102と、メモリ共有化指標設定部103と、共有化メモリ選択部104と、遅延および配線性評価・判定部106と、非共有化メモリ選択部107と、ネットリスト更新部105と、ネットリスト更新部105によって更新されたネットリストと、フロアプランニング結果とを設計結果として出力する出力部108と、を備える半導体集積回路の設計装置100。

(もっと読む)

半導体集積回路の回路設計方法、設計装置及び回路設計プログラム

【課題】ピーク電流を抑えつつ、クロックツリーの生成のやり直しを減らし、設計TATを短縮すること。

【解決手段】本発明の第1の態様にかかる半導体集積回路の回路設計方法は、一のクロックルートからクロックが分配される複数の順序回路の配置情報に基づき、当該複数の順序回路のそれぞれのクロック分配遅延時間を算出し、算出されたクロック分配遅延時間に応じて、複数の順序回路を、予め遅延時間の範囲を定義した複数のグループに組み分けし、グループごとに設定された基準遅延時間となるように、グループごとに当該グループに組み分けされた順序回路に対するクロックのクロックツリーを生成する。

(もっと読む)

MOSトランジスタのシミュレーションパラメータの抽出方法

【課題】ゲートとドレインとの重なり部分の容量であるゲートオーバーラップ容量を精度よく抽出する。

【解決手段】本発明の一態様に係るシミュレーションパラメータの抽出方法は、コンタクトプラグ数のみが異なる複数のレイアウトパターンのそれぞれについて、所定のバイアス電圧下におけるゲート−ドレイン間の容量を測定して真のゲートオーバーラップ容量を含む測定値を求め、コンタクトプラグとゲートとの間の寄生容量を求めるためのモデルパラメータを変化させてシミュレーションを行って得られるコンタクトプラグとゲートとの間のコンタクト寄生容量を測定値から減算することによりゲートオーバーラップ容量演算値を求め、当該ゲートオーバーラップ容量演算値がコンタクトプラグの数によらず略一定となるモデルパラメータにおける当該ゲートオーバーラップ容量演算値を真のゲートオーバーラップ容量として抽出する。

(もっと読む)

半導体集積回路の設計方法、設計装置およびプログラム

【課題】製造バラつきの下で、クロックスキューの最小化しつつ、クロック信号部での消費電力を最小化する半導体集積回路の設計方法、設計装置および、コンピュータプログラムを提供する。

【解決手段】メッシュ配線構造を駆動するバッファツリーを生成するグローバルクロック構造生成部104と、クロック素子の配置分布とクロックゲーティング構造を考慮してクラスタを生成するクロック素子クラスタ生成部106と、そのクラスタに含まれるクロック素子が属するゲーティッド回路にクロック信号を分配するゲーティングセルを複製して、クラスタを駆動するゲーティングセルとして挿入するゲーティングセル複製・挿入部107と、ローカルクロック構造生成部109と、タイミング解析結果に基づき、クロック素子クラスタを駆動するゲーティングセルの駆動能力を調整するゲーティングセル駆動能力調整部111と、を備える。

(もっと読む)

半導体装置の設計方法

【課題】クロストークノイズによるディレイ変動量を正確に測定する。

【解決手段】複数のインバータを奇数段直列に接続したリングオシレータROと、リングオシレータROの一部の配線(被害側配線)VICに沿って設けられる第1配線(加害側配線)AGGと、前記第1配線AGGに供給する第1パルスを発生するパルス発生回路PGENと、前記第1配線AGGと前記パルス発生回路PGENの間に接続された第1バッファ(加害ゲート)AGと、前記パルス発生回路PGENと前記第1バッファAGとの間に接続される第2配線を具備し、前記第1配線AGGと前記リングオシレータROの一部の配線VICとの間の距離は、前記第2配線と前記リングオシレータROの一部の配線VICとの間の距離より短くする。

(もっと読む)

161 - 180 / 946

[ Back to top ]