Fターム[5F064HH10]の内容

ICの設計・製造(配線設計等) (42,086) | 設計、製造における計算機技術 (6,629) | ソフトウェア(プログラム)関係 (5,214) | 評価、検査、試験、監視 (946)

Fターム[5F064HH10]に分類される特許

101 - 120 / 946

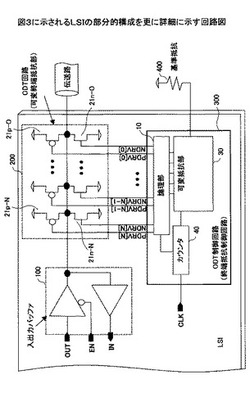

抵抗値補償方法、抵抗値補償機能を有する回路、回路の抵抗値試験方法、抵抗値補償プログラム、回路の抵抗値試験プログラム及びシステム

【課題】簡易で精度の高いODT回路の抵抗補償方式を提供することを目的とする。

【解決手段】複数のトランジスタの組み合わせによって所望の抵抗値と同等の抵抗値を実現するODT回路200であって、組み合わせるべきトランジスタを順次選択することにより、選択されたトランジスタによって実現される抵抗値を順次変化させる構成である。

(もっと読む)

半導体集積回路の設計方法

【課題】 半導体集積回路の電源EM及びスタティックIRドロップの解析と電源補強設計を改善する。

【解決手段】 一つの実施形態の半導体集積回路の設計方法では、電源配線のEM解析を行い、EM解析でEMエラーが発生した場合、EMエラーとなるレイヤ及び座標をチェックしてリストを格納し、半導体集積回路の抵抗網を抽出し、EMエラーとなるレイヤ及び座標を含む抵抗セグメントを全て削除してIRドロップ値が許容値を満足するかの第1の判定を行い、記第1の判定でIRドロップ値が許容値を満足する場合、EMによって半導体集積回路が動作不良とならない抵抗セグメントをレイアウトデータから削除する。

(もっと読む)

ダミーメタル配置評価装置、ダミーメタル配置評価方法及びダミーメタル配置評価プログラム

【課題】配線オブジェクトの敷設方向に対してずれを持たせたダミーメタルの配置を評価すること。

【解決手段】ダミーメッシュ情報作成部21は、配線オブジェクトの方向に対してずれを設けて規則的に配置したダミーメタルのブロック群を、各メッシュ内のダミーメタルの配置が同一となるようにメッシュ形状に分割する。重複判定部23は、分割によって得られた複数のダミーメッシュについて、配線オブジェクトとメッシュ内のダミーメタルのブロックとの重複を判定する。判定の結果、配線オブジェクトと重複するダミーメタルのブロックを除去したダミー情報をダミー情報算出部25が算出し、情報統合部26が配線オブジェクトの情報と統合する。評価部27は、統合したダミー挿入後の回路レイアウトが設計基準を満たすかを評価する。

(もっと読む)

情報処理装置、プログラム、および設計支援方法

【課題】設計対象の集積回路内での回路特性のばらつきに伴う遅延時間の変動を反映したタイミング解析技術を提供する。

【解決手段】情報処理装置は、複数の回路素子を含む対象経路の信号伝搬時間を変化させる物理特性値を所定の変動範囲で複数個発生させる物理特性値発生部と、発生させた物理特性値にしたがって、回路素子を通る信号の遅延時間を算出する素子遅延算出部と、信号の遅延時間を基に対象経路の信号伝搬時間を算出する伝搬時間算出部と、を備える。

(もっと読む)

半導体装置及びその検査方法並びにその設計方法

【課題】不良箇所を容易に特定し得る半導体装置及びその形成方法並びにその設計方法を提供する。

【解決手段】配線パターン32aと、ダミーパターン32bと、一方の端部が配線パターンに電気的に接続され、他方の端部がダミーパターンに電気的に接続されたヒューズ32cとを有している。

(もっと読む)

半導体装置のシミュレーション方法及び装置

【課題】電気特性と熱特性の相互の影響を反映した電気-熱連携解析を短い計算時間で実行し、正確な解析結果を得る半導体装置のシミュレーション方法及び装置を提供する。

【解決手段】まず電気特性解析を実行する(ステップS1)。次に電流特性とチップ損失特性の平均化を実行する(ステップS2)。そしてモジュールの3次元形状モデルを作成し、第1の平均化式により得た平均化した電流値を3次元形状モデルの端面に設定してジュール損失解析を実行する(ステップS3)。そして上記ジュール損失解析と第2の平均化式で算出したチップ損失の平均値とを用いて発熱量が等しく時間ステップの長い熱解析特性データを得る(ステップS4)。温度変化が一定値以上に達した時点で電気特性解析のジャンクション温度を再設定し(ステップS5)、以降、電気特性解析から平均化、熱解析までの解析フローを繰り返して装置動作時の温度特性を得る(ステップS11〜S15)。

(もっと読む)

半導体集積回路の設計装置および設計方法

【課題】回路規模の増大を抑制しつつスキャンテスト時の消費電力を削減する半導体集積回路の設計装置および設計方法を提供する。

【解決手段】対象抽出部102は、組み合せ回路のうちの活性化状態が評価される対象となる回路部分を抽出する。削減量算出部104は、組み合せ回路に入力されるスキャンフリップフロップのそれぞれの出力信号を1個ずつ固定化してスキャンフリップフロップ毎の消費電力の削減量を算出し、評価部108は、その結果に基づいて、スキャンフリップフロップの出力信号を固定化したときの消費電力の削減量が最も多いスキャンフリップフロップを選択する。固定化情報蓄積部106は固定化情報を保持し、対象抽出部102はその固定化情報に基づいて、評価対象となる回路部分を抽出する。評価部108は、抽出された回路部分毎に1つのスキャンフリップフロップを選択し、削減できる消費電力値の合計が所定の値になるまで上記を繰り返す。

(もっと読む)

半導体装置の設計方法、設計支援装置

【課題】ランプアニール工程での基板の温度ばらつきを抑制する。

【解決手段】半導体チップ(22)に導入、配置される複数の回路ブロック(A1〜E6)の初期レイアウト(31)を決定する。複数の回路ブロック(A1〜E6)の各々に対し、製造時にアニール用光源から照射される光の影響を受ける受光面を特定する。複数の回路ブロック(A1〜E6)の各々の面積に対する受光面の面積の比率を、受光面積率として算出する。初期レイアウトを、面積が均等な複数の領域の集合(A1〜E6、A2’、B2’、C5’、C6’、D5’、D6’、E3’、E4’)として特定する。基準ブロックの周辺の領域を周辺ブロックとして特定し、基準ブロックの受光面積率と周辺ブロックの受光面積率との和を周辺和とする。複数の領域の各々の周辺和のばらつきが最小となるように、複数の回路ブロックのレイアウトを変更する。

(もっと読む)

半導体装置のレイアウト検証方法と装置及びプログラム

【課題】Diffusionラウンディングの影響を防ぐためにトランジスタの特性変動量を定量的に考慮した最適な設計基準に基づく設計の検証を可能とする方法の提供。

【解決手段】拡散層1において第1の辺3と第2の辺4で確定されるコーナー部に形成されるDiffusionラウンディング5の形状を数式で表現し、コーナー部に隣接するゲート幅WのトランジスタTrに関して、第2の辺とゲートの間隔をX1とし、Diffusionラウンディングによるゲート幅の誤差をΔWとし、Diffusionラウンディングの形状パラメータとΔWとX1の関係と、トランジスタTrの特性変動率とゲート幅の変動率の関係とから、第2の辺とゲートの間隔X1の設計基準値を導出し、レイアウト情報からコーナー部に隣接して配設されるトランジスタのゲートと第2の辺の間隔を抽出し、抽出したゲートと第2の辺の間隔が、基準値を満たすか否か判定する。

(もっと読む)

回路モデル生成装置

【課題】 本発明の課題は、素子データを含むアナログ回路モデルを生成することを目的とする。

【解決手段】 上記課題は、回路図データとレイアウトデータとを格納する記憶領域と、前記レイアウトデータから寄生素子に係る素子データを抽出する抽出手段と、前記回路図データに前記素子データを含む回路モデルをハードウェア記述言語によって生成する回路モデル生成手段とを有する回路モデル生成装置により達成される。

(もっと読む)

集積回路設計装置及び集積回路の設計プログラム

【課題】設計作業に要する時間を短くすることができる集積回路設計装置及び集積回路の設計プログラムを提供すること。

【解決手段】本発明は、記憶部1、レイアウト部2、演算部3及び表示部4を有する。記憶部1は、ゲートレベルネットリスト11、タイミング制約12及び遅延テーブル13が予め記憶される。遅延テーブル13は、回路に配置されるセルのファンアウト数及びセルに接続される配線の長さに対応する最小の遅延が格納される。レイアウト部2は、ゲートレベルネットリスト11及びタイミング制約12に基づきセルレイアウトを生成し、それぞれのセルのファンアウト数とセルに接続される配線の長さとを算出する。演算部3は、算出したファンアウト数及び配線の長さに対応する遅延を遅延テーブル13から読み出し、セルレイアウトがセットアップタイムを満たすか否かの検証を行う。表示部4は、検証結果14を視認可能な状態で表示する。

(もっと読む)

基板ノイズ解析装置

【課題】 本発明の課題は、被ノイズ回路において影響を受けるノイズの大きさに基づいて効率的に基板ノイズ解析を行うことを目的とする。

【解決手段】 上記課題は、導体集積回路の回路ブロック毎に該回路ブロックの回路データを用いてノイズ源解析を行い、各周波数と該周波数に対するノイズ量とを対応させたノイズ源情報を出力するノイズ源解析手段と、回路ブロック毎に該回路ブロックの回路データを用いて各周波数に対して出力ノードから出力される該周波数の振幅をノイズの影響の大きさを示す感度として解析するノイズ感度解析を行い、各周波数と該周波数に対する感度とを対応させたノイズ感度情報を出力するノイズ感度解析手段と、前記ノイズ源情報と前記ノイズ感度情報とに基づいてノイズを受ける被ノイズ回路の動作に影響を与える周波数成分を特定し、該ノイズ源情報から該周波数成分を抽出するノイズ源情報抽出手段とを有する基板ノイズ解析装置により達成される。

(もっと読む)

LSIの電源遮断領域拡張方法及びそのプログラム

【課題】LSIにおける電源遮断領域を拡張する方法及びそのプログラムを提供する。

【解決手段】回路要素とネット情報とを記述したハードウエア記述ファイルに対して,電源遮断領域の入力端子Aから第1のノードBであるラッチ回路または入力ポートをトレースによって抽出し,さらに,遮断領域の出力端子に接続される第1のアイソレーションセルの出力端子A’から第2のノードB’であるラッチ回路または出力ポートをトレースによって抽出する第1の抽出工程と,第1のノードBから第3のノードCとなるラッチ回路または出力ポートをトレースによって抽出し,さらに,第2のノードB’から第4のノードC’であるラッチ回路または入力ポートをトレースによって抽出する第2の抽出工程とにより,無駄に動作する組み合せ回路を抽出し、前記回路をハードウエア記述ファイルと電源仕様ファイルに追加するとともに,アイソレーションセルを移動する工程とを有する。

(もっと読む)

設計ライブラリデータベース

【課題】結晶化半導体薄膜に対して適正かつ効率的なフォトマスクの作成を可能にする。

【解決手段】1実施形態に係る設計ライブラリデータベースは、2次元的に区画して各々薄膜トランジスタのチャネル領域のサイズを超える複数の結晶粒規定領域が配置された結晶化半導体薄膜を用いる薄膜トランジスタ回路の設計ライブラリデータベースであって、各々のチャネル領域が単一の前記結晶粒規定領域内の固定位置に配置される2個以上の薄膜トランジスタおよび前記2個以上の薄膜トランジスタを相互接続する配線を含む様々な論理ゲート回路をそれぞれ表す複数のスタンダードセル、並びに前記様々な論理ゲート回路の様々な組み合わせをそれぞれ表す複数のマクロセルの少なくとも一方のセルのライブラリ、および前記複数の結晶粒規定領域が配置された結晶化アレイパターンのスタンダードセルのライブラリを含みハードディスクに登録される。

(もっと読む)

電源回路解析装置,電源回路解析プログラムおよび電源回路解析方法

【課題】電源回路解析を、高速かつ少ないメモリ使用量で高精度に行なえるようにする。

【解決手段】解析対象回路における電源回路の解析対象領域を複数の分割領域に分割する分割部11と、この分割部11によって分割された各分割領域での消費電流値と各分割領域で上下層の電源配線を接続すべく各層間に形成されたビアのホール数とに基づき電源回路を分割領域毎に解析する解析部12とをそなえる。

(もっと読む)

回路設計装置、回路設計プログラム及び回路設計方法

【課題】効率的且つ十分に低消費電力化を行なうことを課題とする。

【解決手段】回路設計装置は、回路に含まれるFFのうち、動作していないFFを抽出し、抽出されたFFに対する制御信号の出力元である無動作起因端子を探索する。また、回路設計装置は、無動作起因端子が同一となるFFを1つのドメインとしてドメイン化し、ドメイン化されたFFそれぞれについてバックトレースを実施する。また、回路設計装置は、バックトレースにおいてFFに到達するまでに存在する組み合わせ回路を抽出する。また、回路設計装置は、到達したFFのうち同一ドメインでないFFそれぞれについてフォワードトレースを実施し、到達したFFが同一ドメインである場合に該当する組み合わせ回路も同一ドメインとしてドメイン化する。

(もっと読む)

回路シミュレーション方法および回路シミュレーション装置

【課題】精度の高い回路シミュレーションを実行する回路シミュレーション方法を提供する。

【解決手段】ゲートレベルでの電圧変動解析ステップを実行する(ステップS2)。ゲートレベルでの電圧変動解析ステップは、チップTP全体に対して実行する。そして、次に、電圧変動解析ステップに従う電源電圧および接地電圧(Vss)の電圧波形を取得するステップを実行する(ステップS4)。次に、トランジスタレベルでの信号解析ステップを実行する(ステップS6)。トランジスタレベルでの信号解析解析ステップは、チップTP全体よりも範囲の狭い例えば、すべてではない、1つ又はそれ以上の機能モジュールに対して実行する。そして、信号解析ステップに従う信号解析結果を取得するステップを実行する(ステップS8)。

(もっと読む)

遅延解析プログラム,遅延解析装置および遅延解析方法

【課題】多入力セルにおいて同時スイッチングが発生している可能性の有無を高速に判定し、同時スイッチングを考慮した遅延要因の解析を高精度かつ高速に行なえるようにする。

【解決手段】遅延試験時に信号が伝播した活性化パスが複数存在する場合、抽出部11により2以上の活性化パスが入力されている多入力セルが抽出される。抽出された多入力セルについて、判定部12により、2以上の活性化パスにおける各信号の多入力セルへの入力タイミングに基づき、多入力セルにおいて同時スイッチングが発生している可能性の有無が判定される。そして、解析部13により、判定部12による判定結果および遅延試験の結果に基づき、同時スイッチングの発生状況が遅延要因の一つとして解析される。

(もっと読む)

アサーションベース検証装置、およびアサーションベース検証方法

【課題】大規模で複雑化した半導体集積回路に対する機能検証を効率よく実行しつつ、検証対象の半導体集積回路の品質を向上させる技術を提供する。

【解決手段】論理シミュレーション実行部(15)(17)の機能によって、制御可アサーション記述ファイル(25)の、処理対象アサーション記述と処理非対象アサーション記述とを特定する。処理対象アサーション記述を用いてDUT(22)に対するアサーションベース検証を実行しつつ、発火条件を満足したか否かを判定した結果に基づいて発火情報レジスタ(28)を書き換える。発火情報レジスタ(28)のデータに基づいてアサーション制御情報(27)を更新して新たなアサーション制御情報(27)とし、新たなアサーション制御情報(27)を用いてアサーションベース検証を実行する。

(もっと読む)

レイアウト検証装置及びレイアウト検証方法

【課題】素子と配線、配線と配線の交差部分の耐圧を検証することができるレイアウト検証装置及びレイアウト検証方法を提供する。

【解決手段】レイアウト検証装置は、半導体集積回路の回路図データと、該回路図データに基づいて生成されたレイアウトデータとの整合性を検証する整合性検証手段と、整合性検証手段により整合性が検証された場合に、レイアウトデータに基づいて、互いに交差する位置関係にある素子と配線、又は、配線と配線がなす交差対を抽出する抽出手段と、判定基準となる基準電位差を記憶する記憶手段と、回路図データに基づいて、交差対の電位差を求める電位差検出手段と、交差対の電位差と基準電位差とを比較する電位差比較手段と、を備える。

(もっと読む)

101 - 120 / 946

[ Back to top ]