Fターム[5F064HH10]の内容

ICの設計・製造(配線設計等) (42,086) | 設計、製造における計算機技術 (6,629) | ソフトウェア(プログラム)関係 (5,214) | 評価、検査、試験、監視 (946)

Fターム[5F064HH10]に分類される特許

41 - 60 / 946

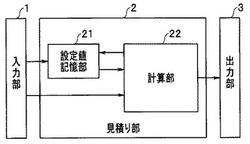

半導体集積回路のチップサイズ見積もり装置、及び半導体集積回路のチップサイズ見積もり方法

【課題】精度よく簡便にチップサイズを見積もることができる、半導体集積回路のチップサイズ見積もり装置、及び半導体集積回路のチップ見積もり方法を提供する。

【解決手段】回路の機能の実現に最小限必要なゲート数である最小機能ゲート数を入力する入力部1と、セルライブラリごとに所定の動作速度の達成に必要となるゲート数と前記最小機能ゲート数との比率である性能考慮ゲート数係数が予め設定された設定値保持部21と、前記最小機能ゲート数と前記性能考慮ゲート数係数とから算出されるゲート数を用いて前記回路の総面積を見積もる計算部22と、を備えたことを特徴とする。

(もっと読む)

レイアウト検証装置、レイアウト検証方法、及びプログラム

【課題】半導体集積回路のレイアウト検証であって、検証済のレイアウトパタンデータへ部分的に変更を加えた後で行うDRC検証において、検証の対象とならない箇所に対するDRC検証の時間を省略し、アンテナ比のようなDRC検証の時間を短縮する。

【解決手段】検証済のレイアウトパタンデータへ部分的に変更を加えた後で行うDRC検証において、変更箇所から等電位追跡を用いてDRC検証の検証対象箇所を特定する。具体的には、変更前後のレイアウトパタンデータの差分図形を抽出して該差分図形から変更ノードを抽出する。また、変更後のレイアウトパタンデータに対して等電位番号を付与して該等電位番号を参照して該変更ノードと同じ等電位番号を持つ検証対象箇所を抽出する。更に、前抽出された記検証対象箇所に対して、アンテナ比のDRC検証を実行する。

(もっと読む)

半導体装置における電流による配線破壊箇所の予測方法

【課題】半導体装置の電流による配線破壊箇所の予測方法において、解析時間を短縮する。

【解決手段】下層配線14A,14Bをそれぞれ一つの直列抵抗で、第1の下層ビア15A,第2の下層ビア15Bを1個の抵抗で、第1の上層ビア17A、第2の上層ビア18Bを1個の抵抗で、第1及び第2の上層配線16A,16Bを抵抗ブリッジ回路で、パワートランジスタTRを直列抵抗で、それぞれモデリングしてなる解析モデルをモデリング用計算機により生成する。回路シミュレータ3により、解析モデルにおけるパワートランジスタTRに電流を供給し、解析モデルにおける各抵抗に流れる電流に基づいて、第1及び第2の下層配線14A,14B、第1及び第2の上層配線16A,16Bにおける各抵抗の電流密度を計算し、各抵抗の電流密度と、配線破壊を起こす電流密度閾値とを比較器4により比較することにより、配線破壊箇所を予測する。

(もっと読む)

半導体装置、半導体装置の設計方法、半導体装置設計装置、及びプログラム

【課題】より多くのI/Oセルを配置することができるようにする。

【解決手段】多層配線層には、電位供給用接続配線230が設けられている。電位供給用接続配線230は、平面視で外周セル列20を構成するI/Oセル200のいずれか、および内周セル列30を構成するI/Oセル200のいずれかと重なっている。そして電位供給用接続配線230は、外周セル列20の下方に位置する電源電位供給配線222を、内周セル列30の下方に位置する電源電位供給配線222に接続するとともに、外周セル列20の下方に位置する接地電位供給配線224を、内周セル列30の下方に位置する接地電位供給配線224に接続している。

(もっと読む)

レイアウト設計方法及びレイアウト設計装置

【課題】チップ面積を小さくすることのできるレイアウト設計方法を提供する。

【解決手段】レイアウト設計方法は、所定のタイミング制約F1を満足させるように、セルを配置し、低抵抗配線が形成される第1配線層を使用してセル間のパスの接続配線を形成する処理(ステップS2〜S4)を有する。また、レイアウト設計方法は、タイミング制約F1を満足させたまま、パスの接続配線のうち、セル間に配置されるバッファ回路によって区切られる複数のステージ中の少なくとも一つのステージに対応する接続配線におけるレシーバ側からの一部を、第1配線層から該第1配線層よりも配線遅延が大きくなる第2配線層に置き換えて形成する配線置換処理(ステップS5)を有する。

(もっと読む)

レイアウト設計方法、および、レイアウト設計プログラム

【課題】チップサイズを縮小する。

【解決手段】レイアウト設計方法は、レイアウト設計装置が、半導体集積回路のレイアウト設計を階層別に行う階層レイアウト設計における上位階層において、上位階層の下の階層で配置配線が行われる所定の機能を備えた階層ブロックが配置される領域であって、空きユニットセル配置領域3と階層ブロック用のユニットセル配置領域4とを含む階層ブロック配置領域2を、チップ領域1に設定し、チップ領域1における階層ブロック配置領域2を包囲する周辺領域5のユニットセル配置領域、および、階層ブロック配置領域2内の空きユニットセル配置領域3を用いて、配置配線を行う。

(もっと読む)

電源ノイズ解析方法

【課題】簡易モデルを使用しても、電源ノイズを高精度かつ高速で解析することのできる電源ノイズ解析方法を提供する。

【解決手段】実施形態の電源ノイズ解析方法は、スイッチング部モデル11と非スイッチング部モデル12とを備える簡易モデル1を用い、半導体集積回路のトグル率の時間軸上の変化を表すトグル率時系列データを生成するステップと、トグル率時系列データにもとづいて簡易モデル1の容量CL、Cnswの容量値の時間軸上の変化を表す容量値時系列データを生成するステップと、簡易モデル1および容量値時系列データを用いて電源ノイズの解析を行うステップとを有する。電源ノイズの解析を行うステップは、スイッチング部モデル11のスイッチSWのスイッチング区間ごとに容量値時系列データから該当区間の容量値を取得し、前区間の過渡解析の結果を引き継ぎながら次区間の過渡解析を実行する。

(もっと読む)

半導体集積回路のレイアウト装置、レイアウト方法及びそれらに用いられるセルデータ

【課題】タイミング違反を容易に解消して工数の増大を抑制すること等が可能な半導体集積回路のレイアウト装置を提供すること。

【解決手段】本発明にかかる半導体集積回路のレイアウト装置は、セルデータを記憶する記憶装置13と、記憶装置13からセルデータを読み出して自動配置配線を行うレイアウト部242と、を備える。また、セルデータは、ターゲットセルに対する配置の状況に応じた遅延をターゲットセルに対して付加する遅延考慮フィラーセルの情報を有する。

(もっと読む)

半導体装置

【課題】ドライバの故障による出力異常を救済することが可能な故障検出救済回路を含んだ半導体装置を提供すること。

【解決手段】故障検知部1は、ドライバ10の出力の期待電位の逆電位となるようにドライバ10の出力にプルアップ抵抗15またはプルダウン抵抗18を接続し、ドライバ10の入力電位と出力電位とを比較することによりドライバ10の故障を検出する。故障救済部2は、故障検知部1によってドライバ10の故障が検出された場合に、期待電位と同電位となるようにドライバ10の出力にプルアップ抵抗26またはプルダウン抵抗29を接続してドライバ10の故障を救済する。したがって、ドライバ10の故障による出力異常を救済することが可能となる。

(もっと読む)

ノイズ振幅評価方法、ノイズ振幅評価装置およびプログラム

【課題】トラップによって引き起こされる半導体集積回路の特性変位量を精度良く高速に求める。

【解決手段】半導体集積回路を構成するトランジスタ中のトラップの数を乱数により決定する工程(ステップS02)と、トラップの各々の属性値を乱数により決定する工程(ステップS03)と、トラップの集合の部分集合であって、部分集合に属するトラップがすべて同時に特性変動を起こした状態に遭遇する確率と、部分集合に属するトラップがすべて同時に特性変動を起こしたときに生じる半導体集積回路の特性変位量と、から所定の期間内に生じる半導体集積回路の特性変位量を推測する工程(ステップS04)と、を含む。

(もっと読む)

レイアウト検証装置及びレイアウト検証方法

【課題】汎用性が高く、効率的に検証処理を行うことができるレイアウト検証技術を提供する。

【解決手段】レイアウトデータがデザインルールに反するか否かの検証を行うに際し、所定の設計値に基づき、レイアウトデータ(1)を、擬似エラー領域内のものとそれ以外のものとに区分し、通常のデザインルール(4)からの許容範囲内のものとして擬似エラー領域用のデザインルール(13)を作成し、擬似エラー領域外のレイアウトデータについては通常のデザインルールで検証を行い、擬似エラー領域内のレイアウトデータについては擬似エラー領域用のデザインルールで検証を行う。

(もっと読む)

半導体集積回路の自動レイアウト方法

【課題】半導体集積回路の自動レイアウト設計において、必要な領域に対しては配線混雑の緩和を行い、かつ、不必要な面積増大を抑制する。

【解決手段】単位領域当たりのネットの数の上限をネット密度制約として設定する(ST105)。ネット密度制約を満たすようにセルを配置する(ST106)。セル配置工程(ST106)では、仮配置されたセルのレイアウトに対し、単位領域に存在する端子を抽出する。そして、抽出した端子に接続されるネットをネットリストを参照して抽出する。抽出したネットの数が前記ネット密度制約を満たすようにセルの配置を変更する。

(もっと読む)

半導体装置

【課題】多層配線構造を有する半導体装置にダミーパタンを配線空隙に効率よく製造容易的に形成する。

【解決手段】多層配線構造の半導体装置において、狭い配線空隙(Area_S1)に、広い配線空隙(Area_S2)に形成されたダミーパタン(22,23)と異なる向きのダミーパタン(21)が形成されている。

(もっと読む)

半導体集積回路の設計方法、設計プログラム、及び設計支援装置

【課題】半導体集積回路の設計TATを短縮する。

【解決手段】本発明による半導体集積回路の設計方法は、コンピュータ装置10によって実行される半導体集積回路の設計方法であって、論理セル500と配線セル400をチップ上に配置するステップと、論理セル500内のゲート505に対するアンテナルール122を配線セル400の第1アンテナ用ライブラリ101に追加することで、第1アンテナ用ライブラリ101を第2アンテナ用ライブラリ201に変更するステップと、配線セル400と他の論理セル510を第1配線550で接続するステップと、第2アンテナ用ライブラリ201に規定されたアンテナルール122に従い、ゲート505の面積に対する前記第1配線550の面積の比を検証する第1検証ステップとを具備する。

(もっと読む)

設計支援プログラム、該プログラムを記録した記録媒体、設計支援方法、および設計支援装置

【課題】半導体集積回路の長寿命化、および設計期間の短縮を同時に実現すること。

【解決手段】設計支援装置700は、検出部701により、レイアウト情報によって表現された設計対象回路から配線間を接続するビアを検出する。つぎに、決定部702により、配線間を接続しないダミービアの接続位置を、検出部701によって検出されたビアに接続された配線のうち、少なくとも一つの配線上の位置に決定する。そして、挿入部704により、決定部702によって決定された接続位置にダミービアを挿入する。

(もっと読む)

静的タイミング解析装置及び静的タイミング解析方法

【課題】静的タイミング解析の所要時間の短縮。

【解決手段】静的タイミング解析装置は、時刻関数生成部12と、スラック関数生成部13と、電源ドメイン電圧定数決定部14と、スラック値計算部15と、出力部16と、を備える。時刻関数生成部12は、ネットリストと、セルの遅延時間情報と、タイミング制約情報と、電源ドメインとその電源電圧範囲との対応関係を示す電源ドメイン情報とに基づいて、電源電圧の関数である、セルへの信号到着時刻を表す時刻関数を生成する。スラック関数生成部13は、タイミング制約情報及び時刻関数に基づいて、セルへの信号到着時刻の余裕度を示す電源電圧の関数であるスラック関数を生成する。電源ドメイン電圧定数決定部14は、電源電圧の下限電源電圧と上限電源電圧の間でスラック関数が最小となる電源電圧定数を決定し、スラック値計算部15は、スラック関数に電源ドメイン電圧定数を代入し、スラック値を計算する。

(もっと読む)

半導体装置の製造方法、半導体装置、設計方法、設計装置、及び、プログラム

【課題】集積度及び歩留まりの低下を抑制しつつ、アニール処理に起因した素子の特性ばらつきを軽減する。

【解決手段】半導体基板1上に素子2、3、5を形成する素子形成工程と、素子形成工程の後、半導体基板1上に、選択的に、半導体基板1よりも高い光吸収率を有するか、又は、半導体基板1への光の吸収率を向上させる機能を有する加熱安定化膜7を形成する加熱安定化膜形成工程と、加熱安定化膜7を有する面側から半導体基板1に光を照射し、半導体基板1に注入された不純物を活性化するアニール工程と、を有する半導体装置の製造方法。

(もっと読む)

回路設計検証装置および回路設計検証方法

【課題】回路シミュレーション用のネットリストに基づいて、当該回路のファンアウトを計算できるようにすること。

【解決手段】回路設計検証装置は、半導体素子レベルの回路シミュレーション用のネットリストを、論理を構成する複数の駆動回路に分割するネットリスト分割部と、前記複数の駆動回路のそれぞれに含まれるMOSトランジスタのゲート長およびゲート幅からゲートサイズを算出するゲートサイズ算出部と、前記複数の駆動回路のそれぞれによって駆動される後段の素子の負荷容量を算出する負荷容量算出部と、算出されたゲートサイズおよび算出された負荷容量に基づいて、前記複数の駆動回路のそれぞれに対するファンアウトを算出するファンアウト算出部と、を備えている。

(もっと読む)

パターン作成方法および半導体装置の製造方法

【課題】高歩留まり且つ低コストで半導体装置を製造することができるパターン作成方法を提供すること。

【解決手段】実施形態によれば、パターン作成方法が提供される。パターン作成方法では、設計パターンに応じた基板上パターンを形成できるよう前記基板上パターンに応じたマスクパターンを作成する際に、前記設計パターン間が満たす必要のある相対関係に基づいて、前記設計パターン間に対応するマスクパターン間が前記相対関係を満たすよう前記マスクパターンを作成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チップ面積を増大させることなく、針ずれに起因する誤測定や誤検査を防止することができる、半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、内部回路と、内部回路と電気的に接続されるとともに、検査装置に接続された複数の探針がそれぞれ接触する複数のパッドを備える。少なくとも2つのパッド2a、2bの間に、当該2つのパッド2a、2bを電気的に接続するとともに、所定の電流を印加することにより、恒久的に、電気的に切断されるヒューズ素子4が設けられる。パッド2a、2bの間の抵抗値を測定することで、針ずれの有無を検知することができる。その後、ヒューズ素子を切断し、内部回路の検査が実施される。

(もっと読む)

41 - 60 / 946

[ Back to top ]