Fターム[5F064HH10]の内容

ICの設計・製造(配線設計等) (42,086) | 設計、製造における計算機技術 (6,629) | ソフトウェア(プログラム)関係 (5,214) | 評価、検査、試験、監視 (946)

Fターム[5F064HH10]に分類される特許

141 - 160 / 946

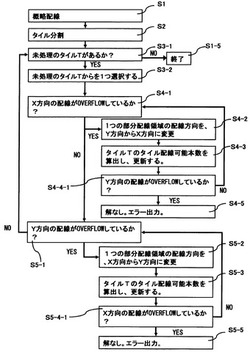

基板の配線設計方法及びプログラム

【課題】配線設計において、簡易的に配線混雑を回避することが可能な配線設計方法を提供することを目的とする。

【解決手段】複数の第1方向配線の配線層及び複数の第2方向配線の配線層を備える基板対して概略配線を行い、基板を複数のタイルに分割し、複数のタイルに対応するように、複数の第1方向配線の配線層及び複数の第2方向配線の配線層を分割して、複数の第1方向配線の部分配線領域と、複数の第2方向配線の部分配線領域と、を形成し、タイルにおける第1方向配線がオーバーフローしている場合には、このタイルに対応する第2方向配線の部分配線領域を、第1方向配線の部分配線領域に変更する。

(もっと読む)

レイアウト設計装置、レイアウト設計方法、及びレイアウト設計プログラム

【課題】

複数階層を有する半導体集積回路の階層レイアウトを行なう際に、複数個所で使用される下位モジュールについての各配置箇所における下位モジュール近傍の上位階層の配線状況を考慮して、下位モジュールのレイアウト設計を行なうことを課題とする。

【解決手段】

上記課題を解決するために、本発明に係るレイアウト設計装置は、複数階層を有する半導体集積回路のレイアウト設計装置であって、複数個所で使用される下位モジュールについて、前記下位モジュールが配置される上位モジュール内のそれぞれの配置箇所近傍の上位階層の配線情報を抽出し、抽出した上位階層の配線情報を、前記下位モジュールのレイアウト設計を行なう際の配線禁止領域として設定し、前記下位モジュールのレイアウトを行なう。

(もっと読む)

半導体装置の電源配線レイアウト方法及び電源配線レイアウト装置

【課題】IRドロップ違反を解消しつつ、半導体集積回路の大型化を抑制することができる半導体装置の電源配線レイアウト方法。

【解決手段】半導体集積回路の電源配線レイアウト方法。電源配線を、複数のノードと、互いに隣接するノード間に配置された複数の要素抵抗と、を含む解析モデルとしてモデル化し、回路シミュレーションにより各複数のノードにおける電圧値を求める。電圧値にIRドロップ違反がある場合、IRドロップ違反が最大となるノードへ流れ込む電流経路を探索し、複数の要素抵抗のうち、電流経路に含まれる要素抵抗からボトルネック要素抵抗を選択し、その抵抗値を変更する。

(もっと読む)

半導体集積回路及び半導体集積回路の電源スイッチ制御方法

【課題】電源スイッチを非導通状態から導通状態に遷移させる時間を最適化できる半導体集積回路及びその電源スイッチ制御方法を提供する。

【解決手段】共通電源配線と、第1の回路と、それぞれ電源スイッチ制御信号に基づいて導通、非導通が制御され共通電源配線と第1の回路との間を並列に接続する複数の電源スイッチと、電源スイッチ制御信号と複数の電源スイッチとの間に接続され電源スイッチ制御信号が非導通状態から導通状態に遷移するときに電源スイッチ制御信号の遷移をそれぞれ異なった遅延時間だけ遅延させて複数の電源スイッチに伝え複数の電源スイッチをそれぞれ時間をずらして非導通状態から導通状態に遷移させる遅延回路と、各遅延回路の遅延時間の増減を制御する遅延時間制御部と、を備える。

(もっと読む)

回路シミュレータおよび半導体装置の設計方法

【課題】インパクトイオン化電流の算出精度を向上させる。

【解決手段】飽和ソース−ドレイン電圧Vdsatがソース−ゲート電圧Vgsおよびソース−ドレイン電圧Vdsの関数にて与えられたドレイン横方向電界Edの計算式に基づいて電界効果トランジスタのインパクトイオン化電流Iiiを計算する。

(もっと読む)

プログラマブル論理回路装置及び画像処理装置

【課題】 節電効率を向上させることができるプログラマブル論理回路装置及び画像処理装置を提供する。

【解決手段】 本発明のプログラマブル論理回路装置100は、素子間の接続の変更により再構成される回路を備える複数の再構成領域R0、R1、R2、R3及びR4と、複数の再構成領域R1、R2、R3及びR4の各々に対して、実行させる処理を割り当てて、複数の再構成領域R1、R2、R3及びR4の各々が実行する処理の状態に基づいて、複数の再構成領域R1、R2、R3及びR4を選択的に再構成して節電状態にする管理領域である再構成領域R0と、を有する。

(もっと読む)

解析装置及び半導体装置

【課題】 本発明の課題は、複数段の電源スイッチを段階的にオンすることによって内部回路に電源供給する半導体装置において、電源供給開始から起動可能となるまでの復帰時間を短縮することを目的とする。

【解決手段】 上記課題は、複数段の電源スイッチを段階的にオンすることによって内部回路に電源供給する電源供給回路を解析する解析装置であって、前段までの電源スイッチをオン状態とし、オンすることによって発生する許容ノイズ量を超えない最大電源ノイズ量となる電源スイッチサイズを次段の電源スイッチとして決定する電源スイッチサイズ決定手段と、前記次段の電源スイッチサイズによる電源ノイズが前記オンされてから収束判定量以下となるまでの時間をオン時間間隔として決定するオン時間間隔決定手段とにより達成される。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法及びプログラム

【課題】半導体集積回路において、シールド配線を配置することで配線間のクロストークの影響を削減するとともに、配置したシールド配線の電位を安定化させること。

【解決手段】半導体集積回路の設計方法は、コンピュータが、半導体集積回路の配線パターンにおいて、配置済の信号配線に対して複数のシールド配線を配置する工程と、前記複数のシールド配線のそれぞれを電源配線に接続する工程と、前記複数のシールド配線を相互に接続する工程と、前記複数のシールド配線のうちの電源配線に接続されていないものを除去する工程と、を含む。

(もっと読む)

ガードリング設計装置、ガードリング設計方法、プログラム及び記録媒体

【課題】半導体集積回路の素子及び配線のレイアウトにおけるガードリングの設計の自由度を高める。

【解決手段】設計装置は、デザインルールを記憶するデザインルール記憶部11、予め設計されたレイアウトを記憶するレイアウト記憶部12、デザインルールに適合したガードリング幅を設定幅として設定するガードリング幅設定部21、レイアウト上にガードリングの形成経路を指定するための経路指定部32、指定経路に基づいてガードリング形成経路を認識する経路認識部22、ガードリング形成用のレイヤーリストを記憶するガードリング形成用レイヤー記憶部13、認識経路の下地レイヤーに応じたガードリング形成用のレイヤーを設定するガードリング形成用レイヤー設定部23及び認識経路に設定幅で設定レイヤーを反映させてガードリングを生成するガードリング生成部24を備えている。

(もっと読む)

半導体回路の設計装置および設計方法

【課題】配線のしやすさを損なうことなく、ビアの不良による歩留まりの低下を抑制可能な半導体回路の設計装置および設計方法を提供する。

【解決手段】半導体回路の設計方法は、論理回路を構成するセルの配置およびセル間の配線を行い、複数箇所にビアが設けられる配線を含むレイアウトパターンを生成するステップ(ステップS1、S2)と、ビアから、配線上の信号を受信するレシーバセルまでの負荷容量をビア毎に算出するステップ(ステップS4)と、ビアごとの、負荷容量に基づいて、負荷容量が大きいビアを優先的に低抵抗のビアに置換するステップ(ステップS6、S7)を備える。

(もっと読む)

応力発生膜を含む半導体装置の製造方法、および設計方法

【課題】応力発生膜の形状に依存して、半導体装置製造時の半導体装置の回路部品の特性がマクロセル設計段階での半導体装置の回路部品の特性から変動することを極力抑制する。

【解決手段】応力発生膜の延在方向の寸法の変更量に対する、半導体装置の特性の変化量が所定の限度で飽和する延在方向の寸法を目標延在寸法として設定する工程と、半導体装置内で応力発生膜の末端からゲートに至るまでの寸法が少なくとも目標延在寸法となるように応力発生膜を形成する工程とを含む。

(もっと読む)

品質優先回路抽出装置、品質優先回路抽出方法、品質優先回路抽出プログラム、マスク作成システム、及びレイアウト制約作成システム

【課題】レイアウト上での素子配置の規則性情報と組み合わせて、差動対回路やカレントミラー回路のようなマスク検査品質を優先する部分回路の抽出を図ること。

【解決手段】品質優先回路ネットリスト抽出装置3で抽出した品質優先回路のネットリスト情報(差動対回路、カレントミラー回路)と品質優先回路レイアウト抽出装置5で抽出した品質優先回路のレイアウト情報(行/列/アレイ構造)から、レイアウトデータに含まれる素子図形に対してマスク検査精度の優先順位を決定する。

(もっと読む)

半導体集積回路、ならびに、その設計方法および製造方法

【課題】ダミー回路を備えることなく、設計時や製造時においても、配線パターンのみの変更によりFFにおけるホールドエラーを解消することができる半導体集積回路、ならびに、その設計方法および製造方法を提供する。

【解決手段】本発明の半導体集積回路は、第1および第2のフリップフロップセルを含む複数のスタンダードセルからなるものである。第1および第2のフリップフロップセルは、同一の寸法のそれぞれの領域内に共通のトランジスタ配置パターンで配置された複数のトランジスタを有するとともに、複数のトランジスタを相互に接続してフリップフロップ回路を構成する互いに異なる配線パターンの配線を有し、それぞれの領域内の同一の位置に配置された同一の寸法の少なくとも1個のトランジスタを、回路的に異なる位置に使用したフリップフロップ回路を構成するセルである。

(もっと読む)

半導体集積回路のレイアウト装置及びレイアウト方法

【課題】集積度の高い半導体集積回路の場合でもレイアウト設計における配線に係る時間を短縮する。

【解決手段】半導体集積回路のレイアウト方法は、回路構成要素の配置された領域へ配線を実施後に、予め設定された条件よりも配線が混雑する配線混雑箇所を抽出するステップと、配線混雑箇所を含む領域に、配線の実施が禁止される複数の配線禁止領域を生成するステップと、複数の配線禁止領域を迂回して配線を実施するステップと、迂回して配線を実施した後に、複数の配線禁止領域を削除するステップと、複数の配線禁止領域を削除した後に、再配線を実施するステップとを具備する。複数の配線禁止領域を生成するステップは、配線層毎に、配線の混雑に対応した領域内に配線禁止領域を発生させる割合に基づいて、複数の配線禁止領域の大きさ及び間隔を算出するステップと、算出結果に基づいて、領域に複数の配線禁止領域を生成するステップとを備える。

(もっと読む)

多電源集積回路設計装置およびその方法、ならびに、多電源集積回路製造方法

【課題】異電源ドメイン間におけるタイミング収束性が改善された回路設計を容易に行うことができる多電源集積回路設計装置の提供。

【解決手段】回路構成情報および電源構成情報に基づいて、異電源ドメインと接続するデータパスに対し、最初および最後に接続される同期式フリップフロップである境界FFの少なくともいずれかを抽出して、境界FFデータとして出力する境界FF抽出部と、回路構成情報および境界FFデータに基づいて、境界FFに接続されたクロックラインに配されたバッファを抽出し、入力を分岐させて当該分岐を入力とする新たなバッファを追加するバッファ追加部と、境界FFが新たなバッファに接続されるようにクロックラインを繋ぎ換えるように、回路構成情報を変更して、変更された回路構成情報のデータを出力するクロックライン再構成部と、を有する多電源集積回路設計装置。

(もっと読む)

半導体設計支援装置

【課題】高位設計手法ではない既存の設計手法にて設計されたブロックに対してもレイテンシ調整を可能とする。

【解決手段】回路記述情報を読み込み、遅延調整のために必要な情報を生成する半導体設計支援装置であって、前記回路記述情報に基づき論理シミュレーションを実施して論理シミュレーション結果情報を出力する論理シミュレーション手段と、前記論理シミュレーション結果情報から信号合流点における複数ブロックの信号の遅延量情報を求める遅延量情報取得手段と、前記遅延量情報から遅延調整のために必要な調整遅延量情報を計算する調整遅延量計算手段と、前記調整遅延量情報から遅延調整のために必要な調整遅延情報を生成する調整遅延情報生成手段とを備える。

(もっと読む)

パス調整方法及び設計支援装置

【課題】設計期間の短縮化を図ること。

【解決手段】設計支援装置は、クロックツリー合成処理(ステップ23)にて生成したクロックツリーに含まれるクロックパスについて、電圧・温度の遅延感度をそれぞれ算出し、2つのクロックパスの遅延感度の差を0に近づけるように、クロックパスの遅延感度を調整する。

(もっと読む)

マスクレイアウト作成方法、マスクレイアウト作成装置、リソグラフィ用マスクの製造方法、半導体装置の製造方法、およびコンピュータが実行可能なプログラム

【課題】コヒーレンスマップ法を使用して補助パターンを作成する場合に、その配置精度を向上させることが可能なマスクレイアウト作成方法を提供する。

【解決手段】リソグラフィ工程で危険点となる可能性の高い設計レイアウトを設定し、設定した設計レイアウトに対して、マスクレイアウトを生成するコヒーレンスマップカーネルを設定し、設定されたコヒーレンスマップカーネルと設計レイアウトとに基づいて、コヒーレンスマップを作成し、コヒーレンスマップから補助パターンを抽出・整形してマスクレイアウトを生成し、マスクレイアウトの最適度を評価するコスト関数COSTを定義し、当該コスト関数を使用して、生成したマスクレイアウトを評価し、コスト関数で評価されるマスクレイアウトが最適となるまで、コヒーレンスマップカーネルのパラメータおよびコヒーレンスマップから補助パターンを抽出・整形する際のパラメータの少なくとも一方を変更する。

(もっと読む)

半導体集積回路装置、設計方法、設計装置、およびプログラム

【課題】チップの面積をより小さくする。

【解決手段】アンテナ比演算部12は、レイアウトデータ蓄積部11から読み出したレイアウトデータに基づいて一の拡散層領域に2以上の独立した金属配線が接続されている構成要素を抽出し、この構成要素に対し、2以上の独立した金属配線のそれぞれの面積と、それぞれの金属配線に接続されるそれぞれの電極の面積とを求め、それぞれの金属配線の面積とそれぞれの金属配線に接続される電極の面積とのアンテナ比をそれぞれ求め、一の金属配線の面積に対する、一の拡散層領域に接続される全ての金属配線の総面積の比に基づいて、一の金属配線に係るプラズマチャージダメージに関する設計基準の緩和値を求める。レイアウト検証部13は、一の金属配線に対応するアンテナ比に対し、一の金属配線に係る緩和値で緩和された設計基準によって検証する。

(もっと読む)

設計支援方法

【課題】開発期間の短縮を図ること。

【解決手段】設計支援装置は、実回路レイアウト25から認識したデバイスのレイアウトデータについて、そのデバイスを含む所定領域内の着目パターンのエッジを格子分割し、各格子に含まれるエッジの有効無効を判定する。次に、設計支援装置は、判定結果に応じて着目パターンに対する形状情報を含む格子テーブルを生成する。そして、設計支援装置は、評価レイアウト22に基づいてエッジ位置に対するデバイスの特性変動に対応する重み付け情報を格子位置に関連付けた形状依存テーブル24と、格子テーブルとに基づいてデバイスの形状に応じた特性変動量を算出する。

(もっと読む)

141 - 160 / 946

[ Back to top ]