Fターム[5F083AD00]の内容

半導体メモリ (164,393) | DRAM (5,853)

Fターム[5F083AD00]の下位に属するFターム

読出しトランジスタ (1,433)

キャパシタ (3,513)

1MOSトランジスタ+1Cap以外のDRAM (506)

Fターム[5F083AD00]に分類される特許

161 - 180 / 401

半導体記憶装置

【課題】不良解析の際に、メモリセルのレイアウトを制限したり、工程数を増加することなく、メモリセル数を数えやすくすること。

【解決手段】半導体基板2上にメモリセル3aの繰り返しパターンが形成されたメモリセルアレイ領域3を有し、メモリセルアレイ領域3上に形成された所定層の電源配線4a、接地配線4bを、少なくともメモリセルアレイ領域3において、メモリセル3aの配置と対応させて縦方向及び横方向に格子状にレイアウトしている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の動作不良を防止し、半導体装置の製造工程を簡略化する。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1と、半導体基板1内に設けられる一対の不純物拡散層2A,2Bと、不純物拡散層2A,2B間の半導体基板上に設けられるゲート絶縁膜3と、ゲート絶縁膜3上に設けられるゲート電極4と、一対の不純物拡散層2A,2B上にそれぞれ設けられる2つのコンタクト5A,5Bとを具備し、ゲート電極4とコンタクト5A,5Bは、同じ材料から構成され、ゲート電極4上端およびコンタクト5A,5B上端は、半導体基板1表面からの高さが一致する。

(もっと読む)

半導体記憶装置

【課題】メモリアレイ領域上に信号線を配設した場合に、信号線のノイズ成分の影響により、誤動作が生じるのを防止する。

【解決手段】メモリアレイ領域11において、ビット線BL0〜BL5はY方向に延びており、ワード線WL0〜WL2、ソース線SL1〜SL3はY方向と直交するX方向に延びている。ビット線BL0〜BL5とワード線WL0〜WL2の各交差点に対応して、メモリセルMCが配置されている。電源線18Aは、メモリアレイ領域11上に形成され、ビット線BL0〜BL5、ワード線WL0〜WL2及びソース線SL1〜SL3に対して斜めに交差している。ここで、3層メタル構造が採用され、ビット線BL0〜BL5は第1メタル層で、ワード線WL0〜WL2及びソース線SL1〜SL3は、その上層の第2メタル層で、電源線18Aはその上層の第3メタル層で形成されている。

(もっと読む)

HOTデバイスのためのSOI/バルク境界のSTI構造

【課題】複数のHOT領域を分離する複数のSTIを備えた半導体装置において。境界領域の複数のSTIのミスアラインメントによるボイドを排除する製造方法を提供する。

【解決手段】基板400上にBOX層401を形成し、BOX層401上にSOI層402を形成し、BOX層401の一端にサイドウォール構造を形成し、BOX層401に隣接し、サイドウォール構造によってBOX層から分離してエピタキシャル層403を形成し、BOX層401とサイドウォール構造に対して非選択にエッチング液を用いた反応性イオンエッチによりSTI領域404a,404b,404cを形成した後、酸化物で充填する。

(もっと読む)

半導体記憶装置

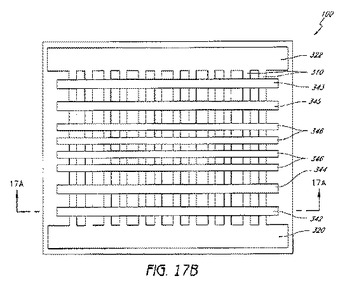

【課題】メモリセルに含まれる選択トランジスタのゲート配線のピッチに対する上層の杭打用金属配線ピッチの影響を低減する。

【解決手段】メモリセルアレイ(1)の両側にワード線ドライブ回路(2R,2L)を対向して配置し、各ワード線ドライブ回路には、ワード線ドライバをメモリセル行に対して交互に配置する。メモリセルの選択トランジスタのゲート配線(PGo,PGe)は、各メモリセル行に対応して配置される。杭打用の上層の金属配線(MLo,MLe)は、対向配置されるワード線ドライブ回路からメモリセルアレイの中央部の接続領域(10)まで延在させ、接続領域においてゲート配線に交互に電気的に接続する。金属配線は、ゲート配線の2倍のピッチで対向して配置する。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクト歩留を向上させる、スタックドコンタクト構造を有する半導体装置を提供する。

【解決手段】NAND型フラッシュメモリのビット線コンタクトには、スタックドコンタクトを構成する第1のコンタクト開口部CH1、第2のコンタクト開口部CH2a、及び第3のコンタクト開口部CH2bが設けられる。下層の第1のコンタクト開口部CH1はビット線コンタクトの中央部に配置され、上層の第2のコンタクト開口部CH2aはビット線コンタクトの左部に配置され、その中心位置がビット線コンタクトの中心位置に対して第2のコンタクト開口部CH2aのズレ量だけ左方向に配置され、上層の第3のコンタクト開口部CH2bはビット線コンタクトの右部に配置され、その中心位置がビット線コンタクトの中心位置に対して第3のコンタクト開口部CH2bのズレ量だけ右方向に配置される。

(もっと読む)

凹型ソケットを有する環状バイアを備えるダイスタッキング

凹型導電性ソケットを備える環状バイアを有するダイを含むダイスタックおよびそのダイスタックを形成する方法は、様々な電子システムで使用するための構造を提供する。一実施形態において、ダイスタックは、別のダイの凹型導電性ソケット中に挿入されたダイの頂部上に導電性ピラーを含む。 (もっと読む)

圧電素子及びその製造方法

【課題】上下の電極間のショートが防止される信頼性の高い圧電素子、及びそれを容易に製造することができる圧電素子の製造方法を提供する。

【解決手段】支持体12上に、下部電極18と、圧電膜20aと、上部電極22aとが、この順に積層されており、圧電膜20aの側面に、下部電極を18構成する材料を含む酸化膜28が形成されている圧電素子11。圧電素子用部材10の上部電極22側に形成したマスク24を介してドライエッチングすることにより上部電極22及び圧電膜20をパターニングした後、パターニングされた圧電膜20aの側面(側壁付着膜26)を酸化させて酸化膜28にする。好ましくは、プラズマ酸化により酸化処理を行う。

(もっと読む)

積層メモリ及びヒューズチップ

【課題】専用のヒューズチップとメモリコアチップを積層して少ないチップ間接合信号数で相互接続し、チップサイズの増大を回避し得る積層メモリを提供する。

【解決手段】本発明の積層メモリは、不良メモリセルを置換するための予備メモリセルを含むメモリセルアレイ20を備えたメモリコアチップMCと、予備メモリセルへの置換に対応する電気的切断状態を設定可能なヒューズ部とこのヒューズ部の状態情報に基づき不良メモリセルの救済動作を制御する救済制御回路を備えたヒューズチップHCとが積層された構成を備える。このように構成された積層メモリは、メモリコアチップMCにヒューズ素子や救済制御回路を搭載不要としてサイズを縮小でき、メモリコアチップMCとヒューズチップHCの間のチップ間接合信号数を削減することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセルトランジスタのコンタクト抵抗を低減する。

【解決手段】半導体装置70には、半導体基板1上に複数の絶縁ゲート型電界効果トランジスタが設けられる。絶縁ゲート型電界効果トランジスタのゲートの間に形成され、側面が側壁絶縁膜8及び絶縁膜9により絶縁ゲート型電界効果トランジスタのゲートと分離された自己整合コンタクト開口部の底部には凹部形状のポリシリコンプラグ11が設けられる。ポリシリコンプラグ11上にはバリアメタル膜12が設けられる。バリアメタル膜12上には、自己整合コンタクト開口部を覆うように金属プラグ13が埋設される。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】異なる配線層間で互いに直交する配線群を接続する際、接続信頼性が高く良好なスペース効率でレイアウト可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、予め設定された配列順で第1配線層に形成されそれぞれY方向(第1の方向)に延伸される複数の第1の配線20と、第2配線層に形成される複数の第2の配線21と、配列順が互いに一致する第1の配線20及び第2の配線21の間を電気的に接続する複数のコンタクト23とを備えている。各々の第2の配線21は、Y方向に直交するX方向(第2の方向)に平行な直線状に規定された隣接する2トラックのうち、一方のトラックに沿って延伸される配線部21aと、他方のトラックに沿って延伸される配線部21bと、2つの配線部21a、21bの間を接続する接続部21cとにより構成され、接続部21cに複数のコンタクト23が形成されている。

(もっと読む)

半導体装置

【課題】集積回路を構成するMISFETの処理速度の向上とリーク電流の低減を両立させ、かつ、半導体装置の小型化を達成することができる技術を提供する。

【解決手段】単体のMISFETから構成される回路素子に代えて、しきい値電圧の異なる複数のMISFETからなる同一ノードトランジスタから回路素子を構成する。例えば、図2に示すように、nチャネル型MISFET1aとnチャネル型MISFET1bを並列接続しかつ、それぞれのゲート電極Gを電気的に接続する。このとき、例えば、nチャネル型MISFET1aを高VthMISFETから構成し、nチャネル型MISFET1bを低VthMISFETから構成する。

(もっと読む)

誘電体薄膜とその製造方法および用途

【課題】薄膜表面に延びる長いクラックが存在せず、絶縁体圧の高い誘電体薄膜とその製造方法を提供する。

【解決手段】組成がBa1-xSrxTiyO3(0≦x≦1、0.9≦y≦1.1)からなる誘電体薄膜の製造において、該薄膜の前駆物質を基板に塗布して乾燥した後、該乾燥薄膜を30℃/分以下の昇温速度で本焼成を行うことによって、平均1次粒子径が70nm以上であり、薄膜表面に連続する直線状の長さ1.5μm以上の亀裂が存在せず、電圧5Vにおけるリーク電流密度が10-5A/cm2未満、ないし電圧20Vにおけるリーク電流密度が10-1A/cm2未満である誘電体薄膜を形成する。

(もっと読む)

ダミーゲートパターンを備える半導体装置

【課題】ダミーゲートパターンを用いてゲートパターンの寸法精度の向上を図り、かつ回路動作の高速化が可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体基板上に形成された拡散層10と、拡散層10の上部に配置され、MOSトランジスタのゲート電極として機能するゲートパターン11と、拡散層10の上部においてゲートパターン11と一定の間隔で隣接して配置されゲート電極として機能しないダミーゲートパターン13とを備え、ゲートパターンの疎密の程度が均一に保たれる。ダミーゲートパターン13は、拡散層10の上部におけるゲート幅方向の所定位置で切断され、切断部13aの直下で抵抗を低減して高速なMOSトランジスタの動作を実現する。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】金属薄膜上に金属酸化膜を形成する際に、金属薄膜の酸化を抑制させることが可能な半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】基板200上にチタン酸ストロンチウムまたはチタン酸ストロンチウムバリウムの薄膜を形成する工程を有する半導体装置の製造方法であって、薄膜を形成する工程は、基板上に二酸化チタンの層を数層形成する工程と、数層形成した二酸化チタンの層の上に酸化ストロンチウムと二酸化チタンとを含む積層膜、または酸化バリウムと酸化ストロンチウムと二酸化チタンとを含む積層膜を形成する工程と、を有する。

(もっと読む)

半導体回路

【課題】高速のスイッチング特性と小サブスレッショルド電流特性とが両立可能なMOS−FETで構成される半導体回路を提供する。

【解決手段】MOS−FETQ1,Q2により構成される論理回路1を有した半導体回路において、MOS−FETQ1,Q2のバックゲートバイアス電圧Vcc,VSSとは異なる電圧Vpp,Vbbを供給する電圧供給手段15,13と、MOS−FETQ1,Q2のバックゲートバイアス電圧を、電圧Vcc,VSSと電圧Vcc,VSSとは異なる電圧Vpp,Vbbとに切り換えるスイッチング手段10とを備えた構成となっている。

(もっと読む)

選択的プリチャージを使用したメモリ読取り安定性の改善

メモリデバイスは、ビットセル(34)にアクセスする前にビット線電圧を低減するために、選択的プリチャージおよび電荷共有を利用する。ビット線電圧の低減は、ビット線の異なるセクション(31、33)を異なる電圧(たとえば、供給電圧および接地)にプリチャージし、これらのセクション間で電荷共有を使用することによって達成される。読取り安定性は、ビット線電圧の低減の結果として改善される。ビット線セクション間の相対容量差(B2−C2)により、電荷共有後のビット線電圧を決定する。したがって、メモリデバイスはプロセス変動または温度変動に耐性がある。ビット線電圧は、供給電圧または接地にプリチャージされるセクションを選択することによって、設計において制御できる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 深さの異なる複数のコンタクトホールを有する構造であって、簡易な製造工程の下、基板に対するエッチングダメージを招来せず製造することが可能な半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板1上の一部領域にフィールド酸化膜2を形成し、その後にフィールド酸化膜2の一部領域をエッチング処理して凹部構造32を形成し、その後に、少なくとも凹部構造32の底面を覆うように、フィールド酸化膜2の上層に下部電極7、酸化膜8、上部電極9を形成し、ソース・ドレイン拡散領域6を形成し、その後に全面に層間絶縁膜10を堆積する。そして、拡散領域6の上面が露出するように拡散領域6の上方領域に係る層間絶縁膜10をエッチングして第1コンタクトホール11aを形成すると共に、上部電極9の上面が露出するように凹部構造32の上方領域に係る層間絶縁膜10をエッチングすることで第2コンタクトホール11cを形成する。

(もっと読む)

ピッチマルチプリケーションされた材料のループの一部分を分離するための方法およびその関連構造

半導体材料からなる途切れのないループの様々な部分を、お互いから電気的に分離する。幾つかの実施形態においては、ループの端部を、ループの中間部分から電気的に分離する。幾つかの実施形態においては、端部において互いに接続された二つの区間を有する半導体材料のループを、ピッチマルチプリケーションプロセスによって形成するが、このプロセスでは、スペーサのループはマンドリルの側壁に接して形成される。マンドリルを除去し、マスキング材料のブロックを、スペーサループの少なくとも一つの端部に置く。幾つかの実施形態においては、マスキング材料のブロックを、スペーサループの各端部に置く。スペーサおよびブロックによって画定されるパターンを、半導体材料の層へと転写する。ブロックは、全ループを電気的に接続する。選択ゲートを、ループの各区間に沿って形成する。ブロックは、ソース/ドレインとして機能する。選択ゲートをオフ状態にバイアスして、ループの区間の中間部分からブロックへの電流を防ぎ、それによって、ループの端部から中間部分を電気的に分離し、また、ループの異なる区間をお互いから電気的に分離する。  (もっと読む)

(もっと読む)

半導体素子のハードマスクパターン形成方法

【課題】マトリックス状に配列された露光装備の解像度限界以下の活性領域を定義するためのハードマスクパターンの形成方法を提供する。

【解決手段】半導体基板101上に、ハードマスク膜103と第1のマスクパターン105を形成する。第1のマスクパターンと交差する第1のパターンと、第1のマスクパターン間に位置する第2のパターンを含む第2のマスクパターン107を形成する。第1のパターン間に第3のマスクパターンを形成する。第1のパターンと第1のマスクパターンが交差する領域に第1のマスクパターンが残留し、第1のパターンと第2のパターンが交差する領域に第2のパターンが残留するようにエッチングを行う。残留する第1のマスクパターン及び第2のマスクパターンをエッチングマスクとして用い、ハードマスクパターンを形成する。

(もっと読む)

161 - 180 / 401

[ Back to top ]