Fターム[5F083AD00]の内容

半導体メモリ (164,393) | DRAM (5,853)

Fターム[5F083AD00]の下位に属するFターム

読出しトランジスタ (1,433)

キャパシタ (3,513)

1MOSトランジスタ+1Cap以外のDRAM (506)

Fターム[5F083AD00]に分類される特許

141 - 160 / 401

サブワードライン駆動回路

【課題】レイアウト面積の増加なしにワードラインを速くディセーブルさせるサブワードライン駆動回路を提供する。

【解決手段】第1ワードラインを活性及び非活性化する第1ワードライン駆動及びクリア手段P1,N1と、第1ワードラインの電位を接地電位に放出させる第1ワードライン電位放出手段N2と、第2ワードラインを活性及び非活性化する第2ワードライン駆動及びクリア手段P2,N3と、第2ワードラインの電位を接地電位に放出させる第2ワードライン電位放出手段N4と、ワードラインブースティング信号により第1及び第2ワードラインを等しくする等化手段N5と、を含み、等化手段は、第1及び第2ワードライン電位放出手段が形成される領域に形成され、第1及び第2ワードライン電位放出手段は、第1ワードライン駆動及びクリア手段と第2ワードライン駆動及びクリア手段との間に配置される。

(もっと読む)

超高帯域メモリのダイスタック

【課題】 3次元ダイスタックを用いて形成されたメモリを提供する。

【解決手段】 システムは、中央処理装置(CPU)、CPUと連絡し、複数の垂直に積層された集積回路チップと複数の入力/出力(I/O)ポートを含み、各I/Oポートは、基板貫通ビアによって複数のチップの少なくとも1つに接続されるメモリデバイス、及び

CPUと前記メモリデバイスと連絡し、メモリデバイスにデータを伝送、またはメモリデバイスから伝送するのを管理するように構成するダイレクトメモリアクセス(DMA)コントローラを含むシステム。

(もっと読む)

内部電源電圧生成回路および内部電源電圧生成方法。

【課題】半導体装置において、内部電源電圧を安定供給する。

【解決手段】本発明は、基準電圧のレベルに対応するクロック情報を有する第1クロック信号と内部電源電圧のレベルに対応するクロック情報を有する第2クロック信号とを比較するためのクロック比較手段210と、該クロック比較手段210の出力信号に対応する電圧レベルを有する駆動制御電圧を生成するための制御信号生成手段230と、前記駆動制御電圧に応答して内部電源電圧端を駆動するための駆動手段250を備える内部電源電圧生成回路を提供する。

(もっと読む)

メモリモジュールおよびそのレイアウト方法

【課題】 LR−DIMM方式のVLPタイプのLR−DIMMの新規の配線方法を提案する。

【解決手段】 複数のDRAMと、データを入力する2つのコネクタと、該2つのコネクタに入力されたデータをリドライブして前記複数のDRAMへ供給するバッファデバイスとが基板上に搭載されており、

前記バッファデバイスは前記2つのコネクタが両側に置かれる前記基板の中央付近に配置され、各コネクタからのデータを逆側に配置されたDRAMへ供給する。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

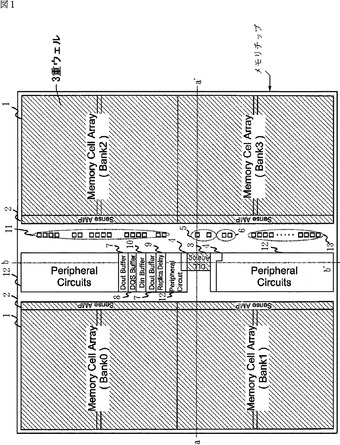

ダイナミック型半導体記憶装置

【課題】安定したクロック発生動作、高精度で低消費電力を実現しDLLを備える。

【解決手段】内部クロック信号を生成するDLL回路、内部クロック信号で動作を制御される周辺回路とメモリセルアレイを含む。第1電源電圧を供給するために同期回路に接続された第1電源パッド、第1電源電圧より低い第2電源電圧を供給するために同期回路に接続された第2電源パッド、周辺回路とメモリセルアレイに第3電源電圧を供給するための第3電源パッド、周辺回路とメモリバンクに第3電源電圧より低い第4電源電圧を供給する第4電源パッドを含む。複数のメモリセルアレイは第1領域と第2領域に分割して配置される。複数の周辺回路は第1領域と第2領域の間の第3領域に配置される。第1、2、3,4電源パッドは第1領域と前記第3領域の間の第4領域に配置されている。

【選択図】図1  (もっと読む)

(もっと読む)

半導体素子及びそのセルブロック配置方法

【課題】長さの制限がなく、メモリセルブロックを密集配列させて高いパッキング密度を具現することができる半導体素子及びそのセルブロック配置方法を提供する。

【解決手段】セルアレイと、前記セルアレイの横及び縦方向に配置されたデコーダとを有する複数個の「L」字形状のセルブロックを有し、前記複数個の「L」字形状のセルブロックは、前記横及び縦方向と交差する斜線方向に指向配置されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】エッチングストッパ膜を有し、配線間容量の増大を抑制可能な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体基板11と、半導体基板11の表面上部に配設された層間絶縁膜29と、層間絶縁膜29に埋め込まれ、半導体基板11に対向する上面が層間絶縁膜29の上面と面一に配設され、互いに離間して配置された複数のビアプラグ31と、層間絶縁膜29及びビアプラグ31の表面上部に配設された層間絶縁膜39と、層間絶縁膜39によって分離され、ビアプラグ31と接続され、ビアプラグ31に対向する上面が層間絶縁膜39の上面と面一に配設され、層間絶縁膜39を挟んで相対向する側面に、層間絶縁膜29の側から順に、層間絶縁膜29とはエッチング性が異なり且つ層間絶縁膜39より比誘電率の高い側壁絶縁膜35、及び側壁絶縁膜35とはエッチング性が異なる側壁絶縁膜37を有する複数の第2配線33とを備える。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】導電層が基板の内部深くにまで達することを回避して、浅いソース・ドレイン領域を形成することを可能とし、微細化に適した半導体装置及びその製造方法を得る。

【解決手段】シリコン基板1の上面内にエクステンション5を形成した後、シリコン酸化膜30を全面に堆積し、シリコン酸化膜30上にシリコン窒化膜31を、シリコン窒化膜31上にシリコン酸化膜32をそれぞれ堆積し、シリコン酸化膜32、シリコン窒化膜31及びシリコン酸化膜30をこの順にエッチングしてサイドウォール36を形成する。不純物領域13を形成し、シリコン酸化膜に対して選択性を有する条件下でシリコン成長を行うことにより、シリコン成長層15,16,37を形成する。コバルト17を全面に堆積した後、熱処理を行うことにより、コバルトシリサイドを形成する。その後、未反応のコバルト17を除去する。

(もっと読む)

集積回路デバイスのヒューズ構造

【課題】 集積回路デバイスのヒューズ構造を提供する。

【解決手段】 本発明のヒューズ構造は、半導体基板の一部の上に配置された金属含有導電性材料のストリップを含み、ストリップは、第1方向に沿って延伸し、均一な線幅を有する。誘電体層は、導電層を覆う。誘電体層内は、第1ビアと第2ビアを有し、第1インターコネクトと第2インターコネクトをそれぞれ含む。第1インターコネクトは、ストリップ上の第1位置と物理的且つ電気的に接触しており、第2インターコネクトは、ストリップ上の第2位置と物理的且つ電気的に接触している。導電ストリップ上の第1と第2位置は、シリコンを含まない。誘電体層の上方は、第1インターコネクトに電気的に接続された第1配線構造と、第2インターコネクトに電気的に接続された第2配線構造である。

(もっと読む)

半導体装置

【課題】信号配線領域の大幅な増大をともなうことなく、信号配間に生じるカップリングノイズの低減を実現した半導体装置を提供する。

【解決手段】信号線が並行配置される場合において、当該信号線の全てが片側の信号線だけからのみカップリングノイズを受ける構成とするため、当該複数の信号線の両側において他の信号線と対向しないように、その信号線の片側一方にのみ電源電位、接地電位又は当該信号線がカップリングノイズを受ける期間において一定電位に維持される配線を配置する。

(もっと読む)

半導体記憶装置

【課題】メモリーセルへの配線長差で生じるスキューをより低減できる半導体記憶装置を提供する。

【解決手段】データが格納されるメモリーセル領域と、メモリーセル領域内のメモリーセルを選択するためのアドレス及びコマンドが入力される、チップの中央付近に配置されたコマンド回路とを有する半導体記憶装置であって、アドレス及び前記コマンドに基づいて生成された信号をメモリーセルへ入力する、メモリーセル領域の一端に配置された入力バッファと、選択されたメモリーセルへデータを書き込む、あるいは選択されたメモリーセルから読み出されたデータを出力する、メモリーセル領域の入力バッファと対向する位置に配置された出力バッファとを有する。

(もっと読む)

除去可能な補助検査端子を有するソリッドステート・ドライブの検査方法

【課題】除去可能な補助検査端子を有するソリッドステート・ドライブの検査方法を提供する。

【解決手段】除去可能な補助検査端子を有するソリッドステート・ドライブの検査方法において、該ソリッドステート・ドライブのメモリ半導体素子に不良が発生した場合、不良分析のために検査端子が設けられた補助ボードを別途に使用して除去するか、又は印刷回路基板の一側面エッジにメモリ半導体素子を検査可能な印刷回路パターンと接続された貫通ホールを設け、不良発生時に、前記貫通ホールが露出されるように、印刷回路基板の一部を切断し、メモリ半導体素子に対する不良分析を実施する。従って、印刷回路基板に搭載されたメモリ半導体素子を取り外さずに不良分析を実施することが可能である。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】閾値電圧が互いに同一であることを要求される2つのトランジスタにおいて、閾値電圧が異なる値になることを抑制する半導体装置の製造方法及び半導体装置を提供する。

【解決手段】第1素子形成領域12には第1トランジスタ202及び第2トランジスタ204が形成され、第2素子形成領域13には第3トランジスタ302が形成される。これら3つのトランジスタは同一導電型である。第1トランジスタ202及び第2トランジスタ204は同一の閾値電圧を有する。第1マスクパターンを用いて第1素子形成領域12に第1ウェル210を形成し、第2マスクパターンを用いて第2素子形成領域13に第2ウェル410を形成する。第1トランジスタ202のチャネル領域及び第2トランジスタ204のチャネル領域は基準線Lを介して線対称な形状を有している。また第1マスクパターンも、基準線Lを介して線対称な形状を有している。

(もっと読む)

不揮発性磁気メモリを使用している低電力電子システム

コンピューティングシステムが少なくとも1つの機能的ユニット及び少なくとも1つの機能的ユニットに接続された磁気ランダムアクセスメモリ(MRAM)ブロックを含む。MRAMブロックは少なくとも1つの機能的ユニットのパワーダウン状態の間、少なくとも1つの機能的ユニットの機能的状態を格納するように構成される。  (もっと読む)

(もっと読む)

欠陥解析方法、プログラム及び電子デバイスの製造方法

【課題】測定スループットを向上させ、かつ正確な解析結果を得ることができる欠陥解析方法を得る。

【解決手段】ステップS1で、検査装置の面積縮小機能を用いて所定の工程後に所定の工程による新規欠陥の座標及び検出サイズを抽出する欠陥検出処理を行い、ステップS3で、検出されたすべての新規欠陥を有効とする識別条件で新規欠陥の有無をチップ単位に判定する。その後、ステップS5において、面積縮小機能による欠陥検査対象領域の全欠陥検査可能領域に対する面積比を求め、ステップS6において、上記面積比に基づき、推定欠陥有りチップ数を推定換算する。

(もっと読む)

金属シリサイド形成のための方法および装置

本明細書で述べられる実施形態は、無拡散アニールプロセスを使用して金属シリサイド層を形成する方法を包含する。一実施形態では、基板上に金属シリサイド材料を形成するための方法が、提供される。その方法は、基板のシリコン含有表面を覆って金属材料を堆積させるステップと、金属材料を覆って金属窒化物材料を堆積させるステップと、金属窒化物材料を覆って金属接点材料を堆積させるステップと、基板を無拡散アニールプロセスにさらして金属シリサイド材料を形成するステップとを含む。無拡散アニールプロセスの短い時間枠は、窒素がシリコン含有界面に拡散して窒化シリコンを形成する時間を低減し、それ故に界面抵抗を最小限にする。  (もっと読む)

(もっと読む)

半導体集積回路および半導体記憶装置

【課題】チップの内部バスやチップ間を接続する外部バスにおける消費電力の低減や、データ転送速度の向上を実現する。

【解決手段】論理レベル‘H’か‘L’かその中間レベルとなる‘M’を採り得る複数本のバスDB[0]〜DB[n−1]と、データD[0]〜D[m−1]を符号化し、これに基づいて複数本のバスのそれぞれを論理レベル‘H’、‘L’、‘M’のいずれかに駆動する送信回路TXと、複数本のバスを互いにショートするバスイコライズ回路BEQを設ける。送信回路TXは、データの符号化を行う際に、論理レベル‘H’に駆動するバスの本数(k本)と論理レベル‘L’に駆動するバスの本数(k本)が同数となるような組み合わせを用いる。バスイコライズ回路BEQは、データが送信された後にショート動作を行うことで、各バスを論理レベル‘M’にプリチャージする。

(もっと読む)

半導体記憶装置

【課題】DRAM回路のセンスアンプ領域の面積を削減する構成が求められている。

【解決手段】本発明は、メモリセルが接続されるビット線を駆動するセンスアンプと、前記センスアンプに対して電源を供給するドライバトランジスタとを有する半導体記憶装置であって、前記センスアンプは、列状に配置されて、第1導電型のトランジスタが配列する第1のセンスアンプ列と第2導電型のトランジスタが配列する第2のセンスアンプ列を構成し、前記ドライバトランジスタは、前記第1のセンスアンプ列と前記第2のセンスアンプ列の間において、前記第1のセンスアンプ列に対応する第1導電型の第1のドライバトランジスタと、前記第2のセンスアンプ列に対応する第2導電型の第2のドライバトランジスタを含む少なくとも一列のトランジスタ列を構成する半導体記憶装置である。

(もっと読む)

半導体装置、半導体製造装置および半導体装置の製造方法

【課題】半導体基板上の凹部が逆テーパ形状やオーバーハング形状を有する場合においても、埋め込み性や膜質の劣化を抑制しつつ、埋め込み絶縁膜の応力を低減することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上にトレンチ5を形成し、熱CVD法を用いることで、トレンチ5内の一部を埋め込む埋め込み絶縁膜6を半導体基板1上に成膜し、埋め込み絶縁膜6の成膜時よりも高い温度にて埋め込み絶縁膜6を熱処理した後、熱CVD法を用いることで、トレンチ5内の一部を埋め込む埋め込み絶縁膜7を埋め込み絶縁膜6上に成膜し、埋め込み絶縁膜7の成膜時よりも高い温度にて埋め込み絶縁膜7を熱処理した後、熱CVD法を用いることで、トレンチ5内を完全に埋め込む埋め込み絶縁膜を埋め込み絶縁膜7上に成膜し、埋め込み絶縁膜の成膜時よりも高い温度にて埋め込み絶縁膜を熱処理する。

(もっと読む)

141 - 160 / 401

[ Back to top ]