Fターム[5F083AD00]の内容

半導体メモリ (164,393) | DRAM (5,853)

Fターム[5F083AD00]の下位に属するFターム

読出しトランジスタ (1,433)

キャパシタ (3,513)

1MOSトランジスタ+1Cap以外のDRAM (506)

Fターム[5F083AD00]に分類される特許

61 - 80 / 401

半導体装置

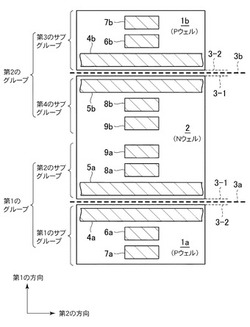

【課題】センスアンプのセンスマージンを拡大する。

【解決手段】2つの素子分離領域3に隣接して各ウェル1,2にドライバトランジスタ4a,5a,4b,5bをそれぞれ配置し、各ウェル1,2にドライバトランジスタ4a,5a,4b,5bよりも素子分離領域3a,3bから離れた位置にクロスカップルされた2つの一対のセンストランジスタ6a乃至9a、6b乃至9bをそれぞれ配置する。これにより、センストランジスタ6a乃至9a、6b乃至9bと夫々対応する素子分離領域3a,3bと間に一定以上の距離が確保されることから、素子分離領域3a,3bからの距離によってトランジスタのしきい値が変化する現象の影響が低減され、その結果、夫々クロスカップルされた一対のトランジスタの特性を正確に一致させることが可能となる。

(もっと読む)

半導体装置

【課題】リードデータの衝突を回避すること。

【解決手段】本発明の半導体装置は、複数のメモリチップと、前記複数のメモリチップから内部データバスに出力されたリードデータを入力し、入力されたリードデータを外部データバスに出力するI/Fチップと、を有する。また、前記内部データバスは、前記複数のメモリチップごとに設けられている。また、前記I/Fチップは、前記複数のメモリチップから前記内部データバスを介して入力されたリードデータをバッファリングするFIFO回路と、前記FIFO回路にバッファリングされたリードデータの前記外部データバスへの出力タイミングを調整するFIFOコントローラと、を有する。

(もっと読む)

半導体パッケージ

【課題】ボンディングワイヤのループインダクタンスを低減した半導体パッケージを提供する。

【解決手段】所定の方向に交互に配置された信号用パッドおよび補助パッドのそれぞれが複数設けられた半導体装置と、信号用ボンドフィンガー、電源電圧用ボンドフィンガーおよび接地電位用ボンドフィンガーのそれぞれが複数設けられたパッケージ基板と、を有する。複数の信号用パッドのそれぞれが複数の信号用ボンドフィンガーのそれぞれと第1のワイヤを介して接続され、複数の電源電圧用ボンドフィンガーおよび複数の接地電位用ボンドフィンガーのそれぞれが複数の補助パッドのそれぞれと第2のワイヤを介して接続されている。第1のワイヤが、電源電圧用ボンドフィンガーに接続された第2のワイヤと接地電位用ボンドフィンガーに接続された第2のワイヤとの間に配置されている。

(もっと読む)

半導体装置

【課題】積層型の半導体装置においてインターフェースチップからコアチップへのクロック信号の供給を不要とする。

【解決手段】外部から供給されるコマンド信号CMD及びクロック信号CKを受けて、各々がクロック信号CKに同期し、且つ、互いにタイミングが異なる複数のリード制御信号R1,R2を出力するリードタイミング制御回路100を有するインターフェースチップIFと、インターフェースチップIFに積層され、コマンド信号CMDが示す動作をリード制御信号R1,R2に同期してそれぞれ実行する複数の内部回路を有するコアチップCC0〜CC7とを備える。本発明によれば、コアチップに内でのレイテンシ制御が不要となることから、コアチップにクロック信号を供給する必要がなくなる。

(もっと読む)

半導体装置

【課題】 半導体装置のレイアウト面積を大きくすることなく、内部電源回路の電流供給能力の向上を可能にする。

【解決手段】 半導体装置は、主領域12と、第1の方向に沿って主領域に形成された複数の第1の電源配線15と、第1の電源配線と交差しかつ電気的に接続されるように第2の方向に沿って主領域に形成された複数の第2の電源配線16と、第1の方向に関して主領域の一方の側に隣接する第1の隣接領域13に設けられ、第1の電源配線の一端にそれぞれ接続された第1の内部電源回路17と、第2の方向に関して主領域の一方の側に隣接する第2の隣接領域14に設けられ、複数の第2の電源配線のうち最も第1の電源配線の他端に近い電源配線の一端に接続された第2の内部電源回路18と、を備える。

(もっと読む)

半導体装置

【課題】複数のランクに分類された積層型の半導体装置において、異なるランクに対して連続アクセスされた場合のデータの衝突を防止する。

【解決手段】ライトデータを伝送する貫通電極TSVWとリードデータを伝送する貫通電極TSVRとをそれぞれ有する互いに積層された複数のコアチップCC0〜CC7と、これらコアチップCC0〜CC7に共通接続されたインターフェースチップIFとを備える。インターフェースチップIFは、データ入出力端子16と、データ入出力端子と貫通電極TSVWとの間に設けられた52入力バッファと、データ入出力端子16と貫通電極TSVRの間に設けられた出力バッファ51とを有する。本発明によれば、ライトデータとリードデータを互いに異なる貫通電極を介して伝送していることから、異なるランクに対して連続アクセスされた場合であってもデータの衝突が生じない。

(もっと読む)

積層チップパッケージおよびその製造方法

【課題】簡単な構成で、複数の積層チップパッケージを積層し互いに電気的に接続することを可能にし、所望の数の半導体チップを含むパッケージを低コストで実現する。

【解決手段】積層チップパッケージ1Sは、本体2を備え、本体2は、主要部分2Mと、主要部分2Mの上面、下面に配置された複数の第1の端子4、第2の端子5を有している。主要部分2Mは、2つの階層部分10S1,10S2と、これらを貫通する複数の貫通電極Tを含んでいる。複数の貫通電極Tは、複数の端子4,5に電気的に接続されている。各階層部分は、第1の面と第2の面を有する半導体チップと、複数の表面電極を含んでいる。階層部分10S1,10S2は、第2の面同士が対向するように接合されている。端子4は階層部分10S1の表面電極を用いて構成され、端子5は階層部分10S2の表面電極を用いて構成されている。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】 高誘電率絶縁膜の吸湿を抑制し、信頼性を向上させる。

【解決手段】 処理容器内に基板を搬入する工程と、処理容器内で基板上に高誘電率絶縁膜を形成する工程と、処理容器内で高誘電率絶縁膜上に高誘電率絶縁膜よりも吸湿性の低い低吸湿性絶縁膜を形成する工程と、処理容器内より低吸湿性絶縁膜形成後の基板を搬出する工程と、を有する。

(もっと読む)

パターン形成方法及びデバイス製造方法

【課題】露光装置の解像限界よりも微細な非周期的な部分を含むパターンを、露光装置を用いて形成する。

【解決手段】パターン形成方法は、ウエハW上に第1L&Sパターン71を形成し、第1L&Sパターン71を覆うように第1保護層48、周期方向が直交する第2L&Sパターン78、及びフォトレジスト層60を形成し、第2L&Sパターン78の一部と重なるように、フォトレジスト層60に第1開口部60A,60Bを有する第3パターンを形成し、第1開口部60A,60Bを介して第1保護層48に第2開口部48A,48Bを形成し、第2開口部48A,48Bを介して第1L&Sパターン71の一部を除去する。

(もっと読む)

半導体装置、および、その製造方法、電子機器

【課題】製造効率の向上、コストダウン、信頼性の向上、小型化を容易に実現させる。

【解決手段】各配線111h,211hにおいて、第1半導体チップ100および第2半導体チップ200の側端部にて露出した側面を、導電層401で被覆される。これにより、導電層401によって両配線111h,211hの間が電気的に接続させる。

(もっと読む)

半導体装置

【課題】補償容量素子を構成する容量絶縁膜が破壊されることのない半導体装置を提供する。

【解決手段】第1の電圧が供給される第1の電源端子29と、第2の電圧が供給される第2の電源端子23と、容量絶縁膜42と該容量絶縁膜42を挟んで形成される第1及び第2電極とを其々備えており、前記第1及び第2の電源端子間に直列に設けられる複数の補償容量素子4と、奇数番目の前記補償容量素子4と次の偶数番目の前記補償容量素子4とを各々接続する第1の配線層に形成された第1の容量接続配線と、偶数番目の前記補償容量素子4と次の奇数番目の前記補償容量素子4とを各々接続する第2の配線層に形成された第2の容量接続配線と、前記第1及び第2の容量接続配線のいずれか一方に隣接して設けられ、実質的に固定された電圧が供給されるシールド配線5と、を備える。

(もっと読む)

半導体集積回路装置

【課題】設計工数をほとんど掛けないで、CMP対策及び短時間光アニール対策の両対策に最適化されたダミーパターンを有する半導体集積回路装置を提供すること。

【解決手段】基板上に、メモリマクロ領域10及び機能回路領域20を有する半導体集積回路装置1において、機能回路領域20間、及び、メモリマクロ領域10と機能回路領域20との間に配置されるとともにダミーパターン41を含むダミーパターン領域40を備え、ダミーパターン41は、前記メモリセルアレイ領域におけるメモリセルパターン11の拡散層12、13及びゲート電極14と同等のパターンであり、ダミーパターン領域40におけるダミー拡散層42、43及びダミーゲート電極44の面積率は、メモリセルアレイ領域における拡散層12、13及びゲート電極14の面積率と同等以上である。

(もっと読む)

半導体メモリチップ、半導体集積回路、半導体パッケージ、半導体メモリ装置、半導体装置パッケージの製造方法、および半導体装置の製造方法

【課題】3D半導体装置を提供する。

【解決手段】半導体メモリチップであって、データチップパッドと、データチップパッドに連結されるデータ入力バッファと、データ入力バッファに連結され、データ入力バッファから出力されるデータをラッチするラッチと、メモリセル・アレイと、を具備し、データ入力バッファとラッチは、データチップパッドからメモリセル・アレイまでの第1データ書き込み経路の部分であり、半導体メモリチップは、第1データ書き込み経路の電気的なノードに電気的に連結され、第1データ書き込み経路の一部分を含む第2データ書き込み経路を形成する貫通電極をさらに具備し、第2データ書き込み経路は、データチップパッドとは異なるチップ・ターミナルから、メモリセル・アレイまで拡張される。

(もっと読む)

半導体記憶装置

【課題】ヒューズ素子の実装密度を向上させる。

【解決手段】半導体記憶装置の救済アドレス制御部116は、ヒューズ格納部118と救済回路120を含む。ヒューズ格納部118は、レーザービームの照射により切断可能な複数のヒューズ素子122と、複数のヒューズ素子122の直上にレーザービームを通過させるための開口部130が設けられた保護膜とを含む。救済回路120は、ヒューズ素子122の切断状態から、救済アドレスを特定する。開口部130は、ヒューズ格納部118の長辺方向においては一体形状を有する。また、救済回路120は、ヒューズ格納部118の短辺側の端部に隣接配置される。

(もっと読む)

半導体記憶装置

【課題】ワード線間の寄生容量が相対的に大きくなっても性能が低下しない半導体記憶装置を提供する。

【解決手段】第1の方向に配線された複数のワード線と、第1の方向と交差する方向に配線された複数のビット線と、複数のワード線とビット線との交点に対応して設けられた複数のDRAMセルを備えるメモリセルアレイと、複数のワード線を駆動するワード線ドライバと、複数のワード線それぞれに接続されメモリセルアレイを間に挟んで、ワード線ドライバに対して反対側に配置され、当該ワード線に隣接するワード線が選択されたときに導通して当該ワード線を非選択電位に接続し、当該ワード線が選択されたときに非導通となる複数のワード線電位安定化トランジスタと、を備える。

(もっと読む)

埋め込みビットラインを備えた半導体装置およびその製造方法

【課題】埋め込みビットラインと接合を安定的にコンタクトさせることができ、埋め込みビットラインとコンタクトされる接合の深さを均一に形成できる半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置製造方法は、基板をエッチングして何れか1つの側壁がステアを有するトレンチを形成するステップと、前記ステアの表面下部に接合部を形成するステップと、前記接合部とコンタクトされる埋め込みビットラインを形成するステップと、を含むことを特徴とする。本発明は、垂直セル構造の埋め込みビットライン製造時に使用されるマスクの個数を顕著に減少させることができ、工程ステップを減少させ、行うことができるため工程の単純化および工程難易度、原価節減の側面で非常に有利である。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減する。

【解決手段】内部回路(LK#2)の内部ノードに対応して対応の内部ノードの信号をラッチする複数のラッチ回路(F1−F7)をテストパス(302)に配置する。内部回路のMISトランジスタは、ラッチ回路のMISトランジスタよりスタンバイ状態時にゲートトンネル電流が低減される状態に設定される。

(もっと読む)

SeOI上の疑似インバータ回路

【課題】メモリアレイのワードライン・ドライバ回路として使用できる、大きくなく、低消費電力の回路を提供する。

【解決手段】半導体・オン・インシュレータ(SeOI)基板上に形成された回路であって、電源電位を印加する為の第1、第2の端子間に第2のチャネル型のトランジスタと直列の第1のチャネル型のトランジスタを含み、トランジスタの各々が薄層におけるドレイン領域およびソース領域と、ソース領域とドレイン領域間に延びるチャネルと、チャネルの上方に配置されたフロント・コントロール・ゲートとを備え、各トランジスタが、トランジスタのチャネルの下方のベース基板に形成され、かつトランジスタの閾値電圧を調整する為にバイアスされうるバック・コントロール・ゲートを有し、トランジスタのうちの少なくとも1つが閾値電圧を十分に調整するバックゲート信号の作用の下、空乏モードで動作するように構成される。

(もっと読む)

昇圧回路及び半導体装置

【課題】半導体チップのチップ面積を小さくできる昇圧回路を提供する。

【解決手段】昇圧回路100は、N個(Nは2以上の自然数)の容量素子(容量素子C0〜C3)を備える。N個の容量素子のうち第K番目(1<K<N、Kは自然数)の容量素子(容量素子C2)は第(K−1)番目の容量素子(容量素子C1)によって昇圧された第(K−1)番目の昇圧電圧を受けて、第(K−1)番目の昇圧電圧を更に昇圧した第K番目の昇圧電圧を発生して第(K+1)番目の容量素子(容量素子C3)に供給し、第N番目の容量素子の一端(出力端子OUT)から第N番目の昇圧電圧を発生する。N個の容量素子の内、少なくとも1つの容量素子(容量素子C0及びC1)は他の容量素子(容量素子C2及びC3)が形成された第1のチップ(半導体チップCHIP2)とは異なる第2のチップ(半導体チップCHIP1)に形成され、第1及び第2のチップは互いに積層されている。

(もっと読む)

情報処理方法、積層型集積回路メモリ

【課題】メモリの単位メガバイト当たり製造コストを、単にモノリシック回路集積法で慣用的に製造される回路の数分の一に低減させる。

【解決手段】各層が別々に最適化されるように、別々の層(103)上へのメモリ回路(103)および制御論理回路(101)の物理的分離が可能な三次元(3DS)メモリ(100)。幾つかのメモリ回路(103)について1つの制御論理回路(101)で十分であり、コストを低減できる。3DSメモリ(100)の製造は、メモリ回路(103)を50μm以下の厚さに薄肉化する工程と、該メモリ回路を、ウェーハ基板形態のまま回路積層体に接合する工程とを有する。微粒子の高密度層間垂直バス相互接続部(105)が使用されている。3DSメモリ(100)製造方法は、幾つかの性能および物理的サイズ効率を可能にしかつ確立された半導体加工技術により実施される。

(もっと読む)

61 - 80 / 401

[ Back to top ]