Fターム[5F083AD00]の内容

半導体メモリ (164,393) | DRAM (5,853)

Fターム[5F083AD00]の下位に属するFターム

読出しトランジスタ (1,433)

キャパシタ (3,513)

1MOSトランジスタ+1Cap以外のDRAM (506)

Fターム[5F083AD00]に分類される特許

81 - 100 / 401

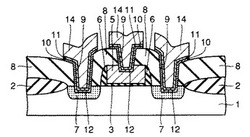

半導体装置およびその製造方法

【課題】半導体装置の微細化に対処しうる、製造が容易で安価な低コンタクト抵抗の半導体装置およびその製造方法を得る。

【解決手段】Si基板(1)上の不純物領域(7)を覆うように層間絶縁膜(8)が形成され、その層間絶縁膜(8)には、層間絶縁膜(8)を貫通して不純物領域(7)を掘り込むようにコンタクトホール(9)が形成されている。コンタクトホール(9)内には、金属膜(10)、バリア層(11)、金属シリサイド(12)およびソース、ドレイン配線(14)が形成されている。ソース、ドレイン配線(14)は、タングステンから形成されている。

(もっと読む)

原子層堆積装置及び原子層堆積方法

【課題】安定してプラズマを発生させることができる原子層堆積装置を提供する。

【解決手段】基板上に薄膜を形成する原子層堆積装置であって、薄膜の原料である原料ガスを供給する原料ガス供給部と、原料ガスと反応して薄膜を形成する酸化ガスを供給する酸化ガス供給部と、酸化ガスのプラズマを発生させるプラズマ発生部と、原料ガス、及び、酸化ガスを排気する排気部と、を備え、酸化ガス供給部は、酸素ガスを貯蔵する酸素ガス貯蔵部と、酸素ガス貯蔵部に貯蔵された酸素ガスからオゾンを発生させるオゾン発生部と、を備えることを特徴とする原子層堆積装置。

(もっと読む)

半導体装置

【課題】 同時に入出力されるデータビット数が異なる半導体装置では、プリント基板の半田ボールと半導体チップのパッド位置が、左右の領域に分かれ、ボールとパッド間の配線ができなくなり、ビット数が異なる製品を、1つのチップで共用することができないという問題がある。

【解決手段】 同時に入出力されるデータビット数が8、16、32ビットのいずれかに変更可能で、複数のパッド電極がチップの中央部に少なくとも2列に配列された半導体チップを有した半導体装置は、前記複数のパッド電極の中の所定のパッド電極が、データ入出力数が16ビットのときのみに使用される16ビット専用のパッド電極と、データ入出力数が32ビットのときのみに使用される32ビット専用のパッド電極と、を備えることを特徴とする。

(もっと読む)

半導体装置

【課題】単一の半導体メモリチップを互いに異なるピン配列を備えたパッケージに実装する場合に、半導体メモリチップのパッド数の増加を防止する。

【解決手段】製品指定情報が、ボンディンク回路、ヒューズ回路等の製品指定情報回路228から与えられる。デコーダ回路224は、この製品指定情報をデコードして、該デコード結果に応じて複数の信号回路220の1つを選択的にチップ・パッド210に接続する。

(もっと読む)

半導体装置、設計装置、及びプログラム

【課題】リングゲート型MOSトランジスタ間の領域だけでなく、リング内の領域においてもディッシング現象の発生を抑止する。

【解決手段】半導体装置1は、基板10と、基板10上に形成されたリング形状のゲート電極21を有するトランジスタ20bと、ゲート電極21の外側に配置され、ゲート電極21と同層に設けられる複数の外部ダミーパターン40と、ゲート電極21の内側に配置され、ゲート電極21と同層に設けられる少なくとも1つの内部ダミーパターン41とを備える。

(もっと読む)

半導体メモリ装置及びそれを含む半導体パッケージ

【課題】高性能及び低電力が要求される多様な装置及びシステムを支援できる、マルチチャネルインタフェース方式のワイド入出力を有する半導体メモリ装置及びそれを含む半導体パッケージを提供する。

【解決手段】本発明の一実施形態に係る半導体メモリ装置は、複数のメモリセルアレイを含む半導体ダイからなり、半導体ダイの中央部に形成される入出力バンプパッド部を含む。入出力バンプパッド部は、前記それぞれのメモリセルアレイを外部装置と独立的に接続するための複数のチャネルを提供する。マルチチャネル方式のワイド入出力インタフェースを通じて動作周波数の減少及びバンド幅の拡張を図ることによって、高性能の装置及びシステムを支援すると同時に電力消耗を減少させる。

(もっと読む)

エッジ・ダミーメモリセル・ブロックを除去した半導体メモリ装置

【課題】エッジ・ダミーメモリセル・ブロックを除去したオープン・ビットライン構造の半導体メモリ装置を提供する。

【解決手段】メモリセル配列を含むメモリセル・ブロックと、一つ以上の第1センスアンプを具備し、それぞれの第1センスアンプは、第1ビットライン、第1相補ビットライン及び第1サイズの第1トランジスタを有する第1増幅回路を具備するエッジ・センスアンプ・ブロックと、一つ以上の第2センスアンプを具備し、それぞれの第2センスアンプは、第2ビットライン、第2相補ビットライン、及び前記第1サイズと互いに異なる第2サイズの第2トランジスタを有する第2増幅回路を具備するセントラル・センスアンプ・ブロックと、エッジ・センスアンプ・ブロックと電気的に連結され、少なくとも1つのキャパシタを含むキャパシタ・ブロックと、を具備する。

(もっと読む)

ルテニウム錯体混合物、その製造方法、成膜用組成物、ルテニウム含有膜及びその製造方法

【課題】CVD法を用いて良質なルテニウム薄膜を形成させるためには、低温で薄膜を形成させることが必要であり、熱に対して高い反応性を有するルテニウム化合物が望まれていた。

【解決手段】(2,4−ジメチルペンタジエニル)(エチルシクロペンタジエニル)ルテニウム及び(2,4−ジメチルペンタジエニル)(エチルシクロペンタジエニル)ルテニウムに対して0.1〜100重量%のビス(2,4−ジメチルペンタジエニル)ルテニウムを含有するルテニウム錯体混合物を原料として用い、CVD法等によりルテニウム含有膜を製造する。

(もっと読む)

リセス埋込ダイを備えるコアレスパッケージ

マイクロエレクトロニクスパッケージ構造を形成する方法、及びそれによって形成される構造物が提供される。該方法は、めっき部材に、ダイを保持するためのキャビティを形成し、前記キャビティ内にダイを取り付け、前記ダイに隣接して誘電体材料を形成し、前記ダイに隣接して前記誘電体材料内にビアを形成し、前記ビア内にPoPランドを形成し、前記ビア内にインターコネクトを形成し、その後、前記めっき部材を除去して、前記PoPランドと前記ダイとを露出させることを有し、前記ダイは前記PoPランドより上に配置される。  (もっと読む)

(もっと読む)

半導体システム

【課題】複数のエリアを有する半導体システムにおいて不使用エリアにおける消費電力を削減する。

【解決手段】内部電源発生回路70b〜70dを其々有する複数のコアチップCC0〜CC7と、コアチップCC0〜CC7を制御するインターフェースチップIFと、を備えた半導体システムであって、前記インターフェースチップIFはコアチップCC0〜CC7の不使用チップ情報DEFを保持する不使用チップ情報保持回路33を備える。コアチップCC0〜CC7は其々対応する不使用チップ情報DEFを不使用チップ情報保持回路33から受け、該不使用チップ情報DEFが不使用状態を示すときには内部電源発生回路70b〜70dを非活性とし、使用状態を示すときには内部電源発生回路70b〜70dを活性とする。これにより、不使用チップにおける無駄な電力消費が削減される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】共通ゲートを有する複数のトランジスタセルをアレー状に配置する構成を持つ不揮発性半導体集積回路装置において、STI領域のパターニング工程でのパターンの変形を防ぐ製造方法を提供する。

【解決手段】半導体メモリ等のメモリセルアレー等の露光において、矩形形状のSTI溝領域エッチング用単位開口を行列状に配置したSTI溝領域エッチング用単位開口群をネガ型レジスト膜28上に露光するに際して、列方向に延びる第1の線状開口群を有する第1の光学マスクを用いた第1の露光ステップと、行方向に延びる第2の線状開口群を有する第2の光学マスクを用いた第2の露光ステップとを含む多重露光を適用する。直行する2方向において、それぞれの方向に対してマスクを用いて露光を行うことで、矩形形状48の端部における近接効果を回避することができ、矩形形状48の端部が丸みを帯びるのを回避することができる。

(もっと読む)

半導体装置

【課題】 セルサイズが小さく、かつ配線接続の自由度が向上できるスタンダードセルを用いた半導体装置を提供する。

【解決手段】 半導体装置はメモリ回路と周辺回路を備え、周辺回路を分割した回路ブロックのそれぞれを、同じ高さを有した矩形で、それぞれが基本論理回路として機能するように構成された複数のスタンダードセルを、同じ高さになるように配置したセルブロックとして構成し、スタンダードセルへの入力信号配線が、メモリセルトランジスタと容量下部電極を接続する容量コンタクトパッド配線を用いて配線される。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極の基板からの抜け落ちを防止する。

【解決手段】半導体装置は、基板80と、基板80に設けられた1又は複数のビアホール91と、1又は複数のビアホール91内にそれぞれ設けられた貫通電極TSVとをそれぞれ有する複数のコアチップと、貫通電極TSVを通じて各コアチップと電気的に接続するインターフェースチップとを備え、ビアホール91は、両端部の径r1,r3に比べて中央部r2の径が大きいボーイング形状部分91aを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】PMOS領域における素子分離膜のライナー窒化膜の除去を行う従来技術による問題を解決した半導体装置およびその製造方法を提供すること。

【解決手段】半導体装置の製造方法は、基板20をエッチングして複数のトレンチを形成するステップと、複数のトレンチ内に第1絶縁膜24Aを埋め込んで第1素子分離膜を形成するステップと、一部のトレンチ(CELL又はPERI NMOS領域のトレンチ)内に埋め込まれた第1絶縁膜24Aをリセスするステップと、リセスされたトレンチの全面にライナー膜26A、27Aを形成するステップと、ライナー膜26A、27Aが形成されたトレンチ内に第2絶縁膜28を埋め込んで第2素子分離膜を形成するステップとを含む。

(もっと読む)

半導体装置の製造方法

【課題】 STIを利用して形成した素子分離膜がウエットエッチング工程により目減りすることを出来るだけ抑制しながら半導体装置を製造する。

【解決手段】 犠牲酸化膜の形成とウエットエッチングによる剥離、及び/又は、二酸化珪素膜の形成とウエットエッチングによる剥離を行う半導体装置の製造プロセスにおいて、犠牲酸化膜及び/又は二酸化珪素膜の形成を、プラズマ処理装置の処理容器内で、酸素を含む処理ガスを用いて生成させたO(1D2)ラジカルが支配的なプラズマにより行う。

(もっと読む)

積層型半導体装置およびチップ自動認識選択回路

【課題】貫通電極によって共通接続された積層型半導体装置を構成する各半導体チップを別々に動作させる。

【解決手段】積層される半導体チップに設けられたチップ自動認識選択回路900a〜900eは、それぞれ、入力されるパルス信号の周期を2倍の周期に変換し出力する周期変更回路12(TFF回路)と、周期変更回路12の入力の論理レベルが、他の全ての周期変更回路12の入力の論理レベルと異なる時間に、半導体チップに対し共通に供給されるチップ選択アドレス信号B0、B1、B2を取り込み、自己チップアドレスとして記憶する自己アドレス記憶回路(ラッチ回路LC1〜LC5)と、チップ選択アドレスと自己チップアドレスとを比較して一致判定を行う判定回路(比較回路13)とを備える。

(もっと読む)

積層型半導体装置

【課題】積層された複数の半導体チップ間で貫通電極切替情報を共有する。

【解決手段】複数の半導体チップ間でデータ転送を行うための複数の貫通電極を互いに共有した積層型半導体装置であって、複数の半導体チップに含まれる第1の半導体チップIFは、複数の貫通電極のうちデータ転送を行う貫通電極を指定する貫通電極切替情報SWを保持し、複数の半導体チップに含まれる第2の半導体チップCC0〜CC7に貫通電極切替情報SWを転送する。本発明によれば、貫通電極切替情報SWが第1の半導体チップIFから第2の半導体チップCC0〜CC7に転送されることから、第2の半導体チップには貫通電極切替情報SWを不揮発的に記憶する回路を設ける必要がない。これにより、第2の半導体チップのチップ面積を縮小することが可能となる。

(もっと読む)

半導体記憶装置及びこれを備える情報処理システム

【課題】複数のコアチップとインターフェースチップからなる半導体記憶装置において、従来の半導体記憶装置との互換性を確保する。

【解決手段】互いに異なるチップ識別情報LIDが割り当てられた複数のコアチップCC0〜CC7と、コアチップCC0〜CC7を制御するインターフェースチップIFとを備える。インターフェースチップIFは、メモリセルを特定するためのアドレス情報ADDを受け、その一部をチップ識別情報LIDと比較するためのチップ選択情報SELとしてコアチップCC0〜CC7に共通に供給する。これにより、コントローラからは単にアドレス空間が拡大されたように見えるだけであることから、従来の半導体記憶装置と同じインターフェースを用いることが可能となる。

(もっと読む)

半導体記憶装置及びこれを備える情報処理システム

【課題】複数のコアチップとインターフェースチップからなる半導体記憶装置において、I/O構成の切り替えを容易とする。

【解決手段】互いに異なるチップ識別情報LIDが割り当てられた複数のコアチップCC0〜CC7と、コアチップCC0〜CC7を制御するインターフェースチップIFとを備える。インターフェースチップIFは、外部との間で同時に入出力する単位外部データのビット数が可変であり、チップ識別情報LIDと比較するためのチップ選択情報SELを、単位外部データのビット数に応じて可変とする。これにより、I/O構成の変更に伴うページ構成の切り替えを不要とすることが可能となる。

(もっと読む)

半導体記憶装置及びデータ処理システム

【課題】複数のコアチップとインターフェースチップからなる半導体記憶装置においてリフレッシュ動作時におけるピーク電流を低減する。

【解決手段】予め互いに異なるチップ情報LIDが付与される複数のコアチップCC0〜CC7を備え、内部リフレッシュコマンドREFaを互いにタイミングの異なる複数のリフレッシュコマンドREFbに分割し、分割されたリフレッシュコマンドREFbのカウント値C2とチップ情報LIDの少なくとも一部とが互いに一致したコアチップにおいてリフレッシュ動作が実行される。これにより、複数のコアチップCC0〜CC7に内部リフレッシュコマンドREFbが共通に供給される場合であっても、各コアチップにおけるリフレッシュ動作のタイミングをずらすことが可能となる。これにより、リフレッシュ動作時におけるピーク電流を低減することが可能となる。

(もっと読む)

81 - 100 / 401

[ Back to top ]