Fターム[5F083AD17]の内容

Fターム[5F083AD17]に分類される特許

1 - 20 / 104

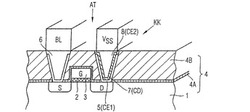

半導体メモリセルおよびその製造方法

【課題】ストレージキャパシタが選択トランジスタ(AT)に接続されている半導体メモリセルの集積度を向上させながら、製造コストを低減できる半導体メモリセルおよびその製造方法を提供する。

【解決手段】ストレージキャパシタは、ソース領域Sまたはドレイン領域Dのための少なくとも1つのコンタクトホールにおいて、コンタクトホールキャパシタKKとして形成されている。このような半導体メモリセルは、特にコスト効率よく製造することができ、かつ高集積度を達成できる。

(もっと読む)

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタのSCEに対する免疫性を向上させると同時に、分岐点での重なりを増加させる方法及び構造の提供。

【解決手段】基板102は第1活性領域104と第2活性領域106とを有し、浅溝分離(STI)領域108によって分離される。バッファ層112は応力緩和層として機能しハードマスク層114が形成される。基板102の表面に分離領域108を部分的に網羅するように凹部118を設ける。ゲート誘電体120が凹部118に形成された後第一ドーパントインプラント122により、ドープ済みチャンネル領域124が形成される。インプラントはハードマスク114を貫通しないので、凹部118の下に形成されたドープ済みチャンネル領域124中のドーパント濃度は最も高くなる。ドープ済みチャンネル領域124はトランジスタのオン・オフを切り替える閾値電圧を変調する。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチ内に埋め込まれたシリコン層と複数のトレンチ間の半導体基板上に形成されたシリコン層とを同じイオン注入を行ない導電層とすること。

【解決手段】半導体基板10に複数のトレンチ30と、前記複数のトレンチ間の前記半導体基板上に第1キャパシタ絶縁膜22を介し第1シリコン層24と、を形成する工程と、前記複数のトレンチ内に埋め込み絶縁膜36を埋め込む工程と、前記埋め込み絶縁膜を前記複数のトレンチの側面に第2キャパシタ絶縁膜33が残存するように除去し、前記埋め込み酸化膜内に凹部を形成する工程と、前記凹部内の前記第2キャパシタ絶縁膜上と前記複数のトレンチ間の前記第1シリコン層上とに第2シリコン層40を直接形成する工程と、前記凹部内および前記第1キャパシタ絶縁膜上に形成された前記第2シリコン層内に不純物を同時にイオン注入する工程と、を含むことを特徴とする半導体装置の製造方法。

(もっと読む)

半導体構造体及びその製造方法

【課題】 埋め込み型DRAM構造のための半導体構造体及びその製造方法を提供する。

【解決手段】 ノード誘電体及び深いトレンチを充填する導電性トレンチ充填領域がセミコンダクター・オン・インシュレータ(SOI)層の上面とほぼ同一面となる深さにまで窪まされる。浅いトレンチ分離部が深いトレンチの上部の一方の側に形成され、一方深いトレンチの上部の他方の側は、導電性充填領域の半導体材料の露出された表面となる。選択的エピタキシャル成長プロセスが、レイズド・ソース領域及びレイズド・ストラップ領域を付着するために行われる。レイズド・ソース領域は、SOI層内のプレーナ・ソース領域上に直接形成され、そしてレイズド・ストラップ領域は、導電性充填領域上に直接形成される。レイズド・ストラップ領域は、プレーナ・ソース領域及び導電性充填領域の間の導電性通路を与えるためにレイズド・ソース領域に接触する。

(もっと読む)

半導体装置の製造方法及びその製造方法による半導体装置

【課題】隣接するトレンチのストレージノード電極同士のショートを防止する半導体装置を提供する。

【解決手段】半導体基板1の複数のトレンチ8の内部表面に第1のポリシリコン膜12を堆積し、第1のポリシリコン膜12表面に不純物ドープのシリカガラス膜13を堆積した後、シリカガラス膜13をプレート電極形成領域の深さまでエッチングし、シリカガラス膜13から導電型不純物を導入して導電型不純物含有ポリシリコン膜16aと拡散層16bとを有するプレート電極16を形成する。次にトレンチ内部表面にキャパシタ絶縁膜17を形成後、トレンチ8内部に第1の導電膜を堆積し、ストレージノード電極18を形成する。その後、第1及び第2導電層21,22でストレージノード電極とセルの拡散層とを接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ型キャパシタと接続する拡散層ソースの幅のばらつきを抑制する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板11表面に垂直に形成されたキャパシタ用トレンチ12の半導体基板11表面側に形成されたn型の埋め込み多結晶シリコン19と、半導体基板11に埋め込まれて溝状をなし、埋め込み多結晶シリコン19を被う素子分離領域25の曲面22に連接する側面とほぼ面一な垂直面を内側表面とするゲート絶縁膜31と、底面及び底面側の対向する両側面をゲート絶縁膜31と接する埋め込み型のゲート電極40と、埋め込み多結晶シリコン19とゲート絶縁膜31との間及び下方にあり、n型の不純物を有する半導体基板11に形成された埋め込み拡散層47と、埋め込み拡散層47と対向する側にあり、ゲート絶縁膜31の側面に接し、半導体基板11の表面から内側にn型の不純物を有する表面拡散層45とを有する。

(もっと読む)

メモリ装置及びメモリ装置の製造方法

【課題】キャパシタンスを確保することが可能なメモリ装置及びその製造方法を提供する。

【解決手段】基板に、基板の表面に平行な断面がほぼC字型であるC字型ディープトレンチキャパシタ202と、C字型ディープトレンチキャパシタ202に連結されているワードライン206,206…とが形成されている。メモリ装置200において、それぞれのメモリセルは、C字型ディープトレンチキャパシタ202の外縁だけでなく内縁もキャパシタンスを提供するために用いられる。

(もっと読む)

集積回路の製造方法

【課題】異なる基材領域又はいくつかのトレンチの底部及び各側壁部を覆う異なる酸化被膜の形成に異なる酸化処理を備える、集積回路を製造する方法を提供する。

【解決手段】表面を有する半導体基板10を準備するステップと、少なくとも一つの注入種が、前記表面の第二の部分区域14と比較すると前記表面の第一の部分区域12に近接して特に注入されるようなイオン注入処理を実行するステップと、前記表面の前記第一の部分区域を覆う第一の膜厚を有する第一の酸化被膜32と前記表面の前記第二の部分区域を覆う第二の膜厚を有する第二の酸化被膜36とを形成するように、単一の酸化処理を実行するステップであって、前記第一の膜厚が前記第二の膜厚と異なるステップと、を備える。

(もっと読む)

スプリット仕事関数ゲートを含むMOSFETを有する集積回路

【課題】ゲート誘起ドレインリーク電流が少ない電界効果トランジスタ、および、ゲート電極とソース/ドレイン領域との間に薄い絶縁体構造物を含む集積回路を提供する。

【解決手段】トランジスタ542のゲート電極は、ゲート電極とチャネル領域512との間の第1のフラットバンド電圧を決定する主部532と第1の側部535とを含む。この第1の側部は、上記主部に接触すると共に、上記ゲート電極と第1のソース/ドレイン領域514,516との間の第2のフラットバンド電圧を決定する。上記第1のフラットバンド電圧および上記第2のフラットバンド電圧は、少なくとも0.1eVだけ異なる。

(もっと読む)

半導体記憶装置

【課題】十分なデータ保持特性を有する半導体記憶装置を提供する。

【解決手段】基板14に形成され、順に連接した第1乃至第3領域15、16、17を有する半導体層18と、第2領域16にゲート絶縁膜19を介して形成されたゲート電極20と、ゲート電極20をゲート長方向に挟むように第1および第3領域15、17内にそれぞれ形成され、キャリア濃度が第2領域16より高く、且つ半導体層18と同じ導電型のソースおよびドレインとを備えたセルトランジスタ11と、一端が第1領域15のソースに接続され、他端が共通配線22に接続されたキャパシタ21と、を具備する。ゲート電極20に電源電圧を印加したときに、ゲート絶縁膜19下の第2領域16に形成されるMOSキャパシタの空乏層の幅Wを、W=√(2εφ/qNa)としたとき、ゲート長Lgと直交する方向の第2領域16の厚さTsiが、空乏層の幅Wより小さい。

(もっと読む)

半導体装置およびその製造方法

【課題】簡便な製造プロセスで形成される高性能なMOSトランジスタを実現する。

【解決手段】本発明の半導体装置およびその製造方法は、半導体基板表面に形成された素子分離領域12によって分離されたMOSトランジスタ14と、MOSトランジスタ14のゲート電極18の直下に形成され、MOSトランジスタ14のチャネル領域16をゲート酸化膜17を介して挟み込むように素子分離領域12の酸化膜中に形成されたトレンチ13と、トレンチ13に埋め込まれた導電性材料よりなる埋め込み電極18を有する。

(もっと読む)

半導体構造体及び半導体構造体を形成する方法

【課題】 改善されたディープ・トレンチ・キャパシタ構造体、及びこのディープ・トレンチ・キャパシタ構造体を組み込むメモリ・デバイスを提供すること。

【解決手段】 後のディープ・トレンチ・エッチング・プロセス中に絶縁体層(202、302)が完全な状態のままであり、かつ、随意的に、ディープ・トレンチ・キャパシタのディープ・トレンチ(250、350)が、異なる深さにおいて異なる形状及びサイズを有するように、半導体オン・インシュレータ(SOI)ウェハ上にディープ・トレンチ・キャパシタ及びメモリ・デバイスが形成される。異なる深さにおいて異なる形状及びサイズを有するディープ・トレンチ(250、350)を形成することによって、キャパシタ(210、310)の容量を選択的に変え、キャパシタ(210、310)をメモリ・デバイス内のトランジスタ(220、320)に接続する埋め込み導電性ストラップ(230、330)の抵抗を低減させることができる。

(もっと読む)

自己整合方式でリセスゲートMOSトランジスタ素子を製作する方法

【課題】自己整合方式でリセスゲートMOSトランジスタ素子を製作する方法を提供する。

【解決手段】本発明による方法で製作されたMOSトランジスタ素子は、側壁と底部を有するゲート溝を備える基板と、ゲート溝の側壁に設けられるドレイン/ソースドープ領域と、ゲート溝の底部に設けられるゲートチャネル領域と、ゲート溝の側壁と底部に設けられ、ゲート溝の側壁における第一膜厚とゲート溝の底部における第二膜厚が相違するゲート酸化膜と、ゲート溝に埋め込まれるゲート導体とを含む。

(もっと読む)

半導体装置とその製造方法

【課題】リーク電流を低減することが可能な半導体装置とその製造方法を提供すること。

【解決手段】複数のセル活性領域102をセル領域Cに備えたシリコン基板1と、複数のセル活性領域102の間のシリコン基板1に形成された素子分離溝1aと、素子分離溝1aに形成されたキャパシタ誘電体膜21と、キャパシタ誘電体膜21上に形成され、シリコン基板1及びキャパシタ誘電体膜21と共にキャパシタQを構成するキャパシタ上部電極23bとを有し、セル領域Cの横のシリコン基板1にダミー活性領域103を設けたことを特徴とする半導体装置による。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチキャパシタを有するDRAMのセルトランジスタのコンタクトプラグとストラップとの間の短絡を防止した半導体装置およびその製造方法を提供する。

【解決手段】半導体基板11に形成されたトレンチキャパシタ14と、半導体基板11に、絶縁体によりトレンチキャパシタ14と分離して形成され、ゲート電極15と第1拡散層16および第2拡散層17とを有するセルトランジスタ13と、トレンチキャパシタ14および第1拡散層16の上に形成され、トレンチキャパシタ14とセルトランジスタ13とを電気的に接続する導電膜21と、導電膜21上に形成された絶縁性保護膜22と、絶縁性保護膜22およびセルトランジスタ13上に形成され、異方性のエッチング速度が絶縁性保護膜22より大きい層間絶縁膜23と、第2拡散層17を層間絶縁膜23上に形成された金属配線に電気的に接続するためのコンタクトプラグ24と、を具備する。

(もっと読む)

半導体記憶装置

【課題】 消費電力が抑制された半導体記憶装置を提供する。

【解決手段】 半導体記憶装置は、データの読み出しおよびデータの書き込みおよびリフレッシュを含む動作が行われる第1モードと、データの読み出しおよびデータの書き込み無しにリフレッシュが自律的に繰り返される第2モードと、を有する。素子分離領域12は、半導体基板11の表面に形成され、素子領域を区画し、表面に絶縁膜31を有し、内部において導電体32を含む。複数のメモリセルは、素子領域に形成され、それぞれがキャパシタ14とMOSトランジスタ16とを含む。電位発生回路4は、導電体に第1モードにおいて第1電位を印加し、第2モードにおいて第1電位より高い第2電位を印加する。

(もっと読む)

集積回路および集積回路の形成方法

【課題】同一半導体基板内に、高いしきい値電圧、または低いしきい値電圧を有する複数のトランジスタを有用な集積回路、およびその製造方法を提供すること。

【解決手段】第1ゲート電極を有する第1タイプのトランジスタと、第2ゲート電極181を有する第2タイプのトランジスタ183とを含む。上記第1ゲート電極は、半導体基板内に設定された第1ゲート用溝内に形成され、上記第2ゲート電極は、上記半導体基板内に設定された第2ゲート用溝180内に形成されている。上記第1ゲート電極は、2つの互いに隣り合う各第1分離用トレンチ間のスペースを完全に充填している。上記第2ゲート電極は、2つの互いに隣り合う各第2分離用トレンチ間のスペースを部分的に充填している。上記第2ゲート電極と、上記互いに隣り合う各第2分離用トレンチとのそれぞれの間に、各基板部分がそれぞれ配置されている。

(もっと読む)

半導体記憶装置

【課題】微細化が進展しても、データ書き込み時には閾値が低く、“1”データ保持時には閾値が高くすることができ、良好なデータ書き込み特性および良好なデータ保持特性の両立を図ることが可能な半導体記憶装置を提供する。

【解決手段】ゲート電極G1の側壁には側壁絶縁膜35が形成される。n型拡散層36の表面にはビット線コンタクト51が形成され、n型拡散層27は、埋め込みストラップ41、及びポリシリコン電極22Aを介してストレージノード電極22に接続されている。側壁絶縁膜35は、トレンチキャパシタ側、即ちストレージノード電極22側の厚さが、ビット線コンタクト51側の厚さよりも大きくされている。

(もっと読む)

メモリセルアレイおよびその形成方法

【課題】メモリセル領域が狭められたDRAMメモリセルアレイを提供する。

【解決手段】各メモリセルは、ストレージキャパシタ3、アクセス用のトランジスタ16、第1方向に沿って配置された複数の各ビット線2、上記第1方向に直交する第2方向に沿って配置された複数の各ワード線8、表面を有する半導体基板1、上記半導体基板に形成され、上記第2方向に伸びる複数の各能動領域を有する。上記アクセス用の各トランジスタは、上記各能動領域無いに部分的に形成されており、かつ、上記各ストレージキャパシタの対応する一つと対応する各ビット線とを電気的に接続する。上記アクセス用の各トランジスタのゲート電極19は、対応するワード線8に接続されている。上記ストレージキャパシタのキャパシタ用の誘電体38は、比誘電率が8を超えたものである。上記各ワード線は、上記各ビット線の上方に配置されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 素子構造の微細化・低駆動電圧化によって顕在化したMOSFETの閾値のバラつきによる、DRAMのリフレッシュ不良を抑制する。

【解決手段】 DRAMにおいて、セルトランジスタのバックゲートに印加するバックバイアス電位の設定値を記録する第1の手段と、第1の手段に記録された前記バックバイアス電位の設定値に基づいてバックバイアス電位を生成して、生成したバックバイアス電位を前記バックゲートに供給する第2の手段とを有し、セルトランジスタと同一構造で且つ同一工程で同時に製作されたMOSFETの閾値が、セルトランジスタが具備すべき目標値より大きい場合に、前記目標値に対するバックバイアス電位より浅い値が第2の手段に記録されてなる。

(もっと読む)

1 - 20 / 104

[ Back to top ]