Fターム[5F083BS47]の内容

Fターム[5F083BS47]に分類される特許

21 - 40 / 57

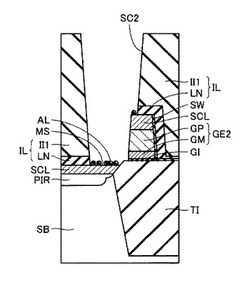

半導体装置の洗浄方法

【課題】ゲートメタル材料の溶解抑制と良好なコンタクト抵抗取得とを両立可能な半導体装置の洗浄方法を提供する。

【解決手段】半導体装置の洗浄方法は、以下の工程を備えている。シリコンを含み、かつ主表面MSを有する半導体基板SBが準備される。主表面MSの上にメタル層GMとシリコン層GPとを下から順に積層した積層ゲートGE2が形成される。主表面MSとシリコン層GP表面との各々にシリサイド層SCLが形成される。主表面MSと積層ゲートGE2表面との各々のシリサイド層SCLの上に絶縁層ILが形成される。半導体基板SBの主表面MSと積層ゲートGE2の表面との各々のシリサイド層SCLが絶縁層ILから露出するようにシェアードコンタクトホールSC2が絶縁層ILに形成される。シェアードコンタクトホールSC2に硫酸洗浄、過酸化水素水洗浄およびAPM洗浄をそれぞれ別工程で行うことによりシェアードコンタクトホールSC2に形成された変質層ALが除去される。

(もっと読む)

半導体装置及びその製造方法

【課題】4個の島状半導体を用いてSRAMを構成することにより、高集積なSGTを用いたSRAMからなる半導体装置を提供することを目的とする。

【解決手段】第1の島状半導体層の周囲上に少なくとも一部に接して第1のゲート絶縁膜が存在し、第1のゲート絶縁膜に第1のゲート電極の一面が接し、該第1のゲート電極の他面に第2のゲート絶縁膜が接し、第2のゲート絶縁膜に少なくとも第2の半導体層が接して、第1の島状半導体層の上部に配置された第1の第1導電型高濃度半導体層と、第1の島状半導体層の下部に配置された第2の第1導電型高濃度半導体層と、第2の半導体層の上部に配置された第1の第2導電型高濃度半導体層と、第2の半導体層の下部に配置された第2の第2導電型高濃度半導体層と、を有することを特徴とするインバータを用いたSRAMにより、上記課題を解決する。

(もっと読む)

半導体集積回路

【課題】同時に読み書きを行うデュアルポートSRAMにおいて、データの読み出し速度を改善する。

【解決手段】各々のメモリセルは、第1及び第2のストアノードにデータを保持する第1及び第2のインバータと、第1のビット線対と第1及び第2のストアノードとの間にそれぞれ接続された第1及び第2のNチャネルトランジスタによって構成される書き込み/読み出しポートと、第1のストアノードのデータをゲートに受ける第1のPチャネルトランジスタ、第2のビット線対の一方と第1のPチャネルトランジスタのドレインとの間に接続された第2のPチャネルトランジスタ、第2のストアノードのデータをゲートに受ける第3のPチャネルトランジスタ、第2のビット線対の他方と第3のPチャネルトランジスタのドレインとの間に接続された第4のPチャネルトランジスタによって構成される読み出しポートとを具備する。

(もっと読む)

半導体記憶装置

【課題】セルサイズを縮小化しつつ、読み出し特性を向上させることができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のSRAMセルMCがマトリクス状に配置されたメモリセルアレイを有する。SRAMセルMCは、第1のインバータINV1と、第1のインバータINV1と入力端及び出力端が相互に接続された第2のインバータINV2と、第1のインバータINV1又は第2のインバータINV2のいずれか一方の入力端にゲートが接続された第1の読み出しドライバトランジスタQrd1と、第1の読み出しドライバトランジスタQrd1を介して第1の読み出しビット線RBLと接続され、ゲートが読み出しワード線RWLに接続された第1の読み出し転送トランジスタQrx1とを備える。第1の読み出し転送トランジスタQrx1は、メモリセルアレイ内の少なくとも2つのSRAMセルMC1、MC2の間で共有される。

(もっと読む)

半導体装置

【課題】微細化が進んだ半導体装置の短チャネル効果を防ぎ、特性を向上させることができる半導体装置の提供を課題とする。

【解決手段】単結晶シリコン基板上に形成された酸化膜と、酸化膜上に形成された単結晶シリコン層と、単結晶シリコン層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極を有する半導体装置であって、単結晶シリコン層はチャネル形成領域、ソース領域、ドレイン領域を有し、チャネル形成領域には、ソース領域、ドレイン領域とは逆の導電型の不純物元素が添加され、チャネル形成領域の不純物元素が添加された領域は、上面から見て主軸がソース領域からドレイン領域にかけて伸びるフィッシュボーン形状を有し、フィッシュボーン形状は単結晶シリコン層の表面から底部にかけて形成され、チャネル形成領域の不純物元素が添加された領域は、空乏層を抑止する機能を有することを特徴としている半導体装置を提供する。

(もっと読む)

半導体集積回路装置

【課題】ラッチ型メモリセルのラッチ部のサイズを増大させることなく、データ保持特性を改善する。

【解決手段】ラッチ型メモリセルの記憶ノードを構成するゲート電極配線(21a,21c)と交差する方向に、フラッシュメモリセルトランジスタの固有の配線と同一配線層の導電線(26a,26b)を連続的に延在させて配置する。ゲート電極配線と導電線の交差部において容量を形成し、導電線を固定電位に維持する。

(もっと読む)

半導体装置及びその製造方法

【課題】SRAMにおいてNMOS及びPMOSトランジスタのバランスを確保して、PMOSトランジスタの閾値電圧を高くできる半導体装置及びその製造方法を提供する。

【解決手段】メモリ領域において、基板の第1半導体領域(12,13)の第1チャネル形成領域上に第1ゲート絶縁膜(20,21)を介して第1ゲート電極が形成され、第1半導体領域に第1ソースドレイン領域(16,17)が形成されて第1トランジスタが形成され、ロジック領域において、基板の第2半導体領域(14,15)の第2チャネル形成領域上に第2ゲート絶縁膜(22,23)を介して第2ゲート電極が形成され、第2半導体領域に第2ソースドレイン領域(18,19)が形成されて第2トランジスタが形成され、第1ゲート電極の第1ゲート絶縁膜に接する部分が金属(40,41)からなり、第2ゲート電極の第2ゲート絶縁膜に接する部分が半導体(26,27)からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの閾値ばらつきの増大を抑制する半導体装置の提供。

【解決手段】SRAMメモリセルであって、第1のゲート電極Gp1と第1のソース及びドレイン拡散層とを有する第1のpMOSトランジスタTp1と、第1のゲート電極と分断された第2のゲート電極Gn1と第2のソース及びドレイン拡散層とを有する第1のnMOSトランジスタTn1と、第3のゲート電極Gp2と第3のソース及びドレイン拡散層とを有する第2のpMOSトランジスタTp2と、第4のゲート電極Gn2と第4のソース及びドレイン拡散層とを有する第2のnMOSトランジスタTn2と、第1のソース/ドレイン拡散層の一方に接続するソース/ドレインコンタクトCS1と、第1のゲート電極と第3のソース/ドレイン拡散層を接続させるコンタクトSC1と、素子分離絶縁膜上に形成され、第1及び第2のゲート電極を電気的に接続するコンタクトC1とを具備する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】シェアードコンタクトを備えるフルCMOS型のSRAMメモリセルにおいて、安定した低電圧動作を得る。

【解決手段】半導体記憶装置は、第1の配線が、第3のドレイン活性領域と第2のゲート電極用配線を開口するように配置された一つの第1のコンタクトを介して、第3のドレイン活性領域と第2のゲート電極用配線に電気的に接続されるとともに、第2の配線が、第4のドレイン活性領域と第1のゲート電極用配線を開口するように配置された一つの第2のコンタクトを介して、第4のドレイン活性領域と第1のゲート電極用配線に電気的に接続されており、第1から第4のいずれかのドレイン活性領域と離れた部分もしくは連続した部分に活性領域を備え、活性領域と前記第1ゲート若しくは前記第2ゲート電極用配線が重なる。

(もっと読む)

半導体記憶装置

【課題】レイアウト面積の増大を抑制しつつ、デュアルポートSRAMのビットセルの縦横のアスペクトの不均衡を低減する。

【解決手段】Aポート用伝送トランジスタFA1、FA2を互いに隣接させてビットセルの一端に配置するとともに、Bポート用伝送トランジスタFB1、FB2を互いに隣接させてビットセルの他端に配置し、Aポート用伝送トランジスタFA1、FA2のゲート電極を共有させることで、Aポート用ビット線BLAc、BLAtを互いに隣接させて配置し、Bポート用伝送トランジスタFB1、FB2のゲート電極を共有させることで、Bポート用ビット線BLBc、BLBtを互いに隣接させて配置する。

(もっと読む)

半導体記憶装置

【課題】不揮発性メモリの高速化を小面積で実現する。

【解決手段】例えば、SRAMに代表される低集積で高速なメモリアレイ53を半導体基板上に形成し、その上層にフラッシュメモリに代表される高集積で低速なメモリアレイ54を形成する。メモリアレイ54は、各メモリセルのチャネルが縦方向に形成され、小面積での大容量化が図られている。メモリアレイ53とメモリアレイ54は、データ線等が適宜共通化されており、外部からメモリアレイ54に書き込みを行う際には、メモリアレイ53に書き込みを行い、メモリアレイ53からメモリアレイ54に転送を行う。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】微細で精度が高く、歩留まりが向上した半導体装置を提供する。

【解決手段】半導体装置は、第1トランジスタ2と第2トランジスタ5とを具備する。第1トランジスタ2は、半導体基板100上に第1ゲート絶縁膜51を介して形成された第1ゲート電極21と第1ソース・ドレイン領域31と第1共通ソース・ドレイン領域30とを備える。第2トランジスタ5は、半導体基板100上に第2ゲート絶縁膜51を介して形成された第2ゲート電極22と第2ソース・ドレイン領域31と第1共通ソース・ドレイン領域30とを備える。第1ゲート電極21及び第2ゲート電極22は、第1共通ソース・ドレイン領域30のコンタクトである第1ノード電極41の両側壁に設けられている。

(もっと読む)

半導体記憶装置

【課題】簡単な構成で大きな動作マージンを確保できかつ動作特性を向上した半導体記憶装置を提供する。

【解決手段】メモリセル内のラッチ部に含まれるトランジスタ(N1)のしきい値電圧(Vth)を動的に制御して、そのトランジスタの動作特性を動的に制御し、データの書き込み特性を向上させる。しきい値電圧を制御するために、トランジスタ(N1)のボディにバイアス信号を印加する。このバイアス信号としてビット線(WBL)の信号を使用する。データ書き込み時において事前にビット線(WBL)により伝達される書き込みデータの信号に基づき、メモリセル内のトランジスタ(N1)のボディにバイアスを印加し、トランジスタ(N1)のしきい値(Vth)を低下させる。

(もっと読む)

半導体集積回路装置

【課題】従来のSRAMセルは、セル内の異なる領域に形成されたウエル領域に電位差が生じる問題があった。

【解決手段】本発明の半導体集積回路装置は、第1のPウエル領域と、第2のPウエル領域と、第1のPウエル領域と第2のPウエル領域との間に位置するNウエル領域と、から構成されるSRAMセルを備える半導体集積回路装置であって、SRAMセルは、第1のPウエル領域に電位を供給し、ウエルコンタクトWCに接続される第1のタップP型拡散層と、第2のPウエル領域に電位を供給し、ウエルコンタクトWCに接続される第2のタップP型拡散層と、を有し、第1、第2のタップP型拡散層は、SRAMセルのレイアウトの中心に対して略対称位置上に配置され、少なくともその一部がSRAMセル内のNウエル領域の上方を通過する第1の金属配線27によって互いに接続されるものである。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】製造コスト増加を抑制することができるSRAM型半導体記憶装置の提供。

【解決手段】データを記憶する記憶回路と、第1アクセストランジスタと第2アクセストランジスタとを備え、データの読み出しと書き込みを制御するアクセス制御回路と、記憶回路とアクセス制御回路とに接地電圧を供給する接地電圧供給領域と、第1アクセストランジスタに備えられた第1ゲート電極と第1アクセストランジスタに備えられた第2ゲート電極とを接続する第2導電型のポリシリコン8とを具備するSRAM型半導体記憶装置を構成する。その接地電圧供給領域15は、接地電圧を供給する接地電圧供給コンタクトに接続され、一部分が第2導電型の半導体22であり一部分を除く他の部分が第1導電型の半導体15で構成される。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、伝達トランジスタにおける駆動能力のばらつきを抑制しながら、伝達トランジスタの駆動能力を向上させることができない問題があった。

【解決手段】本発明の半導体装置は、駆動トランジスタ30及び負荷トランジスタ40からなる第1のインバータと、駆動トランジスタ31及び負荷トランジスタ41からなる第2のインバータと、第1のインバータの出力端子とビット線対の一方との間に設けられた伝達トランジスタ10と、第2のインバータの出力端子とビット線対の他方との間に設けられた伝達トランジスタ11と、駆動トランジスタ30と伝達トランジスタ11を絶縁する絶縁トランジスタ50とを有し、伝達トランジスタ10、伝達トランジスタ11、駆動トランジスタ30及び絶縁トランジスタ50が連続した活性領域で形成され、絶縁トランジスタ50は駆動トランジスタ30と伝達トランジスタ11の間に設けられるものである。

(もっと読む)

半導体装置の製造方法および半導体記憶装置の製造方法

【課題】セルサイズを縮小することのできるSRAMを提供する。

【解決手段】駆動MISFETおよび転送MISFETの上部には、縦型MISFET

が形成されている。縦型MISFETは、下部半導体層(ドレイン)57、中間半導体層

58、上部半導体層(ソース)59を積層した四角柱状の積層体(P1、P2)と、この積層体(P1、P2)の側壁にゲート絶縁膜63を介して形成されたゲート電極66とによって構成されている。縦型MISFETは、下部半導体層57がドレインを構成し、中間半導体層58が基板(チャネル領域)を構成し、上部半導体層59がソースを構成している。下部半導体層57、中間半導体層58、上部半導体層59の夫々は、シリコン膜で構成され、下部半導体層57および上部半導体層59はp型にドープされ、p型シリコン膜で構成される。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】過渡応答が良いノイズ低減対策用のキャパシタを歩留まり良く形成する。

【解決手段】電源電位(VDD)が印加される配線Maおよび接地電位(GND)が印加される配線Mb上に窒化シリコン膜を堆積することによりキャパシタ絶縁膜CZを形成し、このキャパシタ絶縁膜CZ上にタングステン膜を堆積し、エッチングすることによりフローティング電極FEを形成する。このフローティング電極FEは、配線MaおよびMb上に、分割された状態で延在している。この配線Ma、Mb、キャパシタ絶縁膜CZおよびフローティング電極FEからなるキャパシタCa1とCa2により電源ノイズを低減することができる。また、フローティング電極FEを分割したので、歩留まりの向上を図ることができる。

(もっと読む)

半導体装置

【課題】フィン領域の寸法管理が容易なダブルゲート型FinFETを有する半導体装置を提供する。

【解決手段】半導体基板上に直線状に形成された突起状の半導体層からなるフィン領域AA1−1、AA1−2と、フィン領域の側面上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、フィン領域AA1−1、AA1−2と交差するように配置されたゲート電極GC1−1と、ゲート電極下のフィン領域の側面に形成されるチャネル領域を挟むように、フィン領域内に形成されたソース領域及びドレイン領域と、フィン領域AA1−1、AA1−2上に形成されたコンタクト材とを有する。コンタクト材が接続されたフィン領域上のコンタクト領域C1−2は、チャネル領域のチャネル長方向に延伸して配置されたフィン領域と、チャネル長方向と異なる方向に曲がって配置されたフィン領域とに跨っている。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜に開口された接続孔の内部に、チタン膜上に窒化チタン膜が形成された積層構造のバリアメタル膜を介して金属膜を埋め込んだ接続部における不具合を回避する。

【解決手段】コンタクトホールC1を形成して、その底部にニッケルシリサイド層14を露出させた後、TiCl4ガスを用いた熱反応により熱反応Ti膜21aを形成し、TiCl4ガスを用いたプラズマ反応によりプラズマ反応Ti膜21bを形成し、H2ガスを用いたプラズマ処理を施して、プラズマ反応Ti膜21bの塩素濃度を低減すると同時に、ニッケルシリサイド層14の表面の酸化膜を還元し、NH3ガスを用いた熱窒化処理及びNH3ガスを用いたプラズマ処理を施して、プラズマ反応Ti膜21bの表面に窒素リッチTiN膜21cを形成すると同時に、ニッケルシリサイド層14の表面の酸化膜を還元する。

(もっと読む)

21 - 40 / 57

[ Back to top ]