Fターム[5F083CR15]の内容

半導体メモリ (164,393) | ROM(EPROM、EEPROMを除く) (635) | PROM(Programmable ROM) (484) | 抵抗値変化型ROM (100)

Fターム[5F083CR15]に分類される特許

1 - 20 / 100

半導体装置

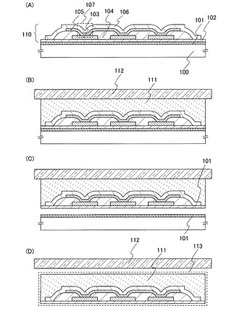

【課題】有機化合物を含む層を有する素子が設けられたフレキシブルな記憶装置及び半導

体装置を歩留まり高く作製する。また、信頼性の高いフレキシブルな記憶装置及び半導体

装置を歩留まり高く作製する。

【解決手段】剥離層を有する基板上に素子層及び素子層を封止する絶縁層を有する積層体

を形成し、剥離層から積層体を剥離してフレキシブルな記憶装置及び半導体装置を作製す

る方法であって、素子層において第1の電極層及び第2の電極層からなる一対の電極間に

有機化合物を含む層を有する記憶素子を含み、少なくとも一方の電極層はスズを含む合金

層で形成する。また、第1の電極層及び第2の電極層からなる一対の電極間に有機化合物

を含む層を有する記憶素子を含み、少なくとも一方の電極層はスズを含む合金層で形成さ

れるフレキシブルな記憶装置及び半導体装置である。

(もっと読む)

半導体装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

二重層フローティングゲートを備えているEPROMセル

【課題】インクジェットペンコントロールチップの既存の層を利用して製造できるEPROMを提供する。

【解決手段】EPROMセル70は、ソース領域及びドレイン領域を有する半導体基板52と、第1の金属層60と電気的に相互接続されている半導体ポリシリコン層56を含むフローティングゲート72と、第2の金属層64を含むコントロールゲートとを備えている。フローティングゲート72は、ソース領域及びドレイン領域に隣接して配置され、第1の誘電体層54によって半導体基板52から分離され、コントロールゲートの第2の金属層64は、第1の金属層60との間にある第2の誘電体層62を介して、第1の金属層60と容量結合されている。

(もっと読む)

半導体装置

【課題】非接触でデータの送受信が可能な半導体装置は、鉄道乗車カードや電子マネーカ

ードなどの一部では普及しているが、さらなる普及のためには、安価な半導体装置を提供

することが急務の課題であった。上記の実情を鑑み、単純な構造のメモリを含む半導体装

置を提供して、安価な半導体装置及びその作製方法の提供を課題とする。

【解決手段】有機化合物を含む層を有するメモリとし、メモリ素子部に設けるTFTのソ

ース電極またはドレイン電極をエッチングにより加工し、メモリのビット線を構成する導

電層とする。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装

置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び

有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電

層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあ

わせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

半導体装置

【課題】コイル状のアンテナ部の内部に、占有面積が大きい導電層が設けられていると、電源を安定して供給することが困難になっていた。

【解決手段】記憶回路部とコイル状のアンテナ部とを積層して配置することにより、記憶回路部が含む占有面積の大きい導電層に電流が流れてしまうことを防止することができ、省電力化を図ることができる。また、記憶回路部とコイル状のアンテナ部とを積層して配置することにより、スペースを有効に利用することができる。従って、半導体装置の小型化を実現することができる。

(もっと読む)

半導体装置

【課題】不揮発性であって、作製が簡単であり、追記が可能な記憶回路を有する半導体装置の提供を課題とする。

【解決手段】本発明の半導体装置は、複数のトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記複数のトランジスタのうちの1つの上に設けられた記憶素子及びアンテナとして機能する導電層とを有し、前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、アンテナとして機能する前記導電層と前記複数のトランジスタのソース配線又はドレイン配線として機能する導電層とは、同じ層上に設けられていることを特徴とする。

(もっと読む)

側壁構造化スイッチャブル抵抗器セル

【課題】抵抗を大きくして感知されやすくするとともに、リセット電流を小さくし、製造中の損傷も抑制できる抵抗率スイッチング素子を提供する。

【解決手段】第1の伝導性電極28を形成するステップと、第1の伝導性電極28の上に絶縁構造13を形成するステップと、絶縁構造の側壁上に抵抗率スイッチング素子14を形成するステップと、抵抗率スイッチング素子14の上に第2の伝導性電極26を形成するステップと、第1の伝導性電極28および第2の伝導性電極26の間に抵抗率スイッチング素子14と直列にステアリング素子を形成するステップと、を含み、第1の伝導性電極28から第2の伝導性電極26への第1の方向における抵抗率スイッチング素子14の高さTは第1の方向に垂直な第2の方向における抵抗率スイッチング素子14の厚さIより大きい。

(もっと読む)

半導体装置

【課題】上下電極間に有機化合物を設けて記憶素子を形成するが、有機化合物を含む層の

上に電極を形成した場合、電極の形成時の温度によっては有機化合物を含む層への影響が

あるため温度に制限がある。この温度の制限のため形成方法が限定され、希望通りの電極

を形成することができず、素子の微細化を阻害している問題があった。

【解決手段】絶縁表面を有する基板上に記憶素子及びスイッチング素子が配置された半導

体装置とし、前記素子は、同一平面に配置された第1の電極と第2の電極と有機化合物を

含む層とを有し、前記有機化合物を含む層は前記第1の電極と前記第2の電極との間に形

成され、電流は前記第1の電極から前記第2の電極へと流れ、前記第1の電極は、前記ス

イッチング素子と電気的に接続されている半導体装置である。

(もっと読む)

記憶素子およびその製造方法、並びに記憶装置

【課題】良好な絶縁耐圧性を有する記憶素子を提供する。

【解決手段】下部電極、記憶層および上部電極をこの順に有し、記憶層は、抵抗変化層とイオン源層とにより構成されている。イオン源層は可動イオンとなる元素を含み、上部電極および下部電極に電圧を印加すると、記憶層の抵抗値が変化して情報を記憶する。抵抗変化層はフッ化マグネシウムなどのフッ化物を含有する。または、下部電極がフッ素またはリンを含有する。これにより、抵抗変化層は電圧印加の影響を受けにくく、抵抗変化層の劣化に起因するメモリ特性の低下が抑制される。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

記憶素子および記憶装置

【課題】消去状態における記憶素子の抵抗値が安定化された記憶素子および記憶装置を提供する。

【解決手段】下部電極10、記憶層20および上部電極30をこの順に積層した記憶素子1において、記憶層20は抵抗変化層22と可動原子を含むイオン源層21とを有する。抵抗変化層22は、n型ドーパントまたはp型ドーパントが導入されている。これにより、消去状態の不安定化の一因である抵抗変化層22内部に形成される局在サイトが不活性化され、抵抗変化層22の抵抗値が安定化する。

(もっと読む)

ストリング選択線及びビット線の改善されたコンタクトレイアウトを有する3次元メモリアレイ

【課題】インターコネクト及びコンタクト用の実装面積が小さい3次元集積回路メモリ用の構造を低製造コストで提供する。

【解決手段】3次元メモリデバイスは、絶縁材料21,22,23,24で分離され、復号化回路を介してセンスアンプに結合可能なビット線BLnとして導電材料の複数の帯片の形状をしている。導電材料帯片11,12,13,14は、スタック横面に側面を有する。ワード線WLn,WLn+1の複数の導電線16,17は行デコーダに結合でき、複数のスタック上で直交して延びる。導電線は、スタックの表面に共形である。記憶素子は、スタック上の半導体材料帯片の側面と導電線の間の交点の界面領域の多層アレイに設けられる。3次元メモリは、複数層に対する2つの最小線幅のマスクで作られる。半導体材料帯片の端部に階段構造が含まれる。半導体材料帯片に平行な金属層上と、ワード線に平行な上部金属層上にSSLインターコネクトを含む。

(もっと読む)

相変化メモリコーディング

【課題】取り付け工程に係る半田付け及び高温環境での熱事象を通じても、データを保持することができる相変化メモリデバイスの提供。

【解決手段】一部のセルとメモリに第一抵抗状態、及び他部のセルとメモリに第二抵抗状態を誘導することにより、データセットを表わすために、プレコーディング(pre−coded)することができる。前記データセットがコーディングされ、基板に取り付けられた後に、前記第一及び前記第二抵抗状態を感知することにより、前記データセットを読み取り、前記第一抵抗状態を第三抵抗状態に変化させ、前記第二抵抗状態を第四抵抗状態に変化させる。半田接合と他の熱サイクルプロセスの後、前記第一及び前記第二抵抗状態は、感知マージン(sensing margin)を維持する。より高速とより低い電力を使用すると、前記第三及び前記第四抵抗状態は、転移(transition)を引き起こす能力がある。

(もっと読む)

半導体装置及びその製造方法

【課題】追加のマスクや追加のプロセスを必要とせず、トランジスタを含む半導体装置に搭載することが可能なメモリ素子を実現する。

【解決手段】半導体装置を、絶縁膜17と金属膜又は金属化合物膜19とを積層した構造を有するメモリ素子16と、メモリ素子16と同一の積層構造を有するゲート構造を持つトランジスタとを備えるものとする。

(もっと読む)

記憶装置の製造方法

【課題】記憶層を分断加工する際に記憶層の表面酸化を抑えることが可能な記憶装置の製造方法を提供する。

【解決手段】下部電極11が形成された基板2上に、記憶層材料膜13Aと上部電極材料膜12Aとを順に形成する。上部電極材料膜12の上にフォトレジスト膜31を形成する。フォトレジスト膜31をマスクとしたドライエッチングを行うことにより、上部電極材料膜12Aおよび記憶層材料膜13Aをこの順にエッチングし、上部電極12および記憶層13をライン状(線状)に形成する。誘導結合型プラズマまたは磁気中性線放電プラズマを用い、ドライプロセスでフォトレジスト膜31を剥離する。記録層材料膜13Aまたは記憶層13がウェットエッチング用の薬液に触れることがなくなり、記憶層13の表面酸化が抑えられる。

(もっと読む)

記憶素子及び記憶装置

【課題】情報の記録等の動作を安定して行うことができ、熱に対しても安定した構成の記憶素子を提供する。

【解決手段】第1の電極2と第2の電極6との間に、記憶層4及びイオン源層3が挟まれて構成され、イオン源層3に、Cu,Ag,Znから選ばれるいずれかの金属元素と、Te,S,Seから選ばれるいずれかの元素とが含まれ、記憶層4が、タンタル酸化物、ニオブ酸化物、アルミニウム酸化物、ハフニウム酸化物、ジルコニウム酸化物のいずれか、或いはそれらの混合材料から成り、第1の電極2及び第2の電極6に、イオン源層3側の電極が正、記憶層4側の電極が負になるように電圧を印加すると、記憶層4にイオン化した金属元素が移動して電流パスを形成し、記憶層4の抵抗値が低くなる記憶素子10を構成する。

(もっと読む)

半導体装置

【課題】製造時以外にデータの書き込みが可能であり、書き換えによる偽造を防止可能な半導体装置を提供することを目的とする。さらに、本発明は、単純な構造の有機メモリから構成される安価な半導体装置の提供を課題とする。

【解決手段】有機化合物層を有する有機素子にトランジスタを並列または直列に接続したメモリセルを構成し、そのメモリセルを直列または並列に接続することによって、NAND型メモリまたはNOR型メモリを構成する。

前記有機素子は電流または電圧の印加、光の照射などで不可逆的にその電気特性を変化さ

せることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】相変化メモリの書き換え電流を低減する技術を提供する。

【解決手段】相変化メモリのメモリセルは、1個のダイオード素子とその上部に形成された4個の抵抗性記憶素子とからなる。1個の抵抗性記憶素子がダイオード素子と接触する領域AR3020Cは、ダイオード素子の平面パターンAR401に完全に含まれる。2個の抵抗性記憶素子がダイオード素子と接触する領域AR3021C、AR3022Cは、それぞれF(最小加工寸法)より小さいF1だけ削られており、上記接触領域AR3020Cよりも小さい。残り1個の抵抗性記憶素子がダイオード素子と接触する領域AR3023Cは、互いに直交する両方向においてF1だけ削られており、ダイオード素子の平面パターンAR401に僅かに含まれる。

(もっと読む)

1 - 20 / 100

[ Back to top ]