Fターム[5F083EP02]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 電荷蓄積機構 (5,261) | FGを有するもの (3,098)

Fターム[5F083EP02]の下位に属するFターム

Fターム[5F083EP02]に分類される特許

2,141 - 2,151 / 2,151

電荷損失が減少された窒化物層を備えるメモリセル構造及びその製造方法

本発明の一実施形態に従って、半導体基板(210)、半導体基板上に配置された第1シリコン酸化物層(215)、第1シリコン酸化物層上に配置された電荷格納層(220)、電荷格納層上に配置された第2シリコン酸化物層(225)、及び第2シリコン酸化物層上に配置されたゲート層(230)がメモリセル構造に含まれる。例示的な実施形態では、例えば、水素含有量が約0at%〜約0.5at%の範囲に減少されたシリコン窒化物が電荷格納層(220)に含まれる。電荷格納層(220)における水素含有量が減少されることで、結果として電荷損失が減少される。電荷損失が減少された電荷格納層(220)が、メモリデバイスにおける閾電圧シフト、プログラミングデータ損失及びプログラミング性能損失を減少する利点を有し、その結果メモリデバイスパフォーマンスを改善する。  (もっと読む)

(もっと読む)

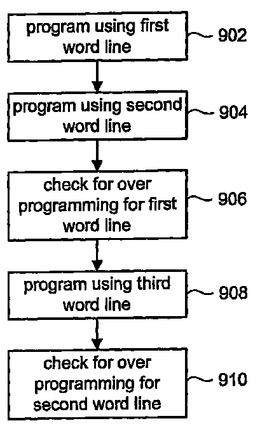

隣接するメモリセルのプログラミングの後にオーバー・プログラミングされたメモリセルを検出する技術

非揮発性半導体メモリシステム(又は他のタイプのメモリシステム)において、メモリセルは、その閾電圧を変更することによってプログラミングされる。システム内の様々なメモリセルに対するプログラミングのタイミングが異なることが原因で、いくつかのメモリセルは、オーバー・プログラミングされてしまう可能性がある。即ち、例えば、セルの閾電圧が、目的とされた値、又は、目的とされた範囲から外れてしまう可能性がある。本発明は、セルに対するプログラミングが原因で、それに隣接する行のメモリセルがオーバー・プログラミングされたか否かを判断することを含んでいる。

(もっと読む)

(もっと読む)

UVチャージングを減少するPECVDシリコンリッチ・シリコン酸化物層

メタライゼーションの前に、UV透過を低減するシリコンリッチ・シリコン酸化物層(500)をPECVDにより層間絶縁膜(300)上にたい積する。これによりVtが減少する。実施形態は、1.7から2.0のR.I.を有するUVを透過しないシリコンリッチ・シリコン酸化物層(500)をたい積するステップを含んでいる。  (もっと読む)

(もっと読む)

電気試験データに基づいてゲート絶縁層の特性および特徴を制御するための方法、これを実施するためのシステム

本発明は、一般に、電気試験データ(46)に基づいてゲート絶縁層(16)の特性および特徴を制御する各種方法、ならびにこれを実施するためのシステムを対象としている。例示的な一実施形態では、上記方法は、少なくとも1つの半導体デバイスに少なくとも1つの電気試験を実施するステップと、以降形成する半導体デバイスに少なくとも1つのゲート絶縁層(16)を形成するために実施する少なくとも1つのプロセス操作の少なくとも1つのパラメータを、電気試験から得られた電気データに基づいて決定するステップと、決定されたパラメータを含む少なくとも1つのプロセス操作を実施して、ゲート絶縁層(16)を形成するステップとを有する。  (もっと読む)

(もっと読む)

不揮発性メモリのソース制御操作

フラッシュEEPROMなどの不揮発性メモリが、自己限定プログラミング技術を用いて並列にプログラムされ得るメモリセルを有する。個々のセルは、自己限定的に熱い電子で荷電され得る電荷記憶装置を有する。電荷記憶装置が必要なレベルの電荷に達すると、熱い電子はそれ以上生成されないか、或いは少数しか生成されない。熱い電子の生成が停止する電荷レベルは、セルに印加される電圧によって決まる。このように、複数のセルが並列にプログラムされ、印加電圧に対応する電荷レベルで各々のセルが自己限定される。  (もっと読む)

(もっと読む)

素子間分離のための半導体構造中の素子間のボイドの使用

記憶素子間の静電結合レベルを低減するために、隣接する電荷記憶素子を有するフラッシュEEPROMまたは他のタイプのメモリセルアレイを素子間にガスが充填されているボイドとともに形成し、これにより電荷記憶素子間の漏れ結合およびアレイから読み出されるデータ中に結果として生じるエラーを低減する。  (もっと読む)

(もっと読む)

フラッシュメモリデバイスの特性を改善する方法

半導体デバイスを製造する方法において、シリコン基板(62)上にゲート酸化膜(60)を提供する。このゲート酸化膜(60)上に第1ポリシリコン層(64)を提供し、第1ポリシリコン層(64)上に絶縁層(66)を提供し、またこの絶縁層(66)上に第2ポリシリコン層(68)を提供する。適切なマスキングを実行した後にエッチングステップが実行されると、シリコン基板を露出させ、かつこのシリコン基板上にスタックゲート構造を形成すべく、第2ポリシリコン層、絶縁層、第1ポリシリコン層、およびゲート酸化膜の一部を除去するようにこれらの層がエッチングされる。スタックゲート構造(72)上に薄い酸化膜(80)を成長させるべく、短時間(例えば10秒から20秒)の急速熱アニールを実行する。それから、急速熱アニールによって形成された酸化膜(80)上に第2酸化膜(82)をたい積する。

(もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】下層のポリシリコン膜を酸化させることなく、酸素アニールによりHTO膜を十分に改質させ、電気的にリークが少ないトンネル酸化膜を形成する半導体装置の製造方法を提供すること。

【解決手段】ポリシリコン膜からなる第1フローティングゲート16上に、窒化膜26又は酸窒化膜28を介してHTO膜を成膜し、酸素アニール処理を施して、トンネル酸化膜18(HTO膜)を形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】 メモリセルの書込み特性のばらつきに起因する書込みベリファイ回数の増加を抑制し、書込み時間の短縮をはかり得るEEPROMを提供すること。

【解決手段】 Si基板1上に浮遊ゲート4と制御ゲート6を積層し、電気的書替え可能としたメモリセルが2次元配置されたメモリセルアレイと、基板1とゲート6の間に消去パルスを印加する消去機構と、基板1とゲート6の間に消去パルスと逆極性の低い電圧の事前書込みパルスを印加する事前書込み機構と、事前書込みパルス印加後の状態を検知するしきい値ベリファイ機構と、基板1とゲート6の間に消去パルスと逆極性の高い電圧の書込みパルスを印加する書込み機構とを備えたEEPROMであって、消去動作の後、事前書込み動作としきい値ベリファイ動作を、最も速く変動するメモリセルのしきい値が消去状態の所望の値に達するまで繰返し、次いで書込み動作によってデータ書込みを行うことを特徴とする。

(もっと読む)

半導体記憶装置

【課題】 ゲート絶縁膜の劣化を防止すると共に、浮遊ゲート内のキャリアの電荷量を正確に制御できるようにする。さらに、書き込み時の消費電力を不要にする。

【解決手段】 開示されている半導体記憶装置は、浮遊ゲート6に一部分が接すると共に他部分がP型シリコン基板1に接するようにモット絶縁体7を設け、このモット絶縁体7に金属−絶縁相転移を生じさせる。そして、浮遊ゲート6に対してキャリアである電子の注入又は放出を行う場合、ゲート酸化膜5を通じてではなく、モット絶縁体7の金属相を通じてキャリアの注入又は放出を行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】NANDセル型EEPROMのデータ消去後に、ビット線コンタクト部とセルPウエルとの接合の順方向電流によるラッチアップを防止する。

【解決手段】NANDセル型EEPROMにおいて、浮遊ゲートおよび制御ゲートを有する不揮発性のメモリセルを少なくとも1つ含むメモリセルユニットと、メモリセルユニットが形成されるメモリセルウエルCPWELL、CNWELLと、メモリセルユニットの一端に接続された第1の信号線BLi と、メモリセルユニットの他端に接続された第2の信号線CELSRCと、メモリセルの記憶データを消去する際、メモリセルウエルに消去電圧を所定期間印加して消去動作を行わせた後、第1の信号線および第2の信号線をフローティング状態にして、メモリセルウエルの消去電圧を放電させるように制御する制御回路を具備する。

(もっと読む)

2,141 - 2,151 / 2,151

[ Back to top ]