Fターム[5F083EP02]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 電荷蓄積機構 (5,261) | FGを有するもの (3,098)

Fターム[5F083EP02]の下位に属するFターム

Fターム[5F083EP02]に分類される特許

2,001 - 2,020 / 2,151

放射線線量計

個人X線線量計システムは携帯用検出器(100)及び読み取り装置(114)を有する。携帯用検出器(100)は、プログラムされた不揮発性メモリ素子(102)のアレイ(104)と、入射X線の一部をUV放射線に変換するシンチレータ素子(106)とを有する。UV放射線に変換されていないX線(112)に曝される結果、メモリ素子(102)の一部は各々の浮遊ゲートに電荷を有することになり、それにより、対応する閾値(Vt)変化が生じさせられる。ある被爆時間後、読み取り装置(114)が、Vt変化されたメモリ素子(102)の数を表すデータを検出器(100)から読み出し、所定の較正曲線を用いて、ユーザが被曝した放射線量(122)を上記データから決定する。

(もっと読む)

(もっと読む)

半導体集積回路装置およびその製造方法

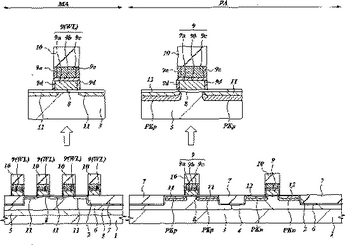

ポリメタルゲートを構成する高融点金属膜の洗浄工程における欠けを防止し、装置の特性を向上させ、また、洗浄効率を向上させるため、基板1上の低抵抗多結晶シリコン膜9a、WN膜9bおよびW膜9cを、窒化シリコン膜10をマスクにドライエッチングし、これらの膜よりなるゲート電極9を形成し、ウエットハイドロゲン酸化により薄い酸化膜9dを形成した後、RPN法を用いて窒化処理を行い、ゲート電極の側壁から露出したW膜9cをWN膜9eとする。その結果、その後の洗浄工程、例えば、n−型半導体領域11やp−型半導体領域12の形成時に行われる、1)レジスト膜のホトリソグラフィー工程、2)不純物の注入工程、3)レジスト膜の除去工程および4)基板表面の洗浄工程が繰り返し行われても、W膜9cの欠けを防止でき、また、洗浄液としてU洗浄液やフッ酸系の洗浄液のような強い洗浄液を用いることができる。  (もっと読む)

(もっと読む)

高いカップリング比を持つ自己整列型トレンチ充填方法

高密度集積回路内で活性領域を分離するための自己整列型トレンチ充填方法を提供する。基板内の、活性領域同士の間に深く狭いトレンチがエッチングされる。トレンチは、その内部で二酸化シリコンなどの適切な誘電体を成長させることで充填される。酸化物が基板から成長してトレンチを充填し、基板内に浸透することで、トレンチよりも幅広く深い酸化物が得られる。NAND型フラッシュメモリシステムのための記憶素子は、例えば、NANDストリング活性範囲を形成するべくエッチングを行った後、あるいはエッチングの一部として実行されるので、基板をエッチングしてトレンチを形成することで製造することができる。これにより、NANDストリング活性範囲が分離トレンチ同士の間に確実に整列させることができる。誘電体成長工程は自己規制型であるため、エッチング工程によって出来たオープン範囲を活性範囲同士の間に維持することができる。次に形成されるゲート内誘電層と制御ゲート層により、オープン範囲が充填されて、制御ゲートと浮遊ゲートの間に側壁結合が得られる。 (もっと読む)

半導体記憶装置

【課題】消去セルの閾値電圧の変化を抑制することが困難であった。

【解決手段】メモリセルアレイ1は、第1、第2乃至第nの状態からなるn値(nは2以上の自然数)を記憶する複数のメモリセルがマトリックス状に配置されている。制御回路7は、メモリセルアレイ1のj値(j<n)のデータが記憶されている第1メモリセルに、次の少なくとも1値のデータを記憶する前に、第1メモリセルに隣接する少なくとも1つの第2メモリセルが第1の状態であり、第1の閾値電圧に達していない場合、第1の閾値電圧まで書き込み動作を行なう。

(もっと読む)

半導体記憶装置、半導体記憶装置の製造方法および半導体記憶装置の動作方法

【課題】 製造が容易でかつ微細化が容易な半導体記憶装置を提供すること。

【解決手段】 この半導体記憶装置では、上記ソース・ドレイン領域104、105は、上記フローティングゲート110、111の一部とオーバーラップしており、上記フローティングゲート110、111の側面は、上記コンタクトプラグ113、114に略沿った形状であり、上記コンタクトプラグ113、114は、上記フローティングゲート110、111の近傍にあるので、デバイス面積を増大させることなく、メモリデバイスの書き込みおよび消去の速度を高速化させることができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】チップ面積を殆ど増加させることなく、読出し動作の高速化をはかる。

【解決手段】不揮発性メモリ素子からなるNANDセルの複数個をソース線を共有するように配設してブロックを構成し、該ブロックの複数個を一端側でビット線を共有し他端側でソース線を共有するように配設してなるメモリセルアレイと、メモリセルアレイのビット線を選択するカラムデコーダと、メモリセルのワード線選択及び選択トランジスタのゲート線選択を行うロウデコーダとを備えたEEPROMであって、各ブロック間で隣接するソース線側選択トランジスタのゲート線SG2は、共通接続されると共にロウ・デコーダで駆動される配線に同一のコンタクトにより接続され、ロウデコーダは、ブロック間で隣接するソース線側選択トランジスタのゲート線SG2を一組にして選択する。

(もっと読む)

半導体装置とその製造方法

【課題】 歩留まりが向上して信頼性の高いフラッシュメモリセルを備えた半導体装置とその製造方法を提供すること。

【解決手段】 第1窓70aを有する第1レジストパターン70を第2絶縁膜69上に形成する工程と、第1レジストパターン70をエッチングマスクにしてコンタクト領域CRが露出する第1開口69dを形成する工程と、第1レジスト部76aを有する第2レジストパターン76を第2導電膜74上に形成する工程と、第2レジストパターン76をエッチングマスクにし、第1、第2導電体67a、74a、フローティングゲート67d、及びコントロールゲート74dを形成する工程と、第3レジストパターン80を各領域I、IIに形成する工程と、第3レジストパターン80をエッチングマスクにして第2窓80a下の第2導電体74aを除去する工程と、を有する半導体装置の製造方法による。

(もっと読む)

半導体記憶装置

【課題】 不純物拡散領域に注入された不純物がトンネル酸化膜(第1のゲート絶縁膜)近傍まで拡散するのを防ぐことができる半導体記憶装置を得る。

【解決手段】 半導体基板と、半導体基板上に第1のゲート絶縁膜を介して形成されたフローティングゲートと、フローティングゲート上に第2のゲート絶縁膜を介して形成されたコントロールゲートと、半導体基板の表面に形成された不純物拡散領域とを有し、不純物拡散領域の上面を、第1のゲート絶縁膜と半導体基板の界面よりも40nm以上低くしている。

(もっと読む)

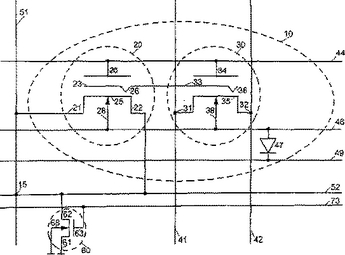

フィールドプログラマブルゲートアレイを構成するためのプログラム可能な相互接続セル

本発明は、制御ゲート電位のノードと、ドレイン、ソース、フローティングゲート、前記制御ゲート電位のノードに接続された制御ゲートを有する第1のフローティングゲートフラッシュメモリトランジスタと、第1のプログラム可能なノードに接続されると共に、第2のプログラム可能なノードに接続されたドレイン、第1のフローティングゲートフラッシュメモリトランジスタのフローティングゲートに接続されたフローティングゲート、制御ゲート電位のノードに接続された制御ゲートを有する第2のフローティングゲートフラッシュメモリトランジスタとを有するプログラム可能な相互接続セル切り替え回路構造を備え、それによって、第1のフローティングゲートフラッシュメモリトランジスタのソースまたはドレインが、プログラム動作の間、セルの外でアースに接続されることを必要とする。  (もっと読む)

(もっと読む)

プラズマ処理方法,半導体基板及びプラズマ処理装置

本発明は,半導体基板の表面に対してマイクロ波を利用したプラズマにより,プラズマ酸化処理とプラズマ窒化処理とを同時に行い,さらに必要に応じて,上述のようなプラズマ酸窒化処理による絶縁膜形成の後,当該絶縁膜に対してさらにプラズマ窒化処理を行う。これによって,電気的特性が良好な絶縁膜(シリコン酸化膜)を形成することができる。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置

【課題】消費電力を低減できる不揮発性半導体記憶装置を提供すること。

【解決手段】不揮発性半導体記憶装置は、メモリセルアレイ10のカラムをリダンダンシビット線に置き換えることで不良を救済する不揮発性半導体記憶装置であって、前記メモリセルアレイ10のロウ方向を選択するロウアドレス信号の変化を検知するロウアドレス変化検知回路91を具備し、前記ロウアドレス変化検知回路91によって前記ロウアドレス信号の変化が検知された際にのみ、前記リダンダンシビット線がセンスされる。

(もっと読む)

半導体装置

【課題】

高電圧を必要とするメモリ素子を混載し、かつメモリ素子駆動回路の製造工程を簡単化でき、かつメモリ素子駆動回路の占有面積の増大を抑制することのできる半導体装置を提供する。

【解決手段】

半導体装置は、第1の電圧で動作する複数のMOSトランジスタを含む主回路と、前記第1の電圧より高い第2の電圧での操作を必要とするメモリ素子と、前記メモリ素子を駆動する駆動回路であって、1つのウェルと、前記1つのウェル内に形成され、カスケード接続された2つ以上のMOSトランジスタと、前記ウェル内の各MOSトランジスタの間およびカスケード接続の両外側、または各MOSトランジスタの間のみ、またはカスケード接続の両外側のみ、またはカスケード接続されたMOSトランジスタのドレイン外側のみに形成されたウェルコンタクトとを有する駆動回路と、を有する。

(もっと読む)

半導体装置およびその製造方法、フォトマスク

【課題】 パターンの埋め込み不良の発生が抑制された半導体装置およびその製造方法ならびにフォトマスクを提供する。

【解決手段】 半導体装置の露光工程において用いられるフォトマスク200は、その主表面上に形成された光を遮る残しパターン22(遮光パターン)と、主表面上に形成された光を透過させる抜きパターン23(透光パターン)とを備え、抜きパターン23は、その延在方向の終端部230におけるパターン幅が、中央部側に位置する部分におけるパターン幅よりも広くなるように形成されている。

(もっと読む)

不揮発性メモリ回路

【課題】電源電圧を印加しなくてもデータを記憶できる不揮発性メモリ回路及び不揮発性メモリ装置に関し、書き込み・読み出しを最適に行なえる不揮発性メモリ回路及び不揮発性メモリ装置を提供することを目的とする。

【解決手段】本発明は、不揮発性メモリ回路であって、第1又は第2のビット線に印加される電圧により不可逆的に内部回路を劣化させてデータを不揮発的にラッチするフリップフロップと、フリップフロップの第1の出力端子と前記第1のビット線との間に接続された第1スイッチと、フリップフロップの第1の出力端子と第1のビット線との間に接続された第2スイッチと、フリップフロップの第1の出力端子の出力を反転した出力を行なう第2の出力端子と第2のビット線との間に接続された第3スイッチと、フリップフロップの第2の出力端子と第2のビット線との間に接続された第4スイッチとを有することを特徴とする。

(もっと読む)

半導体装置とその製造方法

【課題】 周辺回路領域に形成されるロジック回路等に不具合が発生するのを防ぐことができるフラッシュメモリセルを備えた半導体装置とその製造方法を提供すること。

【解決手段】 第1導電体25aのコンタクト領域CR上の第2絶縁膜26を除去する工程と、第2絶縁膜26の上に第2導電膜30を形成する工程と、第1導電体25aのコンタクト領域CR上の第2導電膜30を除去し、該第2導電膜30を第2導電体30aとする工程と、第2導電体30aを覆う層間絶縁膜(第3絶縁膜)44を形成する工程と、コンタクト領域CR上の層間絶縁膜44に第1ホール44aを形成する工程と、コンタクト領域CRと電気的に接続される導電性プラグ45aを第1ホール44a内に形成する工程と、を有することを特徴とする半導体装置の製造方法による。

(もっと読む)

フラッシュメモリをROMメモリへ変換する方法、およびその変換されたROMメモリを具えるデバイス

第1の半導体デバイス上のフラッシュメモリセルを、第2の半導体デバイス上のROMメモリセルに変換する方法であって、第1および第2の半導体デバイスのそれぞれは、半導体基板上に配置されて、同一のデバイス部、並びに、当該デバイス部をフラッシュメモリセルおよびROMメモリセルにそれぞれ配線するための、同一の書込みスキームをそれぞれ具え、フラッシュメモリセルは、少なくとも1つの不揮発性技術のマスクを用いて、不揮発性メモリ技術において製造され、さらに、アクセストランジスタ、並びに、浮遊ゲートおよび制御ゲートを含む浮遊トランジスタを具え、ROMメモリセルは、少なくとも1つのベースラインマスクを用いて、ベースライン技術において製造され、単一のゲートトランジスタを具え、少なくとも1つのベースラインマスクのレイアウトを操作するステップを含み、当該操作ステップは、フラッシュメモリセルのレイアウトを、少なくとも1つのベースラインマスクのレイアウトに組み込むステップと、少なくとも1つのベースラインマスクから、フラッシュメモリセルのレイアウトからの浮遊トランジスタのレイアウトを除去し、さらに、フラッシュメモリセルのアクセストランジスタのレイアウトを、ROMメモリセルのシングルゲートトランジスタのレイアウトとして設計することによって、少なくとも1つのベースラインマスクにおけるフラッシュメモリセルのレイアウトを、ROMメモリセルのレイアウトに変換するステップとを含む変換方法。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置

【課題】 微細化に有利な、二重ウェル、及びこの二重ウェルから離れたウェルを備えた不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1導電型の半導体基板1内に形成された第1導電型の第1ウェル10と、第1ウェル10に形成された複数のメモリセルトランジスタQ5−1、Q5−2と、第1ウェル10の側面領域を囲む第1部分7、及び第1ウェル10の下部領域を囲む第2部分9を有し、第1ウェル10を半導体基板1から電気的に分離する第2導電型の第2ウェルと、半導体基板1内に形成された第2導電型の第3ウェル領域5と、を備える。そして、第3ウェル5の深さL1を、第2ウェルの第2部分9の深さL2よりも浅くする。

(もっと読む)

不揮発性半導体記憶装置

【課題】 信頼性を確保しつつ、書込み速度を確保することができる不揮発性半導体記憶装置を提供する。

【解決手段】 半導体基板40と、半導体基板上40に形成された絶縁膜39と、半導体基板40上に形成された複数のメモリセルと、絶縁膜40上に形成され、メモリセルに向けて延在する複数の第1アシストゲートと、第1アシストゲートの端部を接続し、絶縁膜上に形成された接続部7と、接続部よりメモリセル側に配置され、メモリセルに向けて延在する第2アシストゲート11と、第1アシストゲート下の領域に電圧を印加するか否かを制御する第1選択トランジスタと、第2アシストゲート11下の領域に電圧を印加するか否かを制御する第2選択トランジスタ10dと、第2アシストゲート11と第2選択トランジスタ10dとの間に形成された不純物領域とを備え、接続部7と不純物領域との交差領域下に形成された絶縁膜39を、第1アシストゲート下および第2アシストゲート11下に形成された絶縁膜39より厚くした。

(もっと読む)

フラッシュメモリ素子のソースコンタクト形成方法

【課題】 金属配線およびコンタクト抵抗に優れると同時に、後続の熱処理工程が行われても素子特性の低下を防止することを可能とするフラッシュメモリ素子のソースコンタクト形成方法を提供する。

【解決手段】 本発明のフラッシュメモリ素子のソースコンタクト形成方法は、セル領域のSSL用ゲート電極パターンに備えられた接合領域が形成された半導体基板の全面に層間絶縁膜を形成し、前記層間絶縁膜をパターニングし、前記SSL用ゲート電極パターンの一側で前記接合領域を露出させるソースコンタクトホールを形成する段階と、前記ソースコンタクトホールの形成された結果物の全面にタングステンシリサイド膜の含まれた膜を形成し、前記層間絶縁膜が露出するまで平坦化工程を行い、前記ソースコンタクトホール内にのみ前記タングステンシリサイド膜の含まれた膜が埋め立てられてソースコンタクトを形成する段階とを含む。

(もっと読む)

成膜方法及び成膜装置並びに記憶媒体

【課題】 ポリシリコン膜を形成する際、ポリシリコン膜のグレインサイズを任意の大きさに制御すること。また反応容器内にてウエハを棚状に保持させて処理を行う成膜装置にて、面間均一性及び面内均一性を高めること。

【解決手段】 多数枚のウエハWをウエハボート25に保持させて、反応容器2内に搬入し、成膜ガスを供給して所定の成膜処理を行うにあたり、先ず反応容器内に成膜ガスを供給し、前記ウエハW上に第1のポリシリコン膜を形成し、次いで前記成膜ガスの供給を停止し、反応容器内を真空排気して前記成膜ガスを除去する。続いて酸素ガスを供給して、前記第1のポリシリコン膜の表面を酸素に接触させ、次に前記酸素ガスの供給を停止し、反応容器内を真空排気して前記酸素ガスを除去し、しかる後反応容器内に前記成膜ガスを供給し、前記第1のポリシリコンの上に第2のポリシリコン膜を形成する。

(もっと読む)

2,001 - 2,020 / 2,151

[ Back to top ]