Fターム[5F083EP04]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 電荷蓄積機構 (5,261) | FGを有するもの (3,098) | 構造 (540) | 多層構造 (154)

Fターム[5F083EP04]の下位に属するFターム

長さの異なる層からなるもの (58)

Fターム[5F083EP04]に分類される特許

1 - 20 / 96

不揮発性半導体記憶装置及びその製造方法

【課題】 書き込み動作及び消去動作の両方の特性向上を図る。

【解決手段】 実施形態による不揮発性半導体記憶装置は、半導体基板11と、半導体基板上に形成されたゲート絶縁膜12と、ゲート絶縁膜上に形成され、13族元素であるP型不純物を含有するポリシリコンからなり、下部膜13aと下部膜上に積層された上部膜13bとを有するフローティングゲート電極13と、フローティングゲート電極上に形成された電極間絶縁膜16と、電極間絶縁膜上に形成されたコントロールゲート電極17と、を具備し、上部膜におけるP型不純物の濃度又は活性化濃度は、下部膜におけるP型不純物の濃度又は活性化濃度より高い。

(もっと読む)

二重層フローティングゲートを備えているEPROMセル

【課題】インクジェットペンコントロールチップの既存の層を利用して製造できるEPROMを提供する。

【解決手段】EPROMセル70は、ソース領域及びドレイン領域を有する半導体基板52と、第1の金属層60と電気的に相互接続されている半導体ポリシリコン層56を含むフローティングゲート72と、第2の金属層64を含むコントロールゲートとを備えている。フローティングゲート72は、ソース領域及びドレイン領域に隣接して配置され、第1の誘電体層54によって半導体基板52から分離され、コントロールゲートの第2の金属層64は、第1の金属層60との間にある第2の誘電体層62を介して、第1の金属層60と容量結合されている。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

半導体素子及びその製造方法

【課題】干渉現象を減らしてゲートラインの抵抗を減らすことができる半導体素子の製造方法を提供する。

【解決手段】最上部層が金属シリサイド層からなり、第1間隔で半導体基板上に配列される第1ゲートラインと、最上部層が金属シリサイド層からなり、前記第1間隔より広い第2間隔で前記半導体基板上に配列される第2ゲートラインと、前記第1ゲートラインの間の前記半導体基板上に形成されてエアギャップを含む第1絶縁膜と、前記第2ゲートラインの対向する側壁上に形成された第2絶縁膜と、前記第2絶縁膜の側壁に形成されたエッチング停止膜と、前記第1ゲートラインの間の空間と前記第2ゲートラインとの間の空間が満たされるように全体構造上に形成された第3絶縁膜と、前記第3絶縁膜の上部に形成されたキャッピング膜と、前記キャッピング膜及び前記第3絶縁膜を貫通して前記第2ゲートラインの間の前記半導体基板に形成された接合領域と繋がれるコンタクトプラグと、を含む。

(もっと読む)

NAND型不揮発性メモリのデータ消去方法

【課題】NAND型不揮発性メモリを提供する。

【解決手段】ビット線と、ソース線と、複数の不揮発性メモリが直列に接続されたNAND型セルと、選択トランジスタと、を有し、不揮発性メモリは、第1の絶縁膜を介した半導体上の電荷蓄積層と、第2の絶縁膜を介した電荷蓄積層上の制御ゲートと、を有し、NAND型セルの一方の端子は、選択トランジスタを介して、ビット線に接続され、NAND型セルの他方の端子は、ソース線に接続されたNAND型不揮発性メモリであって、第1の絶縁膜は、半導体に酸素雰囲気で高密度プラズマ処理を行った後、窒素雰囲気で高密度プラズマ処理を行うことで形成されるNAND型不揮発性メモリ。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】浮遊ゲート電極の細りを補償して信頼性を向上させた不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置10では、第1の幅W1を有する活性領域12が、半導体基板11の主面に形成された素子分離層13で分離されている。第1ゲート絶縁膜14が、活性領域12に形成されている。第1の幅W1より狭い第2の幅W2を有する第1導電層15aが、第1ゲート絶縁膜14を介して活性領域12に形成されている。第1の幅W1と第2の幅W2の差を補償するように第3の幅W3を有する第2導電層15aが第1導電層15aの側壁に形成されている。第1ゲート電極15は、第1導電層15aと第2導電層15bを含んでいる。第2ゲート絶縁膜16が、第1ゲート電極15および素子分離層13上にコンフォーマルに形成されている。第2ゲート電極17が、第2ゲート絶縁膜16上に形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込みを高速化した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置110は、ベース半導体層10aと、電極70aと、チャネル半導体層30aと、ベーストンネル絶縁膜20aと、チャネルトンネル絶縁膜40aと、電荷保持層50aと、ブロック絶縁膜60aと、を有するメモリ部MC1を備える。チャネル半導体層30aは、ベース半導体層10aと電極70aとの間に設けられ、電極70aに対向するチャネル部31aを含む。ベーストンネル絶縁膜20aは、ベース半導体層10aとチャネル半導体層30aとの間に設けられる。チャネルトンネル絶縁膜40aは、電極70aとチャネル部31aとの間に設けられる。電荷保持層50aは、電極70aとチャネルトンネル絶縁膜40aとの間に設けられ、電荷を保持する。ブロック絶縁膜60aは、電極70aと電荷保持層50aとの間に設けられる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】隣接セルとの容量を抑制することが可能な半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態の半導体記憶装置は、第1の方向および前記第1の方向と直交する第2の方向に配置される複数のメモリセルトランジスタを備える。前記メモリセルトランジスタのそれぞれは、半導体基板上に形成される第1の絶縁膜と、前記第1の絶縁膜上に形成される浮遊ゲート電極と、前記浮遊ゲート電極上に形成される第2の絶縁膜と、前記第2の絶縁膜上に形成される制御ゲート電極と、を有する。前記第1および第2の方向に隣接する2つの前記メモリセルトランジスタの前記浮遊ゲート電極は、前記隣接する方向の側面に括れた領域を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】周辺回路の抵抗素子の抵抗部の厚さに依らずにメモリセルトランジスタの浮遊ゲートの厚さを自由に設定することのできる半導体装置、およびその製造方法を提供すること。

【解決手段】基板上の抵抗素子およびスタックド・ゲート型のメモリセルトランジスタを含む半導体装置を提供する。前記抵抗素子は、抵抗として機能しない非導通層、および前記非導通層上に第1の絶縁膜を介して形成された抵抗として機能する導通層を含む。前記メモリセルトランジスタは、第1の浮遊ゲートを含む浮遊ゲートを有する。前記非導通層と前記第1の浮遊ゲートは、同じ材料からなる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】素子分離絶縁膜の埋め込み後の化学機械研磨法による研磨で、浮遊ゲート電極をストッパ膜として使用できるようにする。

【解決手段】シリコン基板1にゲート絶縁膜4、下層多結晶シリコン膜5a、上層多結晶シリコン膜5bを積層形成する。上層多結晶シリコン膜5bは、成膜時に炭素を1×1018atoms/cm3以上例えば2×1020〜2×1021atoms/cm3の範囲の濃度で添加される。素子分離溝1bを形成した後に、素子分離絶縁膜2を埋め込み、化学機械研磨法の研磨で素子分離溝1b内以外の部分を除去する。この時、上層多結晶シリコン膜5bがスクラッチの発生を抑制できるストッパ膜として利用でき、シリコン窒化膜などを不要とした構成とすることができる。

(もっと読む)

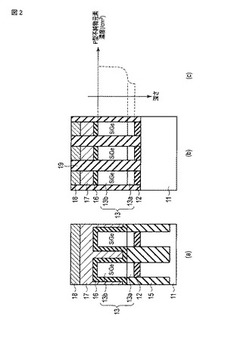

半導体記憶装置

【課題】隣接セルとの容量を低減し、カップリング比を向上させる。

【解決手段】半導体記憶装置は、半導体基板101と、前記半導体基板上に所定間隔を空けて設けられた複数の第1の絶縁膜103と、前記第1の絶縁膜間にビット線方向に沿って設けられた素子分離領域102と、前記第1の絶縁膜上に設けられた第1の電荷蓄積膜104a、前記第1の電荷蓄積膜上に設けられ、ワード線方向の幅が前記第1の電荷蓄積膜より狭い第2の電荷蓄積膜104b、及び前記第2の電荷蓄積膜上に設けられ、ワード線方向の幅が前記第2の電荷蓄積膜より広い第3の電荷蓄積膜104cを有する電荷蓄積層104と、前記第2の電荷蓄積膜と前記素子分離領域との間に設けられた第2の絶縁膜107と、前記電荷蓄積層上及び前記素子分離領域上に前記第2の方向に沿って設けられた第3の絶縁膜105と、前記第3の絶縁膜上に設けられた制御ゲート電極106と、を備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 メモリセルトランジスタの高密度化が可能な不揮発性半導体記憶装置及びその

製造方法を提供する。

【解決手段】 本発明では半導体基板1上のトンネル絶縁膜2と、トンネル絶縁膜上に形

成された第1の浮遊ゲート電極3a及び第1の浮遊ゲート電極上に形成され第1の浮遊ゲ

ート電極よりもチャネル幅方向の幅が短い第2の浮遊ゲート電極3bを有する浮遊ゲート

電極3と、第1の浮遊ゲート電極及びトンネル絶縁膜のチャネル幅方向の側面と接触して

第1の浮遊ゲート電極上面と同じ高さまで上面が突出しかつ下部が前記半導体基板に埋め

込まれた素子分離絶縁膜4と、浮遊ゲート電極の上面及びチャネル幅方向の側面並びに素

子分離絶縁膜の上面を連続して覆い浮遊ゲート電極との界面における窒素濃度が素子分離

絶縁膜との界面における窒素濃度より高い電極間絶縁膜5と、電極間絶縁膜上に形成され

た制御ゲート電極6とを有する不揮発性半導体記憶装置が得られる。

(もっと読む)

不揮発性半導体記憶装置

【課題】金属膜からなるFGを用いることで、書き込み特性及びリテンション特性を向上させた不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板上に形成された第1のゲート絶縁層、前記半導体基板上に前記第1のゲート絶縁層を介して形成された浮遊ゲート、前記浮遊ゲート上に形成された第2のゲート絶縁層、及び前記浮遊ゲート上に前記第2のゲート絶縁層を介して形成された制御ゲートを有するメモリセルを備え、前記浮遊ゲートは、前記第1のゲート絶縁膜と接する第1の半導体膜、及び前記半導体膜上に積層された金属膜とからなる。

(もっと読む)

フラッシュ・メモリ・デバイスおよびその製造方法

【課題】 制御ゲートと浮動ゲートとの間にジグザグ容量を含み、浮動ゲートおよびチャネルに対する制御ゲートの結合を増大するフラッシュ・メモリ・デバイスを提供する。

【解決手段】 フラッシュ・メモリ・デバイスは、ウェハと、このウェハの上に配置されたゲート酸化物層と、このゲート酸化物層、ウェハ、またはそれらの組み合わせの上に配置された浮動ゲートであって、平坦な浮動ゲート部およびこの平坦な浮動ゲート部の選択された領域の上に配置された概ね矩形の浮動ゲート部を含む浮動ゲートと、浮動ゲートの上に配置された高K誘電材料と、高K誘電材料の上に配置された制御ゲートとを含み、高K誘電材料が浮動ゲートを制御ゲートに結合するジグザグ・パターンを形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】 浮遊ゲート電極を含んでおり、メモリセルトランジスタの電気的特性劣化を防ぐことができる不揮発性半導体記憶装置を提供する。

【解決手段】 本発明では、半導体基板1上に形成されたトンネル絶縁膜と、トンネル絶縁膜上に形成された第1の浮遊ゲート電極と第1の浮遊ゲート電極上に形成された非縮退状態の半導体からなる第2の浮遊ゲート電極とを有する浮遊ゲート電極と、浮遊ゲート電極上に形成された電極間絶縁膜と、電極間絶縁膜上に形成された制御ゲート電極とを有する不揮発性半導体記憶装置が得られる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜に所望の大きさでバーズビークが形成され、ゲート絶縁膜の電気的特性に優れた半導体装置およびその製造方法、を提供する。

【解決手段】半導体装置の製造方法は、シリコン基板1上にトンネル酸化膜3およびポリシリコン膜4を形成する工程と、ポリシリコン膜4、トンネル酸化膜3およびシリコン基板1をエッチングしてトレンチ2m,2nを形成する工程と、サイドウォール41をトレンチ2m,2nの側面に形成する工程と、シリコン基板1をエッチングしてトレンチ42m,42nを形成する工程と、サイドウォール41が存在する状態で、トレンチ42m,42nの内壁、ならびにサイドウォール41と対向するトンネル酸化膜3の端部に隣接したポリシリコン膜4およびシリコン基板1の部分を酸化し、トンネル酸化膜3の端部にバーズビーク部11,12を形成する工程とを備える。

(もっと読む)

半導体装置

【課題】メモリセルアレイ領域の微細化を図りつつ選択ゲート領域及び周辺回路領域における抵抗遅延を回避する半導体装置を提供する。

【解決手段】半導体装置は、半導体層上に形成された第1の絶縁膜12と、第1の電極層13と、第1の電極層13及び第1の絶縁膜12を貫通して半導体層内に至るまで形成され、第1の電極層13と自己整合的に形成され、素子領域を分離し、素子分離絶縁膜からなる複数の素子分離領域15と、素子分離領域15を跨いで第1の電極層13上に形成され、第1の電極層13の表面を露出する開口部を有する第2の絶縁膜16と、第2の絶縁膜16上及び第1の電極層13の露出された表面上に形成され、開口部を介して第1の電極層13と電気的に接続され、第1の電極層13よりも抵抗の低い第2の電極層18と、素子分離領域15の上方に位置し、第2の電極層18に電気的に接続されたコンタクトホール20と上層配線21とを具備する。

(もっと読む)

不揮発性半導体記憶装置の駆動方法及び不揮発性半導体記憶装置

【課題】書き込み・消去を高速化したり、或いはデータの保持特性を向上させる不揮発性半導体記憶装置の駆動方法及び不揮発性半導体記憶装置を提供する。

【解決手段】チャネルと前記チャネルの両側に設けられたソース・ドレイン領域を有する半導体層と、前記チャネルの上に設けられた第1の絶縁膜と、浮遊電極と、第2の絶縁膜と、ゲート電極と、を有する不揮発性半導体記憶装置の駆動方法であって、前記浮遊電極に第1の極性の電荷が注入された状態とするために、前記半導体層と前記ゲート電極との間に、前記第1の極性の電荷を前記第2の絶縁膜に注入する第1の電位差を与え、その後、前記第1の極性と逆極性の第2の極性の電荷を前記第2の絶縁膜に注入する第2の電位差を与え、その後、前記第1の極性の電荷を前記浮遊電極に注入する第3の電位差を与えることを特徴とする不揮発性半導体記憶装置の駆動方法。

(もっと読む)

半導体装置およびその製造方法

【課題】 メモリセルトランジスタの制御ゲート電極として金属シリサイド電極を用いても選択トランジスタメモリの特性劣化を抑制できる半導体装置を提供すること。

【解決手段】 選択トランジスタは、半導体基板11上に設けられたゲート絶縁膜12bと、ゲート絶縁膜13b上に設けられたポリシリコンゲート電極13b,19bと、ポリシリコンゲート電極13b上に設けられ、金属の拡散に対してバリアとなる導電性バリア層30と、導電性バリア層30上に設けられたシリサイドゲート電極25bとを備えている。

(もっと読む)

フラッシュメモリ素子及びその製造方法

【課題】本発明は、フローティングゲートを多層の導電膜が積層された構造で形成して隣接するメモリセル間の干渉現象を減少させることが出来るフラッシュメモリ素子の製造方法を提供することを可能にすることを目的としている。

【解決手段】 半導体基板上にトンネル絶縁膜及び非晶質の第1の導電膜を形成する段階と、非晶質の第1の導電膜を結晶質の第1の導電膜に変形させるための熱処理工程を行う段階と、結晶質の第1の導電膜上に第2の導電膜を形成する段階と、第2の導電膜をパターニングする第1のエッチング工程を行う段階と、結晶質の第1の導電膜上の酸化膜を除去するための第2のエッチング工程を行う段階と、非晶質の第1の導電膜をパターニングする第3のエッチング工程を行う段階とを含むことを特徴とする。

(もっと読む)

1 - 20 / 96

[ Back to top ]