Fターム[5F083EP57]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 絶縁膜 (4,144) | CG・FG間絶縁膜 (2,372) | 製法 (116)

Fターム[5F083EP57]に分類される特許

1 - 20 / 116

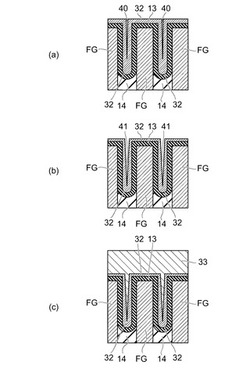

シリコン膜の形成方法及び半導体装置の製造方法

【課題】狭スペースへのシリコン膜の埋め込み性の向上を図る。

【解決手段】実施形態によれば、シリコン膜の形成方法は、凹部20の開口側からボトム側に向けてくぼんだくぼみ40を有するアンドープの第1のシリコン膜32を凹部20に形成する工程を含む。また、前記シリコン膜の形成方法は、凹部20内の第1のシリコン膜32の一部を塩素を含むガスを用いてエッチングし、第1のシリコン膜32に凹部20のボトム側よりも開口側で幅が広い隙間41を形成する工程を含む。また、前記シリコン膜の形成方法は、隙間41に面する第1のシリコン膜32の内壁に不純物を添加する工程を含む。また、前記シリコン膜の形成方法は、不純物の添加後、隙間41を埋める第2のシリコン膜33を形成する工程を含む。

(もっと読む)

半導体装置の製造方法

【課題】デバイス特性の向上を図る。

【解決手段】本実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法においては、半導体層10上に、トンネル絶縁膜11を形成する。トンネル絶縁膜上に、浮遊ゲート電極となる第1導電膜12を形成する。第1導電膜、トンネル絶縁膜、および半導体層を加工することにより、溝15を形成する。溝内の下部側に、第1犠牲膜17を埋め込む。溝内の第1犠牲膜上に、その上面がトンネル絶縁膜の上面よりも高く、第1導電膜の上面よりも低くなるように、第1犠牲膜よりも高密度な第2犠牲膜18を形成する。第1導電膜上および第2犠牲膜上に、絶縁膜19を形成する。絶縁膜上に制御ゲート電極となる第2導電膜WLを形成する。第2導電膜を加工することにより、第2犠牲膜を露出する。第1犠牲膜および第2犠牲膜を除去する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】隣接セルの書き込み閾値の変動を抑制すると共に、制御ゲート電極膜とシリコン基板との間のリーク電流を低減して消去特性を向上させる。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板における素子分離絶縁膜により区画された活性領域上にゲート絶縁膜を介して形成された電荷蓄積層と、前記素子分離絶縁膜の上面、前記電荷蓄積層の側面及び前記電荷蓄積層の上面に形成された電極間絶縁膜と、前記電極間絶縁膜上に形成された制御電極層とを備える。前記電極間絶縁膜は、第1のシリコン酸化膜、第1のシリコン窒化膜、第2のシリコン酸化膜および第2のシリコン窒化膜を積層形成した積層構造を有する。そして、前記電極間絶縁膜は、前記第2のシリコン酸化膜のうちの前記素子分離絶縁膜の上面上の部分の膜厚が前記電荷蓄積層の上面上の部分の膜厚より薄くなるように構成した。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】高電界リークを低減して、書き込み特性を向上させる。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板における素子分離絶縁膜により区画された活性領域上にゲート絶縁膜を介して形成された電荷蓄積層と、前記素子分離絶縁膜の上面、前記電荷蓄積層の側面及び前記電荷蓄積層の上面に形成された電極間絶縁膜と、前記電極間絶縁膜上に形成された制御電極層とを備える。そして、前記電極間絶縁膜は、シリコン窒化膜もしくは高誘電率膜を2層のシリコン酸化膜で挟んだ積層構造または高誘電率膜とシリコン酸化膜の積層構造及び前記積層構造と前記制御電極層の間に形成された第2のシリコン窒化膜を有し、前記第2のシリコン窒化膜のうちの前記電荷蓄積層の上面上の部分を消失させた。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

膜形成方法および不揮発性記憶装置

【課題】より良質な膜を形成する。

【解決手段】実施形態の膜形成方法は、下地の上に設けられた酸素及び窒素の少なくともいずれかを含む膜の表面に、酸素及び窒素の少なくともいずれかを含むイオン化されたガスクラスタを照射して、前記ガスクラスタを照射した後の前記膜の密度を前記ガスクラスタを照射する前の前記膜の密度よりも高くする。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】浮遊ゲートと制御ゲートとの間におけるリークを抑制することができる不揮発性半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコンを含む基板と、前記基板上に設けられたトンネル絶縁膜と、前記トンネル絶縁膜上に設けられた浮遊ゲートと、前記浮遊ゲート上に設けられたリーク抑制部と、前記リーク抑制部上に設けられたゲート間絶縁膜と、前記ゲート間絶縁膜上に設けられた制御ゲートと、を備える。前記リーク抑制部の誘電率は、前記ゲート間絶縁膜の誘電率よりも高くなっている。

(もっと読む)

誘電体膜の形成方法、及びこれを用いる半導体素子のキャパシタの形成方法

【課題】誘電特性及び漏れ電流特性を向上させることのできる半導体素子の誘電体膜の形成方法及びキャパシタの形成方法を提供する。

【解決手段】誘電体膜は、原子層堆積法により、ウェーハ上に酸化ジルコニウム(ZrO2)及び酸化アルミニウム(Al2O3)で構成された誘電体膜を形成する方法であって、チャンバー内に、1つのZrと1つのAl原子とが1つの分子を構成しているソースガスを注入し、ウェーハ上に、ZrO2とAl2O3とからなる[ZrO2]x[Al2O3]y(ここで、x及びyは正数である)膜を形成するステップを繰り返すことにより、ZrO2とAl2O3とで構成された厚さ30Å〜500Åの誘電体膜を形成する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】書き込み特性の向上を図る。

【解決手段】半導体記憶装置の製造方法は、基板10上に、トンネル絶縁膜11を形成し、前記トンネル絶縁膜上に、導電体で構成される電荷蓄積層12を形成し、前記電荷蓄積層、前記トンネル絶縁膜、および前記基板を加工して、前記基板内に、前記電荷蓄積層および前記トンネル絶縁膜を分離する素子分離溝22を形成し、前記素子分離溝内に、上面が前記電荷蓄積層の下面より高く上面より低くなるように素子分離絶縁膜13を埋め込み、前記電荷蓄積層の表面に形成された自然酸化膜30を除去し、前記素子分離絶縁膜および前記電荷蓄積層の表面に、絶縁膜14を形成し、前記自然酸化膜の除去から前記絶縁膜の形成までが、その内部の酸素濃度がコントロールされた製造装置内で行われる。

(もっと読む)

シリコン酸化膜の形成方法、シリコン窒化膜の形成方法、シリコン酸窒化膜の形成方法

【課題】ポリシリコン上において高品質な絶縁膜を形成できる絶縁膜の形成方法を提供する

【解決手段】シリコン酸化膜の形成方法は、基板上にポリシリコン膜を堆積する工程と、

前記ポリシリコン膜の表面を、酸素を含むガスとKrガスを主体とする不活性ガスとよりなる混合ガスにマイクロ波によりプラズマを励起することで形成される原子状酸素O*に曝すことにより、前記ポリシリコン膜の表面にシリコン酸化膜を形成する工程とよりなる。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】酸化膜の窒化速度を向上させる。

【解決手段】ガス流量制御部により処理ガス中の水素含有ガスと窒素含有ガスとの流量をそれぞれ調整し、処理ガス中に含まれる水素原子の数と窒素原子の数との総数に対する水素原子の数の比率Rを0%<R≦80%とする工程と、ガス供給部により処理ガスを処理室内に供給する工程と、プラズマ生成部により励起した処理ガスで酸化膜が形成された基板を処理する工程と、を有する。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】周辺回路領域の素子の寿命が劣化するのを抑制しつつ、浮遊ゲート電極と制御ゲート電極とのカップリング性を確保する。

【解決手段】シリコン基板11は、セル領域および周辺回路領域が設けられている。トンネル絶縁膜12は、セル領域および周辺回路領域のシリコン基板11上に形成されている。浮遊ゲート電極膜13は、セル領域および周辺回路領域のトンネル絶縁膜12上に形成されている。電極間絶縁膜16は、セル領域の浮遊ゲート電極膜13上に形成されている。シリコン酸化膜14および電極間絶縁膜16は、周辺回路領域の浮遊ゲート電極膜13上に形成されている。制御ゲート電極膜17は、セル領域および周辺回路領域の電極間絶縁膜16上に形成されている。

(もっと読む)

不揮発性記憶装置

【課題】基板の活性領域と制御ゲート電極との間の高い耐電圧特性を有する不揮発性記憶装置を提供する。

【解決手段】素子分離絶縁溝を有する基板と、前記基板上の前記素子分離溝の両側に形成された第1および第2のトンネル絶縁膜、第1および第2の浮遊ゲート電極と、前記第1および第2の浮遊ゲート電極の上面を覆い、かつ前記第1の浮遊ゲート電極と第2の浮遊ゲート電極との間、前記第1のトンネル絶縁膜と第2のトンネル絶縁膜との間、および前記素子分離絶縁溝の少なくとも上部を埋めるように形成されたゲート間絶縁膜と、前記ゲート間絶縁膜上に形成された制御ゲート電極と、を有する不揮発性記憶装置を提供する。前記ゲート間絶縁膜は、電子トラップ性を有する第1の絶縁材料からなる電子トラップ層と、前記第1の材料よりも電子トラップ性が低い第2の絶縁材料からなり、前記電子トラップ層を挟む第1および第2の絶縁層とを含む。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】書込・消去特性が高く、動作の信頼性が高い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板と、前記半導体基板上に設けられたトンネル絶縁膜と、前記トンネル絶縁膜上に設けられた第1電極と、前記第1電極上に設けられた電極間絶縁膜と、前記電極間絶縁膜上に設けられた第2電極と、を備える。前記電極間絶縁膜は、積層絶縁層と、前記積層絶縁層上に設けられ、前記積層絶縁層よりもバリアハイトが低い電荷蓄積層と、前記電荷蓄積層上に設けられ、前記電荷蓄積層よりもバリアハイトが高いブロック絶縁層と、を有する。前記積層絶縁層は、第1絶縁層と、前記第1絶縁層上に設けられ、前記第1絶縁層よりもバリアハイトが低い量子効果層と、前記量子効果層上に設けられ、前記量子効果層よりもバリアハイトが高い第2絶縁層と、を有する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルに書き込み用のトランジスタ、読み出し用のトランジスタおよび選択用のトランジスタを備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】半導体と金属の反応速度を制御してメモリセル領域と周辺回路領域とのシリサイド反応の差による不具合を解消する不揮発性半導体記憶装置とその製造方法を提供する。

【解決手段】シリコン基板1の上面にゲート絶縁膜4、第1の導電膜5を形成し、これらをエッチングして素子分離絶縁膜2を埋め込み形成する。電極間絶縁膜6、ゲルマニウム膜7aを形成する。周辺回路領域のゲート電極PGの電極間絶縁膜6に開口6aを形成し、この上に多結晶シリコン膜9aを形成する。ゲート電極MG、PGおよび容量性素子Capの分離加工後に層間絶縁膜10を埋め込む。多結晶シリコン膜9aの上部を露出させ、金属膜を形成してシリサイド化をする。この時、メモリセル領域ではシリサイドが速く進行するが、ゲルマニウム膜7aに達するとジャーマナイド反応は遅くなり、その間に周辺回路領域のシリサイド反応を促進させることができる。

(もっと読む)

半導体装置

【課題】バーズビーク酸化に関する問題を効果的に解決することが可能な半導体装置を提供する。

【解決手段】半導体基板1上に形成されたトンネル絶縁膜2aと、トンネル絶縁膜上に形成された浮遊ゲート電極3と、浮遊ゲート電極上に形成された電極間絶縁膜6と、電極間絶縁膜上に形成された制御ゲート電極7と、トンネル絶縁膜と浮遊ゲート電極との間に形成され、且つ浮遊ゲート電極のチャネル長方向に平行な一対の側面の下端近傍に形成された一対の酸化膜4aと、トンネル絶縁膜と浮遊ゲート電極との間に形成され、且つ一対の酸化膜の間に形成された窒化膜2cとを備え、一対の酸化膜はそれぞれ、チャネル幅方向に平行な断面において上から下に向かってしだいに幅が広くなっている楔状の形状を有している。

(もっと読む)

MOS型半導体メモリ装置、その製造方法およびコンピュータ読み取り可能な記憶媒体

【課題】 電荷蓄積領域として機能する絶縁膜積層体のバンドギャップ構造を長期間維持し、優れたデータ保持特性と、高速でのデータ書換え性能と、低消費電力での動作性能と、高い信頼性と、を同時に兼ね備えたMOS型半導体メモリ装置を提供する。

【解決手段】 MOS型半導体メモリ装置601は、大きなバンドギャップを持つ第1の絶縁膜111および第5の絶縁膜115と、最も小さなバンドギャップを持つ第3の絶縁膜113との間に、両者の中間の大きさのバンドギャップを持つ第2の絶縁膜112および第4の絶縁膜114を備えている。第2の絶縁膜112と第3の絶縁膜113との間には、第1のブロック層112Bが設けられ、第3の絶縁膜113と第4の絶縁膜114との間には、第2のブロック層113Bが設けられている。

(もっと読む)

1 - 20 / 116

[ Back to top ]