Fターム[5F083ER15]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 電子放出 (1,246) | ドレイン側へ放出 (115)

Fターム[5F083ER15]に分類される特許

1 - 20 / 115

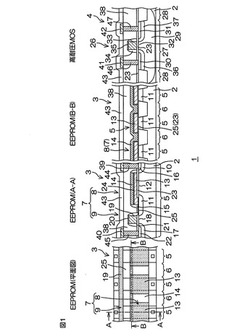

半導体装置および半導体装置の製造方法

【課題】トンネルウィンドウやセレクトゲートの加工寸法のばらつき、およびセレクトゲートのアライメント精度を考慮する必要がなく、セルサイズを小さくすることができる半導体装置およびその製造方法を提供すること。

【解決手段】不揮発性メモリセル7を半導体基板2上に選択的に備える半導体装置1が製造される。この製造方法は、ゲート絶縁膜23上において不揮発性メモリセル7用のアクティブ領域5に、セレクトゲート19を選択的に形成する工程と、セレクトゲート19に対して自己整合的に導入することによってn型トンネル拡散層11を形成する工程と、ゲート絶縁膜23の一部セレクトゲート19に対して自己整合的に除去し、その後の熱酸化によりトンネルウィンドウ25を形成する工程とを含む。

(もっと読む)

半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

半導体装置

【課題】外部からの回路構成情報の呼び出し処理を不要にして、電源投入後すぐに動作できる半導体装置を提供する。

【解決手段】半導体装置は、ワード線とデータ線とが交差する位置にそれぞれ配置された複数の不揮発メモリセル1100を有する。不揮発メモリセル1100の出力にはインバータ回路が接続され、さらに不揮発メモリセルの出力とWBL(Write Bit Line)との間に第1トランジスタM1と、第1トランジスタよりも抵抗が低い第2トランジスタM2とを備える。インバータ回路の出力とRBL(Read Bit Line)との間にはトランスファーゲートを備える。

(もっと読む)

半導体装置

【課題】電荷トラップを含むゲート電極と、電荷トラップを含まないゲート電極とを有する半導体装置において、両ゲート電極下のチャネル層にポテンシャルバリアが形成されないようにする。

【解決手段】基体8上に絶縁膜を介して第一のゲート電極1、第二のゲート電極2が形成され、両ゲート電極1、2を挟んで第一の拡散層5と第二の拡散層6が形成され、両拡散層5、6の間にチャネル層が形成されている。前記絶縁膜は、第一の拡散層5から第二の拡散層6の方向に第一の絶縁領域3、第二の絶縁領域4が配設された、両絶縁領域3、4のうち第二の絶縁領域4が電荷トラップを含み、第一の絶縁領域3を介して第一のゲート電極1が、第二の絶縁領域4を介して第二のゲート電極2が形成され、両ゲート電極1、2底部下に形成されるチャネル層の高さが相互に異なり、第二の拡散層6の先端部は、第二のゲート電極2直下の領域にまで到達している。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】ドレイン領域内のトンネル領域には、ドレイン領域と同一の電位に固定されたドレイン領域に比べて不純物濃度の低い第2導電型の領域と、不純物濃度の低い第1導電型の領域とを形成し、不純物濃度の低い第2導電型の領域と、不純物濃度の低い第1導電型の領域のそれぞれの上面に、フローティングゲート電極への電子注入用と電子引き抜き用のトンネル絶縁膜を独立して設けた。また、データ書き換え時に印加されるストレスが偏らないように、電子引き抜き用のトンネル絶縁膜に比べて電子注入用のトンネル絶縁膜の面積を大きくあるいは厚くした。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】トンネル領域とフローティングゲート電極との間には、膜厚の異なる複数のトンネル絶縁膜を形成した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】フローティングゲート電極は、高い不純物濃度領域と低い不純物濃度領域とからなり、高い不純物濃度領域は、コントロールゲート絶縁膜と接する部分に配置し、低い不純物濃度領域はトンネル絶縁膜と接する領域に配置し、フローティングゲート電極のコントロールゲート絶縁膜と接する表面部分には微細凹凸を形成した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】トンネル領域のエッジ近傍のトンネル絶縁膜上には、トンネル絶縁膜とは異なる材質の絶縁膜からなる電界緩和層を配置した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】トンネル絶縁膜の上部であって、トンネル領域のエッジ部近傍の領域には、フローティングゲート電極とガード絶縁膜を介してドレイン電極と同電位に固定されたトンネル領域エッジ部ガード電極を配置した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】第2導電型のトンネル領域のフローティングゲート電極のエッジ部の下部に、第1導電型の領域からなるフローティングゲート電極エッジの電界集中防止用領域を形成する。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】ドレイン領域内のトンネル領域とフローティングゲート電極領域との間には、トンネル絶縁膜が設けられており、トンネル領域のエッジ近傍のフローティングゲート電極の不純物濃度は、その他の箇所のフローティングゲート電極の不純物濃度に比べて低く設定した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】電気的書き換え可能な半導体不揮発性メモリにおいて、第2導電型のドレイン領域内のトンネル領域と前記フローティングゲート電極領域との間には、トンネル絶縁膜が設けられており、前記フローティングゲート電極は第1導電型の導電体で形成されている電気的書き換え可能な半導体不揮発性メモリ装置。

(もっと読む)

半導体記憶装置

【課題】書き込み/消去の繰り返しによる信頼性の低下を抑制することが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ウェル上にトンネル絶縁膜を介して形成された浮遊ゲートに蓄積する電荷量を制御することにより電気的にデータを書き換え可能な複数のメモリセルを、有するメモリセルアレイと、ウェルに印加するための出力電圧を出力する出力端子と、入力電圧を昇圧して設定された電圧を出力端子に出力する第1のポンプ回路と、入力電圧を昇圧して設定された電圧を出力端子に出力し、第1のポンプ回路よりも高い電圧を出力可能な第2のポンプ回路と、第1のポンプ回路または第2のポンプ回路の少なくとも何れか一方を昇圧動作させるためのアシスト信号を出力するポンプ切替検知回路と、出力電圧の目標電圧を設定するための設定値に基づいて、第1のポンプ回路および第2のポンプ回路の目標電圧を設定する消去パルス制御回路と、を備える。

(もっと読む)

半導体装置及びそれを用いた論理回路

【課題】面積を縮小させることが出来、また歩留まりを向上させる半導体装置及びそれを用いた論理回路を提供すること。

【解決手段】第1トランジスタTr1と第2トランジスタTr2とが形成され、前記第1トランジスタTr1はソース及びドレインとして機能する第1拡散層群103と、第1ゲート電極102と、第2ゲート電極104とを備え、前記第2トランジスタTr2はソース及びドレインとして機能する第2拡散層群201と、電荷を蓄積可能な浮遊ゲート202と、第3ゲート電極200とを備え第2ゲート電極200は、前記第1トランジスタTr1の閾値Vthを制御可能とし、この第2ゲート電極104の電位は、前記浮遊ゲート202が蓄積する電荷量に応じた値である。

(もっと読む)

半導体装置及びその製造方法

【課題】不揮発性メモリを用いた半導体装置において、消去動作の高速化及び低消費電力化を実現する。

【解決手段】チャネル形成領域、トンネル絶縁膜及び浮遊ゲートを順に積層した不揮発性メモリにおいて、チャネル形成領域を酸化物半導体層により構成する。さらに、チャネル形成領域の下側に、浮遊ゲートと対向する位置に消去用の金属配線を設けた構造とする。上記構造により、消去動作において、浮遊ゲートに蓄積された電荷はチャネル形成領域を介して金属配線に引き抜かれる。これにより、半導体装置の消去動作を高速化し、低消費電力化を実現できる。

(もっと読む)

不揮発性メモリ素子を有する装置

【課題】新たな不揮発性メモリ素子を有する装置を提供する。

【解決手段】チャネル形成領域を構成する半導体材料として酸化物半導体を用いた不揮発性メモリ素子を有する装置を提供するものであり、制御ゲートと、第1の絶縁膜を介して制御ゲートと重ねて設けられた電荷蓄積層と、酸化物半導体材料を用いて形成され、第2の絶縁膜を介して電荷蓄積層と重ねて設けられたチャネル形成領域を有する酸化物半導体層と、によって不揮発性メモリ素子が構成されるものである。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高速なアクセスが可能で、かつ、高集積化が可能なスプリットゲート型不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体基板101の主表面の溝に第1、第2のスプリット型不揮発性メモリセルを形成した不揮発性半導体記憶装置100であって、溝内部の対向する第1、第2の側壁102a,102bの表面にそれぞれ第1、第2のスプリット型不揮発性メモリセルの選択ゲート121とコントロールゲート122とが形成され、第1、第2のスプリット型不揮発性メモリセルの選択ゲート121とコントロールゲート122とには、それぞれ異なる電圧を印加することが可能である。

(もっと読む)

半導体記憶装置およびその制御方法

【課題】SOI構造の半導体記憶装置に電気的に書換え可能な不揮発性メモリを形成する手段を提供する。

【解決手段】第1の拡散層16、第2の拡散層17、前記第1および第2の拡散層間に配置された第3の拡散層、および第4の拡散層21と、前記第1および第2の拡散層とそれぞれ一部がオーバーラップし、前記第3の拡散層上から前記第4の拡散層にかけて延在するフローティングゲート電極13と、前記第1の拡散層および前記第3の拡散層に、共通の第1の電位を与える第1の制御線31と、前記第2の拡散層に、第2の電位を与える第2の制御線37と、前記第4の拡散層に、第3の電位を与える第3の制御線33と、を備え、前記フローティングゲート電極が前記第4の拡散層とオーバーラップした面積が、前記第2の拡散層とオーバーラップした面積よりも大きく、前記第1および第3の拡散層とオーバーラップした合計の面積よりも小さい。

(もっと読む)

不揮発性半導体メモリ

【課題】 高温時でも優れたデータ保持特性が維持されるEEPROMセルを有する不揮発性半導体メモリを提供する。

【解決手段】 不揮発性半導体メモリは、センストランジスタ(Tr)と、第1及び第2のセレクトトランジスタ(Tr1、Tr2)と、データ蓄積キャパシタ(C)と、トンネル絶縁膜を有するトンネルウィンドウ(TW)と、コントロールゲート端子(CG)と、セレクトゲート端子(SG)と、ドレイン端子(D)と、ソース端子(S)とを有する。定常状態において、半導体メモリのデータ保持状態に合わせて、自己整合的に、フローティングゲートとトンネルウィンドウ直下領域の電位差が小さくなる方向でバイアス変調されるように構成されている。

(もっと読む)

固体撮像素子及び撮像装置

【課題】ドレイン領域等の不純物拡散領域からフローティングゲートに電荷が注入されてしまうことを防止でき、S/Nを向上できる固体撮像素子及び撮像装置を提供する。

【解決手段】半導体基板に配列された複数の画素部が配列され、画素部が、半導体基板に形成された光電変換部と半導体基板の上方に設けられた電荷蓄積領域と、電荷蓄積領域に電荷を蓄積させて、該電荷に応じた信号を読み出すトランジスタ構造とを備え、トランジスタ構造がソース領域及びドレイン領域を含み、ソース領域及びドレイン領域と光電変換部との間の半導体基板に、ソース領域及びドレイン領域と光電変換部との間で移動する電荷に対して電位勾配のポテンシャル障壁となる障壁層を備える。

(もっと読む)

1 - 20 / 115

[ Back to top ]