Fターム[5F083ER16]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 電子放出 (1,246) | ソース側へ放出 (92)

Fターム[5F083ER16]に分類される特許

1 - 20 / 92

半導体装置

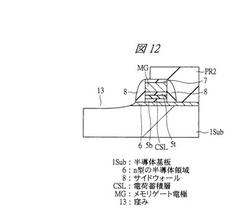

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

半導体装置

【課題】電荷トラップを含むゲート電極と、電荷トラップを含まないゲート電極とを有する半導体装置において、両ゲート電極下のチャネル層にポテンシャルバリアが形成されないようにする。

【解決手段】基体8上に絶縁膜を介して第一のゲート電極1、第二のゲート電極2が形成され、両ゲート電極1、2を挟んで第一の拡散層5と第二の拡散層6が形成され、両拡散層5、6の間にチャネル層が形成されている。前記絶縁膜は、第一の拡散層5から第二の拡散層6の方向に第一の絶縁領域3、第二の絶縁領域4が配設された、両絶縁領域3、4のうち第二の絶縁領域4が電荷トラップを含み、第一の絶縁領域3を介して第一のゲート電極1が、第二の絶縁領域4を介して第二のゲート電極2が形成され、両ゲート電極1、2底部下に形成されるチャネル層の高さが相互に異なり、第二の拡散層6の先端部は、第二のゲート電極2直下の領域にまで到達している。

(もっと読む)

NAND型不揮発性メモリのデータ消去方法

【課題】NAND型不揮発性メモリを提供する。

【解決手段】ビット線と、ソース線と、複数の不揮発性メモリが直列に接続されたNAND型セルと、選択トランジスタと、を有し、不揮発性メモリは、第1の絶縁膜を介した半導体上の電荷蓄積層と、第2の絶縁膜を介した電荷蓄積層上の制御ゲートと、を有し、NAND型セルの一方の端子は、選択トランジスタを介して、ビット線に接続され、NAND型セルの他方の端子は、ソース線に接続されたNAND型不揮発性メモリであって、第1の絶縁膜は、半導体に酸素雰囲気で高密度プラズマ処理を行った後、窒素雰囲気で高密度プラズマ処理を行うことで形成されるNAND型不揮発性メモリ。

(もっと読む)

半導体集積回路

【課題】不揮発性メモリを搭載した半導体集積回路において、外部端子を通して不揮発性メモリの特性テストを実施し、更に、その外部端子にサージ電圧が印加された場合であっても、そのサージ電圧が不揮発性メモリに伝わることを防止する。

【解決手段】半導体集積回路は、不揮発性メモリと、不揮発性メモリに対するデータ書き込み時、書き込み電圧が印加される書き込み制御線と、書き込み制御線に接続された第1ノードと、第1スイッチ回路を介して第1ノードに接続された外部端子と、スイッチ回路を介さずに外部端子に接続された第1ESD保護回路と、動作モードに応じて第1スイッチ回路をON/OFF制御する制御回路と、を備える。動作モードは、外部端子を用いて不揮発性メモリの特性テストを行うテストモードと、外部端子を使用しないユーザモードと、を含む。テストモードにおいて、制御回路は、第1スイッチ回路をONする。ユーザモードにおいて、制御回路は、第1スイッチ回路をOFFする。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリ容量を容易に調整することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】このフラッシュメモリでは、Y方向に配列された4つのP型ウェルPWのうちの端の1つのP型ウェルPWに複数のメモリブロックMB0〜MB3を設け、残りの3つのP型ウェルPWにそれぞれ3つのメモリブロックMB10〜MB12を設ける。また、それぞれメモリブロックMB0〜MB3,MB10〜MB12のX方向に隣接してロウデコーダRD0〜RD3,RD10〜RD12を設ける。メモリブロックMB10〜MB12を削除してメモリ容量を減らす場合でも、周辺回路の再レイアウトが不要となる。

(もっと読む)

プリント不揮発性メモリ

【課題】低コストで高スループットなプリント技術を使用した不揮発性メモリセルを提供する。

【解決手段】同一水平レベルにおいて所定の距離で離間している第1及び第2の半導体アイランドであって、第1の半導体アイランド2が制御ゲートを構成し、第2の半導体アイランド3がソース端子及びドレイン端子を構成する、当該第1及び第2の半導体アイランドと、第1の半導体アイランド2の少なくとも一部の上のゲート誘電体層4と、第2半導体アイランドの少なくとも一部の上のトンネリング誘電体層5と、ゲート誘電体層4とトンネリング誘電体層5の少なくとも一部の上のフローティングゲート7と、制御ゲート2並びにソース端子及びドレイン端子に電気的に接触する金属層と、を備える。一つの効果的な実施形態では、不揮発性メモリセルを、「全プリント」加工技術を使用して製造することができる。

(もっと読む)

シリコン酸化膜の形成方法、シリコン窒化膜の形成方法、シリコン酸窒化膜の形成方法

【課題】ポリシリコン上において高品質な絶縁膜を形成できる絶縁膜の形成方法を提供する

【解決手段】シリコン酸化膜の形成方法は、基板上にポリシリコン膜を堆積する工程と、

前記ポリシリコン膜の表面を、酸素を含むガスとKrガスを主体とする不活性ガスとよりなる混合ガスにマイクロ波によりプラズマを励起することで形成される原子状酸素O*に曝すことにより、前記ポリシリコン膜の表面にシリコン酸化膜を形成する工程とよりなる。

(もっと読む)

半導体記憶装置

【課題】書き込み/消去の繰り返しによる信頼性の低下を抑制することが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ウェル上にトンネル絶縁膜を介して形成された浮遊ゲートに蓄積する電荷量を制御することにより電気的にデータを書き換え可能な複数のメモリセルを、有するメモリセルアレイと、ウェルに印加するための出力電圧を出力する出力端子と、入力電圧を昇圧して設定された電圧を出力端子に出力する第1のポンプ回路と、入力電圧を昇圧して設定された電圧を出力端子に出力し、第1のポンプ回路よりも高い電圧を出力可能な第2のポンプ回路と、第1のポンプ回路または第2のポンプ回路の少なくとも何れか一方を昇圧動作させるためのアシスト信号を出力するポンプ切替検知回路と、出力電圧の目標電圧を設定するための設定値に基づいて、第1のポンプ回路および第2のポンプ回路の目標電圧を設定する消去パルス制御回路と、を備える。

(もっと読む)

半導体装置

【課題】メモリ回路を含む半導体装置の低消費電力化を図ることを課題とする。

【解決手段】メモリ回路を含む半導体装置において、メモリ回路はワード線とビット線で規定される領域に設けられた半導体素子を有するメモリセルと半導体素子を有さないメモリセルを含み、該半導体素子には、酸化物半導体を用いて形成したオフ電流が極めて低いトランジスタを用いるため、読み出し精度が高まり、低電圧動作が可能となる。また、メモリセルは、ハイまたはローのいずれか一方のデータを記憶し、半導体素子を有するメモリセルは、前記データを構成するハイおよびローのうち、少ない方を記憶し、半導体素子を有さないメモリセルは、多い方を記憶する。

(もっと読む)

半導体装置及びその製造方法

【課題】不揮発性メモリを用いた半導体装置において、消去動作の高速化及び低消費電力化を実現する。

【解決手段】チャネル形成領域、トンネル絶縁膜及び浮遊ゲートを順に積層した不揮発性メモリにおいて、チャネル形成領域を酸化物半導体層により構成する。さらに、チャネル形成領域の下側に、浮遊ゲートと対向する位置に消去用の金属配線を設けた構造とする。上記構造により、消去動作において、浮遊ゲートに蓄積された電荷はチャネル形成領域を介して金属配線に引き抜かれる。これにより、半導体装置の消去動作を高速化し、低消費電力化を実現できる。

(もっと読む)

不揮発性メモリ素子を有する装置

【課題】新たな不揮発性メモリ素子を有する装置を提供する。

【解決手段】チャネル形成領域を構成する半導体材料として酸化物半導体を用いた不揮発性メモリ素子を有する装置を提供するものであり、制御ゲートと、第1の絶縁膜を介して制御ゲートと重ねて設けられた電荷蓄積層と、酸化物半導体材料を用いて形成され、第2の絶縁膜を介して電荷蓄積層と重ねて設けられたチャネル形成領域を有する酸化物半導体層と、によって不揮発性メモリ素子が構成されるものである。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中に含まれる不純物の拡散を防止することができ、さらに、ゲート絶縁膜の信頼性及びホットキャリア耐性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】N型シリコン基板1上にゲート酸化膜36およびP+型ゲート電極35を形成する。P+型ゲート電極35の両側にソース/ドレイン領域6を形成する。ゲート酸化膜36およびP+型ゲート電極35中には窒素がドープされ、窒素ドーピング領域30が形成される。

(もっと読む)

新たな高速高密度NANDベース2T−NORフラッシュメモリ設計

【課題】高速高密度NANDベース2T-NORフラッシュメモリ設計の提供。

【解決手段】ツートランジスタNOR フラッシュメモリセルはNANDベース製造プロセスで製造された対称なソース及びドレイン構造を有する。該フラッシュセルはダブルポリNMOSフローティングゲートトランジスタで構成されたストレージトランジスタ、ダブルポリNMOSフローティングゲートトランジスタで構成されたアクセストランジスタ、短絡ポリ1及びポリ2を備えたポリNMOSトランジスタ或いはシングルポリ ポリ1又はポリ2NMOSトランジスタを包含する。該フラッシュセルはファウラー・ノードハイムチャネルトンネルスキームを使用しプログラム及び消去される。NANDベースフラッシュメモリデバイスは、ワードラインに垂直である平行なビットラインとソースラインと共に配置される。書き込みロウデコーダ及び読み出しロウデコーダがフラッシュメモリデバイスが、ページ、ブロック、セクタ又はチップ単位でのベリファイ、プログラム及び読み出し動作を伴うプリプログラムにおいてフラッシュメモリアレイに適宜電圧を供給するために設計される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルを高集積度化することができるチャージトラップ型フラッシュ構造の不揮発性半導体記憶装置を提供する。

【解決手段】半導体記憶装置50は、接地線SUBLとしての半導体基板層1aの第1主面(表面)上に、素子分離層2、ソース電極3a、ソース電極3b、ドレイン電極4a、及びドレイン電極4bを柱状にエッチング開口した開口部5が互いに離間して複数設けられる。開口部5には、半導体基板層1b、積層膜6、及びゲート電極7が埋設され、開口部5の内側には半導体基板層1bが半導体基板層1aと接するように設けられる。半導体基板層1bの内側には、トンネル酸化膜、電荷蓄積膜、電流遮断膜から構成される積層膜6が設けられる。積層膜6の内側にはゲート電極7が埋設される。半導体基板層1bにはソース層8とドレイン層9が垂直方向に複数設けられ、チャネルが垂直方向に設けられるメモリトランジスタが積層形成される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

不揮発性メモリ素子及びその駆動方法

【課題】プログラム及び消去動作部分と読み出し動作部分とを分離させることによって、耐久性またはサイクル特性を画期的に改善させる不揮発性メモリ素子及びその駆動方法を提供する。

【解決手段】単一ポリEEPROMの不揮発性メモリ素子は、第1タイプウェル10上に形成されるフローティングゲート50と、第2タイプウェル20上に形成されるとともにフローティングゲート50と直列連結される複数のトランジスタ30,40と、を備え、これらのトランジスタ30,40のうち、いずれかひとつはプログラム及び消去のための第1トランジスタ30であり、他のひとつは読み出し(reading)のための第2トランジスタ40である。

(もっと読む)

半導体メモリセル及び半導体メモリセルの製造方法、半導体メモリセルの動作方法

【課題】単一ポリEEPROMセルをスタックゲートポリEEPROMセルの水準にスケーリングできる半導体メモリセルを提供する。

【解決手段】単一ポリEEPROMセルは、フローティングゲートFG上にカップリングのためのコンタクトを形成させ、コンタクトはコントロールゲートCGラインによりワードライン用ポリシリコンWLの方向に連結される。このコンタクトとフローティングゲート用ポリシリコンFGとの間にカップリングのための誘電膜102を形成してフローティングゲート用ポリシリコンFGとコンタクトを通じてカップリングを実施する。また、この半導体メモリセルで、プログラム、消去、読み出しが可能なように動作させる。

(もっと読む)

不揮発性半導体記憶装置

【課題】読み出し精度を向上させた不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置100は、複数のメモリストリングMS、及びメモリストリングMSの一端に接続された複数のドレイン側選択トランジスタSDTrを有する。ドレイン側選択トランジスタSDTrは、上方に延びるドレイン側柱状半導体層47と、ドレイン側柱状半導体層47の側面を取り囲むように形成された電荷蓄積層46bと、電荷蓄積層46bを取り囲むように形成されたドレイン側導電層42とを備える。不揮発性半導体記憶装置100は、選択されたメモリストリングMSからデータを読み出す前に、非選択メモリストリングMS(n−sel)に接続された非選択ドレイン側選択トランジスタSDTr(n−sel)の電荷蓄積層46bに電荷を蓄積させる制御信号生成部16を備える。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】カップリング比の増大を図ることができる、半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体基板2に形成されたトレンチ3には、埋設絶縁体4が埋設されている。埋設絶縁体4の上部は、半導体基板2の表面よりも上方に突出している。半導体基板2の表面上には、トンネル酸化膜5が形成されている。埋設絶縁体4の側方において、トンネル酸化膜5上には、フローティングゲート6が形成されている。フローティングゲート6の側部は、埋設絶縁体4の上方に迫り出し、その側面は、平面10およびその下方に連続する曲面11からなる。フローティングゲート6の上面12ならびに平面10および曲面11からなる側面上には、ONO膜13がそれらの各面に接して形成されている。そして、ONO膜13上には、コントロールゲート14が形成されている。

(もっと読む)

1 - 20 / 92

[ Back to top ]