Fターム[5F083ER29]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 負電圧を利用するもの (616)

Fターム[5F083ER29]の下位に属するFターム

ゲート負電圧印加方式 (527)

Fターム[5F083ER29]に分類される特許

61 - 80 / 89

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの占有面積を小さくした不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板と、半導体基板上に行列状に配列された複数の半導体柱と、半導体柱の間の半導体基板上に列方向に帯状に形成され、ワード線として機能する複数の第1の導電領域と、半導体柱の頂部に夫々形成された複数の第2の導電領域と、第2の導電領域を行方向に接続する複数のビット線と、半導体柱の第1と第2の導電領域との間に夫々形成され、第1と第2の導電領域に接する複数のチャネル領域と、半導体柱の間の列方向に、半導体基板上部で且つチャネル領域と対峙して絶縁的に且つ連続的に形成され、制御ゲートとして機能する複数の第3の導電領域と、第3の導電領域よりも高い位置でチャネル領域の上部に、夫々絶縁的に形成された複数の電荷蓄積領域とを具備する。

(もっと読む)

NROM用2次注入

2次電子注入(SEI)は、NROMセルなどのONO層内に別個の電荷蓄積領域を有するNVMセルをプログラムするために使用される。低ワード線電圧(Vwl)、負基板電圧(Vb)、更に狭い及び深いインプラントの種々の組合せによりプロセスが促進される。第2ビット問題を制御することができ、保存及びパンチスルーを改善することができる。より低いSEIプログラミング電流が、ビット線抵抗、必要な接点の数、及び電源要件に関する制約の緩和をもたらすことができる。 (もっと読む)

不揮発性メモリ並びにその製造方法及び動作方法

【課題】第1の1つの導電型基板に形成される1つの不揮発性メモリを提供する。

【解決手段】1つの不揮発性メモリは、1つのゲート、第2の1つの導電型ドレイン領域、1つの電荷蓄積層、及び第2の導電型の第1の1つの希薄ドープ領域を含む。1つのゲートは、第1の1つの導電型基板に形成される。第2の1つの導電型ドレイン領域は、第1の1つの導電型基板の1つのゲートの第1の1つの側部に形成される。1つの電荷蓄積層は、第1の1つの導電型基板の1つのゲートの第1の1つの側部に且つ第2の1つの導電型ドレイン領域と1つのゲートとの間に形成される。第2の導電型の第1の1つの希薄ドープ領域は、第1の1つの導電型基板の1つのゲートの第2の1つの側部に形成される。第2の1つの側部は第1の1つの側部の反対側である。

(もっと読む)

メモリセルを有する集積回路及びこの集積回路への情報記憶方法

【課題】メモリアレーの複雑化及び面積増加をすることなくビット線外乱を抑制する。

【解決手段】メモリアレイを有する集積回路200であり、そのメモリセル205,206は、電気的に絶縁された多数の半導体領域で複数の共通ビット線207を共有するように構成されている。所定の半導体領域は一般的にタブ203,204であるが、そのタブで形成されるメモリセルが書き込み動作のためにアクセスされる場合にはそのタブは所定の電圧にバイアスされ、他の場合にはそのタブは別の電圧にバイアスされる。同じビット線207に沿って多くのメモリセルがあるが、プログラミング期間中では、選択されたメモリセルだけがタブ・バイアスによる外乱を受ける。選択されない複数のタブにおける他のメモリ素子はビット線外乱から保護される。

(もっと読む)

電荷トラップ型メモリ素子及びその製造方法

【課題】ナノ粒子の複合体を利用した電荷トラップ型メモリ素子及びその製造方法を提供する。

【解決手段】本発明によれば、基板と、この基板上にナノ粒子の複合体で形成された電荷トラップ層を有するゲート構造体と、を備える電荷トラップ型メモリ素子と、その製造方法が提供される。本発明によれば、電荷トラップ性の良好なナノ粒子が絶縁性ナノ粒子の間に存在するので、既存の電荷トラップ性の良好なナノ粒子のみを使用してメモリを形成する場合に問題になった金属ナノ粒子が互いに集まる現象が生じない。また、電荷トラップ性の良好なナノ粒子が絶縁性ナノ粒子の複合体からなる電荷トラップ層を備えることにより、優秀なリテンション特性を持つことができる。

(もっと読む)

低不純物濃度MOSキャパシタを有する単一ポリEEPROMセル

【課題】標準CMOSプロセスでEEPROMメモリセルを製造するために、電気的に消去可能なプログラマブルリードオンリーメモリ(EEPROM)メモリセルおよび動作方法を開示する。

【解決手段】EEPROMメモリセルは、ほとんどまたはまったく追加の非標準処理を有しない標準CMOSプロセスで製造可能である。単一多結晶シリコン層を、低不純物濃度MOSキャパシタと組み合わせて使用する。EEPROMメモリセル300で使用される低不純物濃度キャパシタは、設計において非対称であり得る。非対称キャパシタによって領域が縮小する。反転によって引き起こされる更なるキャパシタンス変化も、複数の制御キャパシタを使用することによって低減できる。更に、複数のトンネルキャパシタ302を使用すると、カスタマイズされたトンネル経路の利点が提供される。

(もっと読む)

半導体記憶装置、半導体記憶装置の製造方法及び半導体記憶装置の情報書き換え方法

【課題】書き込み前と書き込み後の読み出し電流の差を大きくできる半導体記憶装置、その製造方法及び情報書き換え方法を提供する。

【解決手段】半導体記憶装置100は、第1拡散領域11と、ゲート絶縁膜32と、ゲート電極31と、第1多層膜141と、第3拡散領域113とを備える。ゲート絶縁膜32は、第1拡散領域11から離れた位置において、半導体基板10の上に形成されている。ゲート電極31は、ゲート絶縁膜32の上に形成されている。第1多層膜141は、第1拡散領域11とゲート絶縁膜32との間において、半導体基板10の上に形成されている。第3拡散領域113は、半導体基板10において第1多層膜141の付近に形成されている。第3拡散領域113は、不純物濃度が第1拡散領域11よりも低い。第1多層膜141には、正電荷(ホール)が主体として蓄積された後に、負電荷(電子)が主体として蓄積されて書き込みが行われる。

(もっと読む)

半導体装置およびその製造方法

【課題】 閾値変調が抑制された半導体装置およびその製造方法を提供する。

【解決手段】 半導体装置は、半導体基板10と、半導体基板10の主表面上にゲート絶縁膜42を介して複数形成された電荷蓄積用のフローティングゲート電極FGと、フローティングゲート電極FG上に形成されるコントロールゲート電極CGとを備える。半導体基板10における隣り合う複数のフローティングゲート電極FGが設けられる部分の主表面の高さが互いに異なる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】 浮遊ゲートFGと制御ゲートG2に加えて、第3ゲートG3を具備するフラッシュメモリで、ローカルビット線抵抗の低減とメモリセルの短チャネル効果抑制を両立させ、メモリセルの微細化、高性能化、高信頼化を促進する。

【解決手段】メモリセルはシリコン基板上に形成されたストライプ状の多段の溝上に形成され、ストライプの方向に第3ゲート、ローカルビット線が延在し、それと垂直な方向に第2ゲートが延在する。メモリトランジスタのゲート長、第3ゲートのゲート幅はシリコン基板に垂直な方向に確保されているので平坦な構造と比べて大きい。

(もっと読む)

半導体装置

【課題】新規な構造を有する一層ゲート型の不揮発性メモリ素子を含む半導体装置を提供する。

【解決手段】半導体装置は、不揮発性メモリ素子C100を含む半導体装置であって、第1領域10Aと、該第1領域10Aに隣接した第2領域10Bと、該第2領域10Bに隣接した第3領域10Cとを含み、さらに、半導体層10に設けられ、不揮発性メモリ素子C100の形成領域を画定する分離絶縁層20と、前記第1領域10Aに形成された第1拡散層12と、前記第2領域10Bに形成されたP型の第1ソース領域及び第1ドレイン領域36と、前記第3領域10Cに形成されたP型の第2ソース領域及び第2ドレイン領域38と、前記半導体層10上方に形成された絶縁層30と、前記絶縁層30上方に形成された導電層32とを含む。

(もっと読む)

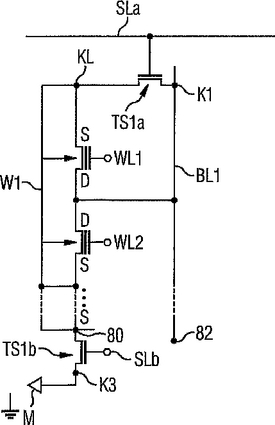

集積されたメモリ回路構造、特にUCPフラッシュメモリ

【課題】チップ面積の低減および電気特性の改善の少なくとも一方を実現できるメモリ回路構造50を提供する。

【解決手段】トランジスタをそれぞれ含む複数のメモリセルをマトリックス状に配置する。上記マトリックスの行における、メモリセルの各トランジスタの各制御電極に各ワード線WL1、WL2を配置する。上記マトリックスの列における、メモリセルの各トランジスタの各端子電極に各ビット線BL1、W1を配置する。スイッチング素子TS1aを、上記列毎に配置する。上記スイッチング素子TS1aは、上記の同一の列に位置する2つの各ビット線BL1、W1同士を電気的に断接できるようになっている。上記スイッチング素子TS1aにより、メモリ回路構造50における、チップ面積を低減および/または電気特性を改善できる。  (もっと読む)

(もっと読む)

検知回路

【課題】電源電圧の急激な変化(電源ノイズ)による誤動作を防止できる検知回路を提供すること。

【解決手段】固定電位点と、パワーオン時、固定電位点からの電位差が変化していく可変電位点との電位差が所定の電位差となったことを検知する、半導体基板に形成される検知回路であって、可変電位点の電位にバイアスされる第1の半導体領域に形成され、可変電位点に接続される第1の抵抗体(r3)と、固定電位点の電位にバイアスされる第2の半導体領域に形成され、可変電位点に接続されない第2の抵抗体(r1)とを具備する。

(もっと読む)

半導体記憶装置

【課題】

絶縁基板上の半導体層を活用した新規な構成により、製造工程が少なく、安価な半導体不揮発性記憶装置を提供する。

【解決手段】絶縁基板上に設けた導電層2を電荷を蓄積する浮遊領域として、前記浮遊領域と絶線されかつ電気的に容量結合する半導体層4と、前記浮遊領域と電気的に容量結合する制御電極領域5を備え、前記浮遊領域2に蓄積する電荷の正負あるいはその電荷量によって生ずる静電力の変化によって前記半導体層4の導電状態を制御することによる。

(もっと読む)

半導体記憶装置及びその書き込み方法

【課題】チップ面積の増大を抑制しつつ、書き込み時にビット線に流れるリーク電流を低減しうる半導体記憶装置の構造及びその書き込み方法を提供する。

【解決手段】 第1の拡散層及び第2の拡散層と、第1の拡散層と第2の拡散層との間の半導体基板上に形成された電荷蓄積層及びゲート電極とを有するN型メモリセルトランジスタと、半導体基板に形成され、第1の拡散層に対して接続可能に構成され、外部電源から供給される電圧を昇圧して出力する電源回路と、N型メモリセルトランジスタへの書き込みの際に、第2の拡散層に基準電圧を印加し、基準電圧に対する負電圧を電源回路から供給して第1の拡散層に印加することにより、第1の拡散層と第2の拡散層との間に電流を流して電荷蓄積層に電荷を蓄積させる書き込み手段とを有する。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】 工程数の増加を伴うことなく、FAMOSにおける消去を実現する。

【解決手段】 P型半導体基板1にN-ウェル3を形成し、N-ウェル3にP-不純物拡散層4を形成し、P-不純物拡散層4上に延伸されたフローティングゲート8をゲート絶縁膜7を介してN-ウェル3上に形成し、この半導体記憶装置の消去動作を行う場合、P-不純物拡散層4を負の電位に設定し、フローティングゲート8をP-不純物拡散層4と容量結合させることにより、フローティングゲート8に蓄積された電子をN-ウェル3側に引き抜く。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】 工程数の増加を伴うことなく、FAMOSにおける消去を実現する。

【解決手段】 素子分離絶縁膜2を介してP型不純物拡散層5a、5bと離間して配置されたP型不純物拡散層5cをN型半導体基板1に形成することにより、N型半導体基板1との間でPN接合ダイオードを形成し、フローティングゲート4とP型不純物拡散層5cとを配線層7を介して電気的に接続し、N型半導体基板1を負の電位に設定し、フローティングゲート4に蓄積されたキャリアをP型不純物拡散層5cを介してN型半導体基板1側に引き抜くことにより、FAMOSの消去を実現する。

(もっと読む)

不揮発性半導体記憶装置およびその書込方法

【課題】ソース−ドレイン間の電位差を小さくしてメモリセルのゲート長を短くすることができる不揮発性半導体記憶装置の書込方法を提供する。

【解決手段】ドレイン付近にバンド間トンネリングによるホットエレクトロン(BBHE)を発生させ、このホットエレクトロンを電荷蓄積層に注入してビットデータの書き込みを行う。ゲート電圧Vg、セルウェル電圧Vsub、ソース電圧Vs、ドレイン電圧Vdの関係をVg>Vsub>Vs>Vdとし、Vg−Vdがバント間トンネル電流の発生電位差以上となり、且つ、Vsub−Vdがトンネル絶縁膜の障壁電位と比べてほぼ同等以上となるようにする。

(もっと読む)

半導体装置

【課題】高性能な書き込み消去特性を有する不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板のp型ウエル2上にゲート絶縁膜6を介して選択ゲート18が形成され、p型ウエル2上に酸化シリコン膜15a、窒化シリコン膜15bおよび酸化シリコン膜15cからなる積層膜15を介してメモリゲート17が形成される。メモリゲート17は、積層膜15を介して選択ゲート18に隣接する。p型ウエル2の選択ゲート18およびメモリゲート17の両側の領域には、ソース、ドレインとしてのn型の不純物拡散層20,21が形成されている。積層膜15に電子を注入することにより、書き込みが行われ、積層膜15にホールを注入することで消去が行われる。積層膜15にホールを注入する際には、積層膜15へのホール注入のための電圧パルスをメモリゲート17および不純物拡散層20に複数回印加する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の書込方法、読出方法、消去方法

【課題】pチャネルMONOSメモリセルにおいて、データ書込時のデータ転送レートの高速化を実現する。

【解決手段】ビットラインをGND〜VCCで動作させるために、プログラム時にセルウェルに4Vのバックゲート電圧を印加する。プログラムモードとベリファイモードとの切り換えを高速化するために、ベリファイも4Vのバックゲート電圧が印加されたままの状態で行う。このため、ベリファイ時にはワードライン(ゲート)に−5Vの読出モード時よりも大きい(絶対値)電圧を印加する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルの信頼性を向上できる不揮発性半導体記憶装置を提供すること。

【解決手段】不揮発性半導体記憶装置は、電荷蓄積層と制御ゲートとを備える第1MOSトランジスタMTと、ドレインが前記第1MOSトランジスタMTのソースに接続された第2MOSトランジスタSTとを含む複数のメモリセルがマトリクス状に配置されたメモリセルアレイ10と、同一行にある前記第1MOSトランジスタMTの前記制御ゲートを共通接続するワード線WLと、同一行にある前記第2MOSトランジスタSTのゲートを共通接続するセレクトゲート線STと、消去動作時において、前記メモリセルアレイ10が形成される半導体基板202と、前記セレクトゲート線SG0〜SG(4m−1)とを電気的に接続するスイッチ素子D0〜D(4m−1)とを備える。

(もっと読む)

61 - 80 / 89

[ Back to top ]