Fターム[5F083ER29]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 負電圧を利用するもの (616)

Fターム[5F083ER29]の下位に属するFターム

ゲート負電圧印加方式 (527)

Fターム[5F083ER29]に分類される特許

81 - 89 / 89

裏側のトラッピングを用いた、拡張性のあるナノ−トランジスタおよびメモリ

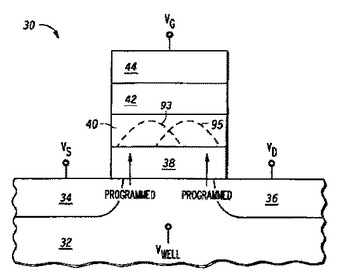

本発明の形態によれば、充電および放電が、薄いシリコンチャネルの裏面に置かれた膜のスタックによって形成されたトラップ領域で起こるデバイス構造が提供される。メモリ機能をもたらす充電メカニズムを、フロントゲートトランジスタのオペレーションから切り離すことによって、フロントゲートの効率的な拡張が可能である。しかしながら、これらのデバイスのユニークな特徴が、ずっと重要である:これらの構造は、トランジスタとメモリの両方として作用することができる。薄い活性シリコンチャネル、および、薄いフロントの酸化物は、本構造を数十ナノメーターへ拡張するための容量を提供し、本デバイスのデュアル機能は、はっきりと異なる2つの電圧範囲を用いることによって得られる。低い電圧では、本構造は、通常のトランジスタとして作用し、より高い電圧では、本構造は、メモリデバイスとして作用する。  (もっと読む)

(もっと読む)

不揮発性メモリセルをプログラミングするための改良システム

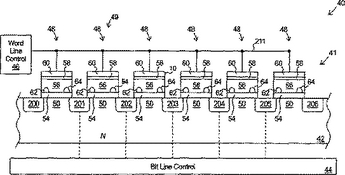

デュアルビット誘電体メモリセル(48)のアレイ(40)は複数のビット線を有している。第1ビット線(201)はアレイ(40)内のメモリセルの列内の複数のメモリセル(38)のそれぞれにソース領域を形成する。第2ビット線(202)は列内の複数のメモリセル(38)のそれぞれにドレイン領域を形成する。第1ビット線(201)と第2ビット線(202)間には、逆の導電性のチャネル領域(50)が設けられており、それぞれと接合を形成している。選択ワード線(211)がチャネル領域(50)の上部に設けられており、また、同じ行内の複数のメモリセル(48)のそれぞれの上部にゲート(60)を形成している。複数の非選択ワード線(210、212)はそれぞれ選択ワード線(211)に並列であり、またそれぞれが複数のメモリセル(49)から選択されたメモリセル以外の列内の複数のメモリセル(48)の1つの上部にゲート(60)を形成している。ワード線制御回路(46)は選択ワード線(211)に正のプログラミング電圧(220)を印加し、また同時にビット線制御回路(44)はドレインビット線(202)に正のドレイン電圧を印加し、正のドレイン電圧よりも小さい正のソース電圧をソースビット線(201)に印加する。  (もっと読む)

(もっと読む)

集積メモリデバイスおよびその製造方法

【課題】容易に製造可能であり、セルのサイズの縮小を可能にするメモリデバイスを提供する。

【解決手段】 本発明の、トンネル電界効果トランジスタ(TFET)と埋込みビット線とを用いたメモリデバイスには、記憶セルの行および列を含む行列が含まれる。各記憶セルには、少なくとも1つのセルトランジスタ(T01〜Tmn)が含まれ、そのセルトランジスタは第1のドープされた領域と第2のドープされた領域とを含んでおり、一方がソース領域(98)であり、もう一方がドレイン領域(152)である。そのメモリデバイスにはワード線(T01〜Tmn)が含まれ、各ワード線は1つの行にあるメモリセルとビット線とに接続されており、各ビット線は1つの列における記憶セルに接続されている。第1のドープされた領域と第2のドープされた領域のドーピングタイプは異なる。

(もっと読む)

ゲート当たりトラップ位置を2つ有する電荷をトラップする不揮発性メモリおよびその動作方法

【課題】容易に製造され高密度の用途に対応する不揮発性メモリ用のメモリ技術を提供する。

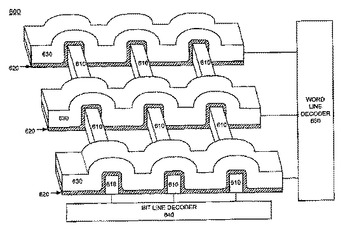

【解決手段】マルチゲート型メモリセルは、半導体本体と、半導体本体上に直列に配列された複数のゲート50,51とを備える。半導体本体上の電荷蓄積構造体は、複数のゲート50,51におけるすべてまたはいくつかのゲートのそれぞれの下の2つの電荷トラップ位置を含む。ソース55およびドレイン56のバイアス電圧を、半導体本体の、直列における第1のゲート50および最後のゲート51の近くに伝える回路、ならびにゲートのバイアス電圧を複数のゲートに伝える回路が備えられる。マルチゲート型メモリセルは、直列における複数のゲート50,51の下の、連続したマルチゲートのチャネル領域58を含み、電荷蓄積位置がゲートのうちのいくつかまたはすべての間にある。

(もっと読む)

電荷トラッピング不揮発性メモリおよびそのゲートバイゲート消去のための方法

【課題】多重ゲートメモリセルは、半導体本体および前記半導体本体に連続的に配置された複数のゲートを有する。

【解決手段】前記半導体本体の電荷蓄積構造は、前記複数のゲート中のゲートの下方に電荷トラッピング位置を具備する。連続した最初のゲートおよび最後のゲートに近接する前記半導体本体に、ソースおよびドレーンバイアス電圧を伝導する回路、および、前記複数のゲートに、ゲートバイアス電圧を伝導する回路を有する。多重ゲートメモリセルは、いくつかの、またはすべての前記ゲートの間の電荷蓄積位置と共に、連続した前記複数のゲートの下方に、連続した多重ゲートチャネル領域を具備する。

(もっと読む)

半導体不揮発性メモリへの情報の記録方法

【課題】半導体不揮発性メモリセルに対して電流効率よく情報の記録を行う方法を提供する。

【解決手段】半導体不揮発性メモリ101は、制御電極30と、第1主電極領域21及び第2主電極領域22とを有するトランジスタ、抵抗変化部23,26、及び電荷蓄積部を備えている。抵抗変化部は、半導体基板の表層領域のうち、第1及び第2主電極領域のうちの少なくとも一方の電極領域と、制御電極と対向するチャネル形成領域12とによって挟まれる部分に第1及び第2主電極領域よりも不純物濃度の低い第2導電型で設けられている。電荷蓄積部は、抵抗変化部上に設けられていて、絶縁層を含みかつ電荷を蓄積可能である。電荷蓄積部に、予め電荷を蓄積することで情報が消去されている半導体不揮発性メモリに情報を記録するに当たり、第1導電型がp型であってかつ第2導電型がn型の場合には、一方の主電極領域に正の高電圧を印加するステップと、他方の主電極領域を接地電圧とするステップと、制御電極に、チャネル形成領域が弱反転する正の電圧を印加するステップとを含んでいる。

(もっと読む)

相補型不揮発性メモリ素子、その動作方法、その製造方法、及びそれを含む論理素子、並びに半導体装置とその読み込み動作回路

【課題】 相補型不揮発性メモリ素子、その動作方法、その製造方法、及びそれを含む論理素子、並びに半導体装置とその読み込み動作回路を提供する。

【解決手段】 第1不揮発性メモリ素子と、前記第1不揮発性メモリ素子上に積層された、第1不揮発性メモリ素子と相補的関係にある第2不揮発性メモリ素子とを含む相補型不揮発性メモリ素子であって、さらに、前記第1及び第2不揮発性メモリ素子の間にボンディング材が備えられた不揮発性メモリ素子である。

(もっと読む)

個別電荷蓄積素子を有するメモリのプログラミング

不揮発性メモリ(100)は、個別電荷蓄積素子(40)を有するトランジスタ群(30)から成るアレイを含む。トランジスタに対しては、2ステップ書き込み方法(60)を使用して書き込みを行ない、この方法では、第1ステップ(68)が低ゲート電圧によるホットキャリア注入(hot carrier injection:HCI)書き込みである。第2ステップ(78)を幾つかのメモリセルに対して選択的に利用して注入電荷分布を変え、トランジスタメモリセル内部の各メモリビットの間の電荷分布間隔を大きくする。書き込みを行なう第2ステップは、書き込み操作に長い余分な時間が加わることなく行われる。一の例では、第1ステップにおいて電子を注入し、そして第2ステップにおいてホールを注入する。2つのステップを実行して分布が形成される結果、蓄積媒体の中心部分の電子電荷が取り除かれる。  (もっと読む)

(もっと読む)

不揮発性メモリデバイス

不揮発性メモリデバイス(100)は、基板(110)、絶縁層(120)、フィン(210)、複数の誘電層(310〜330)及び制御ゲート(510/520)を備える。絶縁層(120)は、基板(110)上に形成され、フィン(210)は、絶縁層(120)上に形成される。誘電層(310〜330)は、このフィン(210)を覆うように形成され、制御ゲート(510/520)は、誘電層(310〜330)上に形成される。誘電層(310〜330)は、メモリデバイス(100)の電荷格納構造として機能する酸化物−窒化物−酸化物層を備える。  (もっと読む)

(もっと読む)

81 - 89 / 89

[ Back to top ]