Fターム[5F083ER30]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 負電圧を利用するもの (616) | ゲート負電圧印加方式 (527)

Fターム[5F083ER30]に分類される特許

161 - 180 / 527

半導体記憶装置、表示装置及び機器

【課題】絶縁基板上に形成される不揮発性メモリ素子において、外部の光が電荷保持部に当ることにより、保持した電荷が、活性化し逃げることを防止することを課題とする。

【解決手段】絶縁基板上に不揮発性メモリ素子を備え、前記不揮発性メモリ素子が、電荷保持膜と、チャネル領域と、前記チャネル領域の両側にソースとドレインとを備える半導体層を備え、前記電荷保持膜が、少なくともその一部の上側と下側とに設けられた、上側遮光体及び下側遮光体の間に位置していることを特徴とする半導体記憶装置により上記課題を解決する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】記憶情報を高速に読み出す半導体集積回路装置の製造方法を提供する。

【解決手段】本発明の半導体集積回路装置の製造方法は、半導体基板上に第1ゲート電極を形成する工程、この工程の後に第1ゲート電極を覆うように半導体基板上に導電性膜を形成する工程、この工程の後に導電性膜の一部を覆うように半導体基板上にマスクパターンを形成する工程、この工程の後にドライエッチングを行いマスクパターンで覆われていない導電性膜をサイドスペーサ状の第2ゲート電極に加工する工程で、且つマスクパターンで覆われた導電性膜を第2ゲート電極のコンタクト領域としてパターニングする工程、この工程の後にマスクパターンを除去する工程、この工程の後に不揮発性メモリセルを覆うように半導体基板上に層間絶縁膜を形成する工程、この工程の後に層間絶縁膜中に第2ゲート電極のコンタクト領域に接続するプラグを形成する工程、を有する。

(もっと読む)

不揮発性半導体記憶装置及びその書き込み方法

【課題】 本発明は、NAND型不揮発性半導体記憶装置の集積密度を向上させることが

できる。

【解決手段】 本発明の不揮発性半導体記憶装置は、半導体基板1表面内に、チャネル領

域を挟んでソース領域2及びドレイン領域3が形成される。そして、チャネル領域上に、

第1の絶縁層8a、トラップ層8b、第2の絶縁層8cの順で積層された積層膜8が形成

される。そして、積層膜8のソース領域側側部には、第3の絶縁層6が形成される。また

、ソース領域2と第3の絶縁層6との間のチャネル領域上には、ゲート絶縁膜5が形成さ

れる。そして、ゲート絶縁膜5上及び積層膜8のソース領域2側端部上には、制御ゲート

7が形成される。また、積層膜8上であって、ソース領域2からドレイン領域3の方向に

向かって、制御ゲート7と離間形成され、かつ互いに離間形成された複数のプログラミン

グゲート9とを備える。

(もっと読む)

マイクロコンピュータ及びデータプロセッサ

【課題】不揮発性メモリセルから記憶情報を高速に読み出すことができる半導体装置を提供する。

【解決手段】マイクロコンピュータは、内部バス68と、前記内部バスに結合されている中央演算部61と、前記内部バスに結合された不揮発性メモリ63とを含む。前記不揮発性メモリは、第1ゲートと第2ゲートとを含む複数の不揮発メモリセルと、前記複数の不揮発メモリセルの一つの前記第1ゲートに結合された第1回路21と、前記複数の不揮発メモリセルの一つの前記第2ゲートに結合された第2回路22と、前記第1回路に供給する第1電圧と前記第2回路に供給する第2電圧とを生成する電圧生成回路VS,77と、を含む。前記第1回路のゲート耐圧は前記第2回路のゲート耐圧より低い。

(もっと読む)

半導体記憶装置

【課題】フローティングゲートとコントロールゲートの間に耐圧を超える電圧が印加されることを防ぐ。

【解決手段】半導体記憶装置は、半導体基板26と、半導体基板26上にゲート絶縁膜を介して設けられた一対の選択ゲート電極4,6と、一対の選択ゲート電極4,6の間の半導体基板26上にゲート絶縁膜を介して設けられた複数のフローティングゲート電極FGと、各フローティングゲート電極FGの間及びフローティングゲート電極FGと選択ゲート電極4,6との間にそれぞれ設けられた複数のコントロールゲート電極CGと、を備えた半導体記憶装置であって、読み出しアクセス時に、読み出しセルとなるフローティングゲート電極FGの第1の側壁に隣接する第1のコントロールゲート電極CGに第1の読み出し電圧が印加され、当該フローティングゲート電極FGの第2の側壁に隣接する第2のコントロールゲート電極CGに前記第1の読み出し電圧より大きい第2の読み出し電圧が印加される。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1の主面f1上に形成された制御ゲート電極CGと、制御ゲート電極CGの側方に電荷蓄積絶縁膜ISを介して形成されたメモリゲート電極MGと、制御ゲート電極CGおよびメモリゲート電極MGの上面に形成された金属シリサイド層SCと、制御ゲート電極CGの側面に形成された側壁絶縁膜IWとを有する不揮発性メモリセルNVMを備えた半導体装置であって、側壁絶縁膜IWは、制御ゲート電極CGの側面と、制御ゲート電極CG上面の金属シリサイド層SCの側面とを一体的に覆うようにして形成され、この側壁絶縁膜IWによって各電極CG,MG上面の金属シリサイド層SCは互いに絶縁されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】一旦記憶情報「0」が書込まれた記憶素子に対する再書込を防止して、読出動作における誤読出を防止する手段を提供する。

【解決手段】ゲート電極の両側に、第1のシリコン酸化膜と電荷蓄積窒化膜と第2のシリコン酸化膜とを積層した2つの記憶素子とを備えた不揮発性半導体記憶装置において、電荷蓄積窒化膜に複数の回数に分割して電荷を注入する場合における書込電圧を、初期書込電圧から設定書込電圧までの間を段階的に増加するよう設定すると共に、セル電流を用いて電荷の保持状態を確認するための目標電流を、電荷の保持状態の変化によりセル電流が増加する傾きより大きい傾きで、初期目標電流から設定目標電流までの間を段階的に増加するよう設定しておき、記憶素子に電荷を注入する場合に、セル電流が目標電流を超えているときは当該書込電圧で記憶素子に電荷を注入し、セル電流が目標電流以下のときは記憶素子へ電荷を注入しないようにする。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置の性能を向上させる。

【解決手段】同一のシリコン基板1上に、制御ゲート電極CGsおよび側壁メモリゲート電極MGsを有するスプリットゲート型メモリセルM1Aと、シングルメモリゲート電極MGuを有するシングルゲート型メモリセルM2とを備える不揮発性半導体記憶装置において、第1領域R1に制御ゲート絶縁膜ICsを介して制御ゲート電極CGsを形成し、第1領域R1には電荷蓄積膜IMsを介して側壁メモリゲート電極MGsを形成し、同時に、第2領域R2には電荷蓄積膜IMuを介してシングルメモリゲート電極MGuを形成する。その際、側壁メモリゲート電極MGsとシングルメモリゲート電極MGuとは同一の工程で形成し、制御ゲート電極CGsと側壁メモリゲート電極MGsとは、互いに電気的に絶縁された状態で、互いに隣り合って配置されるようにして形成する。

(もっと読む)

半導体記憶装置

【課題】電荷蓄積層に蓄積された電荷の抜けを抑制し、データの保存安定性に優れた半導体記憶装置を提供する。

【解決手段】シリコン基板10の表層領域に形成され、シリコン基板10上のゲート絶縁膜14に対向するチャネル領域16とソース領域18との間及び/又はチャネル領域16とドレイン領域20との間に設けられた抵抗変化部22、24と、抵抗変化部22、24上に形成された電荷蓄積部40、60と、を有する半導体記憶装置100であって、電荷蓄積部34、54は、第1酸化膜26、46、データが記憶される前に該データとは電気的に異なる電荷が注入されている電荷蓄積層34、54、及び第2酸化膜30、50が順次積層されてなり、第1酸化膜26、46中に少なくとも1層の電荷抜け防止層28、48が設けられている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】コントロールゲートのゲート長のばらつきを抑え、製造歩留まりを高める不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板10のチャネル領域上に形成された電荷蓄積層11と、電荷蓄積層11上に形成されたコントロールゲート電極30と、コントロールゲート電極30上に形成されたスペーサ層17と、コントロールゲート電極30及びスペーサ層17の側方に絶縁層15を介して形成されたワードゲート電極20とを具備する。スペーサ層17の上面は、ワードゲート電極20から遠ざかるにつれて低くなっている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】コントロールゲート電極を低抵抗化し、高速動作が可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板10のチャネル領域上に形成された電荷蓄積層11と、電荷蓄積層11上に形成されたコントロールゲート電極30と、コントロールゲート電極30上に形成されたシリサイド層63と、コントロールゲート電極30の側方に絶縁層15を介して形成されたワードゲート電極20とを具備する。シリサイド層63の上面は平坦である。

(もっと読む)

半導体記憶装置

【課題】プログラム動作やリード動作を高速化でき,セルトランジスタが過消去状態になってもリード動作を正常に行う半導体記憶装置を提供する。

【解決手段】選択トランジスタとそれに接続されコントロールゲートを有する記憶トランジスタとを有する複数のメモリセルと,複数のメモリセルの選択トランジスタのゲートに接続される複数の選択ゲート線と,複数のメモリセルの記憶トランジスタのコントロールゲートに接続される複数のコントロールゲート線と,複数のメモリセルの記憶トランジスタのソースに接続される複数のソース線と,選択ゲート線に交差し複数のメモリセルの選択トランジスタに接続される複数のビット線とを有し,プログラム動作では記憶トランジスタにソース線からドレイン電流を流し,リード動作では記憶トランジスタにソース線にドレイン電流を流す。

(もっと読む)

不揮発性メモリデバイス及びその製造方法

【課題】電気消去特性の向上に寄与する不揮発性メモリデバイス及びその製造法を提供することを課題とする。

【解決手段】本発明に係る不揮発性メモリデバイスは、半導体基板と;前記半導体基板上に形成されたゲート電極と;前記半導体基板上に形成され、前記ゲート電極に近接して形成された拡散層電極と;前記ゲート電極の側面に形成され、注入された電子を保持する電荷蓄積層と;前記拡散層電極の下部に形成されたLDD領域とを備える。そして、前記電荷蓄積層は、前記ゲート電極の側面にのみ形成され、前記LDD領域に沿って延在しない構造であることを特徴とする。

(もっと読む)

不揮発性メモリ及びマイクロコンピュータ

【課題】不揮発性メモリの消去動作における基板電流の最大値を低減すること。

【解決手段】本発明の不揮発性メモリ(2)は、半導体基板(30)に形成されたソース電極(53)及びドレイン電極(54)と、ソース電極とドレイン電極間の前記半導体基板上に形成された電荷トラップ層(52)と、電荷トラップ層上に配置されたゲート電極(50)とを有する不揮発性メモリセルがアレイ状に複数配列されて成る。不揮発性メモリは、ソース電極とゲート電極とに消去に必要な電圧を印加する消去モードを有する制御回路(33)を備える。前記消去モードにおいて、ゲート電極に電圧の印加を開始してから前記ゲート電極の電圧が消去に必要な所定電圧に達するまでの期間(63)が、ソース電極に電圧の印加を開始してから前記ソース電極の電圧が前記所定電圧に達するまでの期間(64)よりも長くされる。これによって、消去動作における基板電流の最大値が抑えられる。

(もっと読む)

不揮発性半導体記憶素子、及び不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置が備える不揮発性半導体記憶素子を標準的なCMOSプロセスで製造するトランジスタを用いて構成する。

【解決手段】標準的なCMOSプロセスによるトランジスタ二個を一組とし備える記憶部200は、ソース・半導体基板間に発生するバンド間トンネル電流が流れる際に発生する正孔と電子を、半導体基板とゲート酸化膜の境界付近にある結晶欠陥にトラップさせる。結晶欠陥に正孔又は電子をトラップしたトランジスタは閾値が変化するので、記憶部200が備えるNMOSトランジスタ201とNMOSトランジスタ202の閾値の変化によるドレイン電流の差をSRAM部100が備えるセンスアンプ回路で検出することにより記憶されたデータの読み出しを行う。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】 非導電性の電荷トラップ膜を電荷蓄積領域として用いる不揮発性メモリの読み出し電流を大幅に向上させることができ、また、読み出しディスターブによるデータ反転の読み出し不良を撲滅できる半導体集積回路装置を提供する。

【解決手段】 半導体集積回路装置は、半導体柱と絶縁体柱が一方向に交互に敷き詰めた状態で複数配置された柱列と、前記複数の半導体柱に夫々設けられた複数の不揮発性記憶素子であって、前記半導体柱の前記一方向に沿う側面にゲート絶縁膜を介在して制御ゲート電極が設けられ、前記半導体柱の上面部にドレイン領域が設けられ、かつ前記半導体柱の底面部にソース領域が設けられた複数の不揮発性記憶素子と、前記複数の不揮発性記憶素子の夫々の制御ゲート電極を含み、かつ前記柱列の前記一方向に沿う側面に前記一方向に沿って設けられた配線とを有する。

(もっと読む)

半導体装置

【課題】不揮発性メモリセルを備えた半導体装置の高信頼度化を図る。

【解決手段】複数のメモリセルから構成されたメモリアレイに対して電気的に接続された電子回路が、メモリセルを構成する選択ゲート、メモリゲート、ウェル、ソース、およびドレインに電圧を印加し、書込み、消去、緩和パルス印加、ベリファイなどの動作の制御を行う。緩和パルス印加では、電荷蓄積膜の選択ゲート側にホールが電子より多く分布している状態において、選択ゲートに正電圧を印加し、メモリゲートに0Vを印加して、ホールと電子とを結合させて、電荷蓄積膜中の電荷を安定化させる。

(もっと読む)

不揮発性半導体記憶装置の製造方法及び不揮発性半導体記憶装置

【課題】信頼性、動作速度、歩留まりを向上させることが可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、電荷蓄積層14と、コントロールゲート24とを具備する。電荷蓄積層14は、半導体基板10のチャネル領域上方に形成されている。コントロールゲート24は、電荷蓄積層14の上方又は側方に形成され、ポリシリコン及びポリシリコンゲルマニウムのいずれか一方を含む。コントロールゲート24は、更に砒素と、炭素及びリチウムの少なくとも一方とを含む。砒素は、炭素及びリチウムの少なくとも一方がコントロールゲート24に含まれていない場合と比較して、高濃度でコントロールゲート24に含まれている。

(もっと読む)

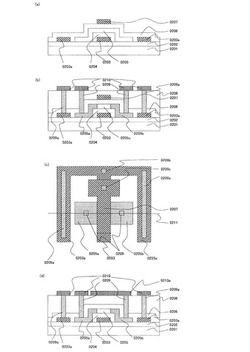

半導体記憶装置及びその製造方法と半導体記憶装置の動作方法

【課題】書込み速度の向上と、かつ読出しディスターブの抑制を両立させることが可能な半導体記憶装置を提供する。

【解決手段】半導体層上に電荷蓄積膜とゲート電極105を形成し、ゲート電極105の下部に形成されたチャネル領域の両側の半導体層に2つの第1導電型の拡散領域A及びBを形成する。チャネル領域は、一方の拡散領域Aが接する側のチャネル幅Waよりも他方の拡散領域Bが接する側のチャネル幅Wbの方が大きく形成される。記憶動作時には一方の拡散領域Aへ他方の拡散領域Bよりも高い電圧を印加し、読出し時には他方の拡散領域Bへ一方の拡散領域Aよりも高い電圧を印加する。

(もっと読む)

半導体記憶装置及びその製造方法と駆動方法

【課題】寄生抵抗の増大なく、ホットキャリアによる特性劣化を抑制できる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】ガラス基板1上に形成した半導体層3と、半導体層3上に形成したONO膜による電荷保持膜21と、電荷保持膜21上に設けたゲート電極22とを備える。更に半導体層3にゲーート電極22とオーバーラップするように設けられたニッケルシリサイド等の半導体と金属の化合物からなるソース・ドレイン領域23を有する。

(もっと読む)

161 - 180 / 527

[ Back to top ]