Fターム[5F083ER30]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 負電圧を利用するもの (616) | ゲート負電圧印加方式 (527)

Fターム[5F083ER30]に分類される特許

101 - 120 / 527

不揮発性半導体記憶装置並びにその駆動方法

【課題】 注入効率が高く、書き込まれた情報が安定的に保持される不揮発性半導体記憶装置並びにその駆動方法を提供する。

【解決手段】 メモリセル1は、N型基板2上に、P型の不純物拡散領域3,4を離間して形成し、両領域間に係る前記基板上において、不純物拡散領域3に隣接して形成された第一積層部15と、不純物拡散領域4に隣接し前記第一積層部15と離間して形成された第二積層部16を備える。メモリセル1に対する書き込み処理時において、第一ゲート電極8に対し、同ゲート電極下方に位置する基板2の表面が弱反転状態となる条件の第一負電圧を印加し、第二ゲート電極10に対し、前記第一負電圧よりも絶対値の大きい第二負電圧を印加し、不純物拡散領域4に対して前記第一負電圧よりも絶対値の大きいドレイン電圧を印加し、不純物拡散領域3に対して、前記ドレイン電圧よりも電位の高いソース電圧をそれぞれ印加する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】電荷蓄積層の膜厚を大きくすることなく、電荷蓄積層に電荷をより効率的に捕獲することができる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】トンネル絶縁膜30t、電荷蓄積層CS1、ブロック絶縁膜50およびゲート電極60は、半導体基板20の上において第1のソース・ドレイン領域21および第2のソース・ドレイン領域22の間に順に設けられている。電荷蓄積層CS1は第1の層40tおよび第2の層30n、40nを有する。第1の層40tは第1の窒素原子濃度を有する。第2の層30n、40nは、第1の窒素原子濃度よりも大きい第2の窒素原子濃度を有し、かつトンネル絶縁膜30tおよびブロック絶縁膜50の一方に面している。

(もっと読む)

不揮発性メモリー装置

【課題】MONOS型不揮発性メモリーの消去を行う場合には、FN電流を用いた消去法を用いる場合でも、バンド間トンネリングホットホールを用いた消去を行う場合においても、負電源を用いることが必要となる。負電源を用いるためには別途電気的に分離できるよう配線パターンを設計する必要があり、配線パターンに制約が加わるという課題がある。

【解決手段】接合深さとして、10nm以上500nm以下の値となるようドレイン領域203D、ソース領域203Sを形成した。ドレイン領域203D、ソース領域203Sでの電界強度が大きくとれることから、バンド間トンネリングホットホールをゲート電極206を接地し、ドレイン領域203Dに5[V]程度の電位を供給することで発生させることができ、負電源を用いることなく消去を行うことが可能となる。

(もっと読む)

不揮発性半導体記憶装置

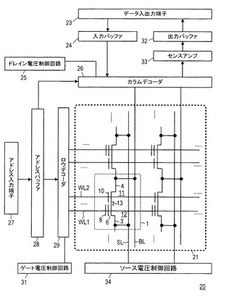

【課題】データ消去の単位となるブロックの集合である複数のコアを有し、任意のコアでのデータ書込み又は消去動作と、他の任意のコアでのデータ読出し動作との同時実行を可能とした不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装は、メモリセルアレイ401aのデータ書き込み・消去の確認読み出し動作で選択されるデータ線DLaと参照信号線REFaの電流を比較するデータ比較回路403aと、メモリセルアレイ401bの通常のデータ読み出し動作で選択されるデータ線DLbと参照信号線REFbの電流を比較するデータ比較回路403bと、参照信号線REFa、REFbにそれぞれ定電流を流すダミーカラムゲート404a、404bと、ダミーカラムゲート404a、404bを並列に駆動する一つの電流源406とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリセルを有する半導体装置において、駆動力の低下を抑えて、信頼度を向上させることのできる技術を提供する。

【解決手段】メモリセルMC1をp型の導電性を示す導電膜からなる選択ゲート電極CGを有する選択用pMIS(Qpc)とp型の導電性を示す導電膜からなるメモリゲート電極MGを有するメモリ用pMIS(Qpm)とから構成し、書込み時には半導体基板1側からホットエレクトロンを電荷蓄積層CSLへ注入し、消去時にはメモリゲート電極MGからホットホールを電荷蓄積層CSLへ注入する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高速化と高集積化を両立し、かつ、高品質な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体基板の表面に平行に設けた複数の溝と交差する方向に設けた選択ゲート電極とメモリゲート電極のうち、一方を先に形成し、他方を先に形成したゲート電極の側壁に形成し、上記選択ゲート電極とメモリゲート電極を挟んで溝の間の突出部分にソースドレイン領域を設けたFINFET構造のスプリットゲート型不揮発性半導体記憶装置において、選択ゲート電極表面とメモリゲート電極表面との高さの差(H2とH3との差)を溝の底面に設けた絶縁層表面とソースドレイン領域表面の高さの差H1以上設ける。

(もっと読む)

不揮発性メモリー装置および不揮発性メモリー装置の製造方法

【課題】MONOS型不揮発性メモリー素子の消去を行う場合として、バンド間トンネリングホットホールによる消去方法を用いることが好適である。この場合、消去できる領域がドレイン領域近傍に制限されるため、FN電流を用いた消去動作よりも消去できる領域が狭く、特にソース領域近傍側の電荷を消去しきれないという課題があり、特に製造工程で帯電したソース領域近傍の電荷を消去することが困難になるという課題がある。

【解決手段】ソース領域203Sに5V程度の電圧をかけ、ドレイン領域203D、ゲート電極206を接地する動作と、ドレイン領域203Dに5V程度の電圧をかけ、ソース領域203S、ゲート電極206を接地する動作とを行う。ソース領域203S近傍に位置するゲート絶縁層204の電荷も消去することが可能となり、製造工程で帯電したソース領域近傍の電荷を消去することが可能となる。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】多値記録が可能なメモリセルを備えた半導体記憶装置の性能を向上させる。

【解決手段】シリコン基板100上に配置された複数のメモリセルを有する半導体集積回路装置であって、個々のメモリセルは、素子分離膜118で規定されたアクティブ領域において、ボトム酸化膜105、電荷蓄積窒化膜106、トップ酸化膜107を介して形成されたメモリゲート電極103を有する。素子分離膜118の一部上面は、アクティブ領域上面の高さよりも高くなるように突出して形成され、電荷蓄積窒化膜106はその素子分離膜118が突出した部分の側壁から、アクティブ領域表面に渡って形成されている。

(もっと読む)

不揮発性半導体記憶装置及びその駆動方法

【課題】電荷蓄積型のメモリセルの繰り返し動作信頼性を向上させた不揮発性半導体記憶装置及びその駆動方法を提供する。

【解決手段】チャネルと前記チャネルの両側に設けられたソース・ドレイン領域とを有する半導体層と、前記チャネル上に設けられた第1絶縁膜及び前記第1絶縁膜上に設けられた電荷蓄積層を有する積層構造体と、前記積層構造体上に設けられたゲート電極と、を有するメモリセルと、前記半導体層よりも前記ゲート電極の電位を低くしてデータの書き込み及び消去のいずれか一方を行う第1パルスを前記半導体層と前記ゲート電極との間に印加し、前記第1パルスの印加の回数に基づいて、前記半導体層よりも前記ゲート電極の電位を高くして前記積層構造体へ電子を注入する第2パルスを前記半導体層と前記ゲート電極との間に印加する駆動部と、を備えたことを特徴とする不揮発性半導体記憶装置を提供する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリウィンドウが広い半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置1において、半導体基板11上にトンネル絶縁膜12及びブロック絶縁膜13を設け、その上に制御ゲート電極18を設ける。そして、トンネル絶縁膜12とブロック絶縁膜13との間に、電荷蓄積粒15を分散させる。電荷蓄積粒15は、シリコン窒化物からなる窒化部16と、窒化部16に接し、シリコンからなるシリコン部17とにより構成する。電荷蓄積粒15は、シリコン窒化膜の表面上にシリコンを堆積させることにより、複数のシリコン粒子を形成した後、シリコン窒化膜をシリコン粒子毎に分断することによって形成されたものである。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】不揮発性メモリの記憶保持特性の向上を図ることができる技術を提供することにある。特に、第1電位障壁膜となる酸化シリコン膜をプラズマ成膜法で形成した場合であっても、酸化シリコン膜の膜質を改善して不揮発性メモリの記憶保持特性の向上を図ることができる不揮発性半導体記憶装置の製造技術を提供する。

【解決手段】第1電位障壁膜EV1の主要構成要素である酸化シリコン膜OX1をプラズマ成膜法により形成した後、高温のプラズマ窒化処理と、一酸化窒素を含む雰囲気中での加熱処理とを組み合わせて実施することにより、酸化シリコン膜OX1の表面に酸窒化シリコン膜SOXを形成し、かつ、酸化シリコン膜OX1と半導体基板1Sの界面に窒素N2を偏析させる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】層間絶縁膜を表面研磨する工程を経て形成される半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1の主面s1上に、高耐圧ゲート絶縁膜IG1および高耐圧ゲート電極EG1からなる高耐圧ゲートG1を形成した後、サリサイドブロック膜SAB、層間絶縁膜ILを順に形成し、その層間絶縁膜ILをCMPにより研磨する。サリサイドブロック膜SABは、下層から順に酸化シリコンを主体とする絶縁膜である保護酸化膜t1と、窒化シリコンを主体とする絶縁膜である保護窒化膜t2とによって形成する。また、層間絶縁膜ILの研磨は、高耐圧ゲートG1上面のサリサイドブロック膜SABに達するまで研磨する。

(もっと読む)

半導体製造装置、ゲルマニウムドットの製造方法およびそれを用いた半導体メモリの製造方法

【課題】ゲルマニウムからなるドットの密度を向上可能な半導体製造装置を提供する。

【解決手段】半導体製造装置600は、石英管610と、反応室620と、石英管610内へH2ガスを供給する配管650と、石英管610内にリモート水素プラズマを生成するアンテナ670、マッチング回路680および高周波電源690と、反応室620内で基板800を保持する基板ホルダー630と、基板800を加熱するヒーター640と、ゲルマンガスを基板800の近傍に供給する噴出器700および配管710とを備える。

(もっと読む)

半導体記憶装置の製造方法

【課題】GIDLが抑制できるメモリセルトランジスタと選択トランジスタからなるフラッシュEEPROMを製造する。

【解決手段】半導体基板の表面に対して斜め方向且つメモリセルトランジスタCT及び選択トランジスタSTのゲート長方向に対して平行する方向に不純物を導入し、水平方向に所定角度回転させた半導体基板の表面に対して斜め方向且つメモリセルトランジスタ及び選択トランジスタのゲート長方向に対して交差する方向に不純物を導入して、メモリセルトランジスタのゲート電極と選択トランジスタのゲート電極との間の基板表面における不純物濃度が、メモリセルトランジスタのゲート電極同士の間の基板表面における不純物濃度及び選択トランジスタのゲート電極同士の間の基板表面における不純物濃度よりも低くなるようにメモリセルトランジスタ及び選択トランジスタのソース、ドレイン拡散層を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層に新たな機能を有する素子を設けた半導体装置を提供する。

【解決手段】半導体基板上に形成された第1配線層150、及び半導体素子200を備える。第1配線層150は、絶縁層156と、絶縁層156の表面に埋め込まれた第1配線154とを備える。半導体素子200は、半導体層220、ゲート絶縁膜160、及びゲート電極210を備える。半導体層220は、第1配線層150上に位置する。ゲート絶縁膜160は、半導体層220の上又は下に位置する。ゲート電極210は、ゲート絶縁膜160を介して半導体層220の反対側に位置する。

(もっと読む)

不揮発性半導体記憶素子とその製造方法

【課題】構造が簡単で、素子サイズを縮小でき、高集積化に適し、且つ欠陥の起こりにくい不揮発性半導体記憶素子を提供する。

【解決手段】不揮発性半導体記憶素子10は、1ビット又は多ビット分のデータを記憶する素子であり、チャネル領域14を挟んで配置されたソース領域12とドレイン領域13と、ゲート絶縁膜15,18と、保護絶縁膜20に埋設され、チャネル領域14上に並んで配置され、ソース領域12及びドレイン領域13に対向しない複数の浮遊ゲート電極16,17と、ゲート絶縁膜15,18上に、チャネル領域14に対向して配置されたコントロールゲート19と、を備える。各浮遊ゲート電極16,17は、物理的或いは電気的にチャネル幅と同等かそれ以上の大きさを有する。

(もっと読む)

メモリ回路におけるリーケージ電流を制限する回路および方法

【課題】スタンバイモードにおける集積回路のリーケージ電流を制限する小型かつ容易に集積できる電流制限回路を実現する。

【解決手段】電流制限回路70はスタンバイモードで動作する間に携帯用無線装置10のメモリ回路24のリーケージ電流を制御する。第1の半導体ウエル64が第2の半導体ウエル66に配置されたメモリ回路24を隔離する。スタンバイモードにおいて、電流制限回路は非導通モードに切り替えられ第2の半導体ウエル64と第1の半導体ウエル66で形成されるダイオードおよび基板62と第2の半導体ウエル64で形成されるダイオードのリーケージ電流を制限する。

(もっと読む)

半導体集積回路装置

【課題】ラッチ型メモリセルのラッチ部のサイズを増大させることなく、データ保持特性を改善する。

【解決手段】ラッチ型メモリセルの記憶ノードを構成するゲート電極配線(21a,21c)と交差する方向に、フラッシュメモリセルトランジスタの固有の配線と同一配線層の導電線(26a,26b)を連続的に延在させて配置する。ゲート電極配線と導電線の交差部において容量を形成し、導電線を固定電位に維持する。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性半導体記憶装置(メモリ)を構成するスプリットゲート型トランジスタで発生するディスターブを抑制して、半導体装置の信頼性を向上することができる技術を提供する。

【解決手段】メモリセル領域に形成されているメモリセルには、コントロールゲート電極CGの側壁に電位障壁膜EV1、電荷蓄積膜ECおよび電位障壁膜EV2を介して、サイドウォール形状のメモリゲート電極MGが形成されている。このとき、メモリセルのコントロールゲート電極CGは矩形形状をしており、ゲート絶縁膜GOXに接する辺の端部に形成される角部が逆テーパ形状に加工されている点に特徴がある。

(もっと読む)

固体撮像素子及び撮像装置

【課題】ノイズの原因となる電荷の注入を防止することができる固体撮像素子及び撮像装置を提供する。

【解決手段】固体撮像素子は、光電変換部3と、半導体基板上に設けられた絶縁膜と、絶縁膜上に設けられた電荷蓄積部と、光電変換部3で発生した電荷を電荷蓄積部に注入するゲート電極を含むトランジスタとを有する固体撮像素子であって、トランジスタのドレイン領域の上方の絶縁膜の少なくとも一部が他の部分よりも厚く形成されている。

(もっと読む)

101 - 120 / 527

[ Back to top ]