Fターム[5F083ER30]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 負電圧を利用するもの (616) | ゲート負電圧印加方式 (527)

Fターム[5F083ER30]に分類される特許

41 - 60 / 527

不揮発性記憶素子

【課題】本発明は、中間絶縁層、電荷蓄積層、及びトンネル絶縁層のうちの少なくとも1つが酸化ガリウムを含まない場合に比べて、情報の書込みと消去を繰り返しても閾値電圧の変動が抑制された不揮発性記憶素子を提供する。

【解決手段】基板と、ソース電極と、ドレイン電極と、チャネル層と、電荷蓄積層と、ゲート電極と、前記チャネル層及び前記電荷蓄積層の間に設けられたトンネル絶縁層と、前記電荷蓄積層及び前記ゲート電極の間に設けられた、中間絶縁層と、を備え、前記中間絶縁層、前記電荷蓄積層、及び前記トンネル絶縁層が酸化ガリウムを含み、前記チャネル層が有機半導体層である不揮発性記憶素子である。

(もっと読む)

半導体装置

【課題】不揮発性メモリと容量素子を有し、性能を向上させる半導体装置を提供する。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MG6nとp型ウエルPW1との間および制御ゲート電極CG4nとメモリゲート電極MG6nとの間には、内部に電荷蓄積層5bを有する絶縁膜5が形成されている。この絶縁膜5は、酸化シリコン膜5aと、その上に形成された窒化シリコン膜5bと、その上に形成された酸化シリコン膜5cと、その上に形成されかつ酸化シリコン膜5cよりも薄い絶縁膜5dとの積層膜からなる。この絶縁膜5dは、ポリシリコンからなるメモリゲート電極MG6nに接している。絶縁膜5dは、Hf,Zr,Al,Ta,Laのうちの少なくとも1種を含む金属化合物により形成されているため、フェルミピニングを生じることができ、誘電率が高い。

(もっと読む)

半導体装置

【課題】不揮発性メモリセルのデータ書き込みおよび消去用の素子において、チャネル全面のFNトンネル電流によりデータを書き換える。

【解決手段】フラッシュメモリの形成領域の半導体基板1Sのn型の埋込ウエルDNW内にp型のウエルHPW1〜HPW3を互いに分離した状態で設け、そのウエルHPW1〜HPW3にそれぞれ容量部C、データ書き込み・消去用の容量部CWEおよびデータ読み出し用のMIS・FETQRを配置した。データ書き込み・消去用の容量部CWEでは、チャネル全面のFNトンネル電流によりデータの書き換え(書き込みおよび消去)を行う。

(もっと読む)

不揮発性半導体メモリ、及び不揮発性半導体メモリへの書込み方法

【課題】不揮発性半導体メモリの周辺回路を小さくし、集積回路の縮小化に寄与する。

【解決手段】p型基板10に形成され、ソース線430と接続するn型拡散層50と、p型基板10上に設けられ、ワード線400と接続するワード電極200と、p型基板10とワード電極200の間に設けられたワード絶縁層と、n型拡散層50上、及びワード電極200の側壁に設けられたトンネル絶縁層と、トンネル絶縁層上に設けられた電荷蓄積層と、電荷蓄積層上に設けられたコントロール絶縁層と、コントロール絶縁層上に設けられ、コントロール線420と接続するコントロール電極300と、を備え、制御部は、メモリ素子600に書込みを行うときに、ソース線430に正電圧を印加し、ワード線400に負電圧を印加し、かつコントロール線420に正電圧を印加する不揮発性半導体メモリ。

(もっと読む)

不揮発性半導体記憶装置

【課題】ホットキャリア注入によって書き換えを行うスプリットゲート型MONOSメモリにおいて、リテンション特性を向上させる。

【解決手段】メモリセルM00の選択ゲート電極は選択ゲート線SG0に接続され、メモリゲート電極はメモリゲート線MG0に接続される。また、ドレイン領域はビット線BL0に接続され、ソース領域はソース線SL0に接続される。さらに、メモリセルM00が形成されたp型ウエル領域にはウエル線WL0が接続される。メモリセルM00に書き込みを行うときは、ウエル線WL0を通じてp型ウエル領域に負電圧を印加しながら、ソースサイド注入方式による書込みを行う。

(もっと読む)

半導体装置およびその製造方法

【課題】電荷を蓄積可能な電荷蓄積膜を有する不揮発性メモリセルを含む半導体装置において、データ保持特性劣化を改善し、その信頼性を向上させることにある。

【解決手段】半導体基板の主面に不揮発性メモリセルを含む半導体装置であって、不揮発性メモリセルは、半導体基板上に第1絶縁膜と、導電膜と、第2絶縁膜と、電荷を蓄積可能な電荷蓄積膜とを有する。また、電荷蓄積膜上に第3絶縁膜と、第1ゲート電極と、第1絶縁膜から前記第1ゲート電極までの一連の積層膜と接するように第4絶縁膜と、第1絶縁膜と並ぶように前記半導体基板上に第5絶縁膜とを有する。さらに、第5絶縁膜上に形成され、第4絶縁膜の側面に前記第1ゲート電極と隣り合うように第2ゲート電極と、第1ゲート電極と第2ゲート電極を挟むように半導体基板にソース領域およびドレイン領域とを有する。半導体装置は、導電膜と電荷蓄積膜が平面的に重なり合うように形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】所定の動作の信頼性を向上する。

【解決手段】不揮発性半導体記憶装置は、第1ワード線WL0に接続された第1メモリセルと、前記第1ワード線に隣接する第2ワード線WL1に接続され、前記第1メモリセルと幅が異なる第2メモリセルと、を具備する。前記第1ワード線に第1電圧が印加され、前記第2ワード線に前記第1メモリセルの幅と前記第2メモリセルの幅との差に基づき補正された前記第1電圧と異なる第2電圧が印加される。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の動作方法

【課題】不揮発性半導体メモリの保持特性の悪化を抑制しつつ、消去動作に要する時間を短縮する。

【解決手段】(a)メモリセルアレイのデータ消去対象領域に消去パルスを印加するステップと、(b)データ消去対象領域に配置されたメモリセルの閾値電圧が消去レベルに達したか否かを判定するステップと、(c)ベリファイ結果に基づいて、新たな消去パルスを印加するか、待機状態に移行するかを決定するステップとを具備する方法で、不揮発性半導体メモリの消去動作を実行する。(b)ステップは、消去パルスの印加が行われた印加期間が経過した後、待機状態に移行する前に閾値電圧が消去レベルに達したか否かを判定する。(c)ステップは、閾値電圧が消去レベルに達していないとき、データ消去対象領域に新たな消去パルスを印加するステップと、閾値電圧が消去レベルに達しているとき、新たな消去パルスの印加を禁止するステップとを含む。

(もっと読む)

半導体装置

【課題】デプレッション型トランジスタを用いて構成される記憶素子を有する半導体装置であっても、正確な情報の保持を可能にすること。

【解決手段】あらかじめ信号保持部への信号の入力を制御するトランジスタのゲート端子に負に帯電させ、且つ電源との接続を物理的に遮断することにより負電荷を保持させる。加えて、一方の端子が当該トランジスタのゲート端子に電気的に接続される容量素子を設け、当該容量素子を介して当該トランジスタのスイッチングを制御する。

(もっと読む)

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法に対する様々な実施例が与えられる。一実施例では、半導体デバイスは、ゲート層、誘電体層、メモリ層、ソース層、半導体チャネル層、及びドレイン層を含む。ソース層は電気的浸透性及びパーフォレーションを有する。半導体チャネル層はソース層及びメモリ層と接触する。ソース層及び半導体チャネル層は、ゲート電圧チューナブル電荷注入バリアを形成する。  (もっと読む)

(もっと読む)

半導体装置

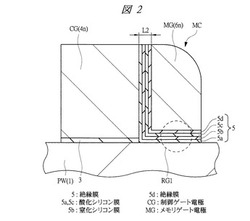

【課題】半導体装置の信頼性を向上する。

【解決手段】メモリセルMCは、半導体基板1の主面上のゲート絶縁膜5を介して設けられたコントロールゲート電極CGと、コントロールゲート電極CGの側面および半導体基板1の主面に沿って設けられたONO膜9と、ONO膜9を介してコントロールゲート電極CGの側面および半導体基板1の主面上に設けられたメモリゲート電極MGとを有する。コントロールゲート電極CGおよびメモリゲート電極MGの上部には、シリサイド膜15およびシリサイド膜15の表面の酸化によって形成された絶縁膜51が設けられている。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み/消去におけるディスターブを抑制し、かつ面積の増大を抑えた不揮発性半導体記憶装置を提供する。

【解決手段】複数のメモリセルMCを含む第1セルアレイ32が形成された第1導電型の第1のウェル領域と、複数のメモリセルMCを含む第2セルアレイ32が形成された第1導電型の第2のウェル領域と、第1、第2のウェル領域を含む第2導電型の第3のウェル領域とを備える。さらに、第1セルアレイ32が含むメモリセルと第2セルアレイ32が含むメモリセルとに共通に接続されたビット線BLと、ビット線BLに接続されたカラムデコーダ13とを備える。

(もっと読む)

不揮発性フラッシュメモリ

【課題】低消費電力、低減されたリーク問題、および単純なプロセスを伴った新規なフラッシュメモリ、新規なプログラミング方法、およびそのセンシングスキームを提供する。

【解決手段】ワード線218、第1のビット線204、および第2のビット線206を備えた不揮発性メモリセル200を動作させる方法は、メモリセル200をプログラミングする工程を有し、そのプログラミングする工程が、高い正電圧のバイアスを第1のビット線に印加し、接地バイアスを第2のビット線に印加し、高い負電圧のバイアスをワード線に印加することを備え、正帯電ホールが誘電体層212を介してトラッピング層214に突き抜けるようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】不揮発性メモリを用いた半導体装置において、消去動作の高速化及び低消費電力化を実現する。

【解決手段】チャネル形成領域、トンネル絶縁膜及び浮遊ゲートを順に積層した不揮発性メモリにおいて、チャネル形成領域を酸化物半導体層により構成する。さらに、チャネル形成領域の下側に、浮遊ゲートと対向する位置に消去用の金属配線を設けた構造とする。上記構造により、消去動作において、浮遊ゲートに蓄積された電荷はチャネル形成領域を介して金属配線に引き抜かれる。これにより、半導体装置の消去動作を高速化し、低消費電力化を実現できる。

(もっと読む)

半導体記憶装置

【課題】スプリットゲート型のMONOSメモリセルを有する半導体記憶装置において、SSI方式による書込み時のディスターブ耐性を向上させる。また、非選択メモリセルのディスターブ耐性が向上することにより、メモリモジュールの面積を低減させる。

【解決手段】メモリゲート電極12の側面において、電荷蓄積膜9と絶縁膜11との間に絶縁膜10を形成し、メモリゲート電極12側面の絶縁膜10および11の合計の厚さを、メモリゲート電極12下部の絶縁膜11の厚さよりも厚く形成する。

(もっと読む)

半導体記憶装置

【課題】メモリセルに負の閾値電圧を設定することができ、しかも安定な動作が可能な半導体記憶装置を提供する。

【解決手段】ワード線、及びビット線に接続された複数のメモリセルがマトリックス状に配置され、前記メモリセルに負の閾値電圧を設定することが可能なメモリセルアレイと、前記ワード線、及びビット線の電位を制御する制御回路と、前記制御回路は、前記ビット線のうち第1のビット線BLoに接続されたメモリセルから負の閾値電圧の読み出し動作を行なう場合、前記第1のビット線に隣接して配置された第2のビット線BLeと、前記メモリセルアレイが形成されたウェルと、前記メモリセルアレイのソース線SRCに、正の第1の電圧Vfixを供給し、選択セルのワード線に前記第1の電圧より低い正の電圧を供給する。

(もっと読む)

不揮発性メモリセル、これを有するメモリアレイ、並びに、セル及びアレイの操作方法

【課題】自己収束消去動作を容易にすると共に保持状態の期間におけるメモリデバイスの電荷蓄積層内での電荷保持能力を保持してもいるトンネル誘電体構造を有する不揮発性メモリデバイスの提供。

【解決手段】半導体基板101であって、該基板の表面より下に配置され且つチャネル領域106によって分離されたソース領域102及びドレイン領域104を備えた半導体基板と、前記チャネル領域より上に配置されたトンネル誘電体構造102であって、低いホールトンネリング障壁高さを有する少なくとも1つの層を備えたトンネル誘電体構造と、前記トンネル誘電体構造より上に配置された電荷蓄積層130と、前記電荷蓄積層より上に配置された絶縁層140と、前記絶縁層より上に配置されたゲート電極150とを有するメモリセル、該メモリセルのアレイ及び操作方法と共に開示する。

(もっと読む)

半導体装置

【課題】不揮発性メモリを構成するメモリセルのサイズを縮小できる技術を提供する。

【解決手段】本発明では、ソース線S1がメモリセルMC1AとメモリセルMC8Aで共通となっている。これにより、メモリセルMC1AやメモリセルMC8Aごとに電気的に独立したソース線を設ける必要がなく、メモリセルのサイズを縮小化することができる。具体的に、共通するソース線S1は、ビット線D1やビット線D8と並行するように配置されているのではなく、選択ゲート線CGL1やメモリゲート線MGL1と並行するように延在している。これにより、メモリセルMC1A〜メモリセルMC8A間の間隔を狭めることができるので、メモリセルアレイ全体の占有面積を縮小化することができる。このソース線S1は、メモリセルMC1B〜メモリセルMC8Bとも共通化されている。

(もっと読む)

記憶装置

【課題】ロジック回路を増やすことなく、第三者がメモリセルにアクセスできずかつ必要な場合にはいつでもアクセス可能なメモリセルを有する記憶装置を提供する。

【解決手段】本実施形態は、第1のメモリセルと、第2のメモリセルと、を有し、第2のメモリセルに設けられた第2のトランジスタの第2のチャネルが酸化物半導体膜からなる記憶装置であって、第2のメモリセルからのデータの読み出しは第2のトランジスタに紫外線を照射している時に行われる記憶装置によって解決する。

(もっと読む)

MOS型半導体メモリ装置、その製造方法およびコンピュータ読み取り可能な記憶媒体

【課題】 電荷蓄積領域として機能する絶縁膜積層体のバンドギャップ構造を長期間維持し、優れたデータ保持特性と、高速でのデータ書換え性能と、低消費電力での動作性能と、高い信頼性と、を同時に兼ね備えたMOS型半導体メモリ装置を提供する。

【解決手段】 MOS型半導体メモリ装置601は、大きなバンドギャップを持つ第1の絶縁膜111および第5の絶縁膜115と、最も小さなバンドギャップを持つ第3の絶縁膜113との間に、両者の中間の大きさのバンドギャップを持つ第2の絶縁膜112および第4の絶縁膜114を備えている。第2の絶縁膜112と第3の絶縁膜113との間には、第1のブロック層112Bが設けられ、第3の絶縁膜113と第4の絶縁膜114との間には、第2のブロック層113Bが設けられている。

(もっと読む)

41 - 60 / 527

[ Back to top ]