Fターム[5F083ER30]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 負電圧を利用するもの (616) | ゲート負電圧印加方式 (527)

Fターム[5F083ER30]に分類される特許

21 - 40 / 527

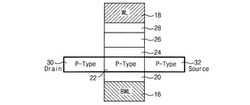

チャージトラップインシュレータメモリ装置

【課題】ナノスケールチャージトラップインシュレータメモリ装置において維持特性を向上させ、多数のセル絶縁層を用いて多数のチャージトラップインシュレータセルアレイが垂直方向に積層してセル集積容量を高める技術を開示する。

【解決手段】

多数の上部ワードライン及び下部ワードラインと、多数のビットライン及びセンシングラインと、上部/下部ワードラインとビットラインの交差領域に配置される多数のメモリセルアレイと、チャージトラップインシュレータからビットラインに格納データが出力される多数のメモリセルと、メモリセルをビットライン及びセンシングラインと各々選択的に連結する第1のスイッチング素子及び第2のスイッチング素子とを含み、チャージトラップインシュレータの極性に従い抵抗変化するP型フロートチャンネルと、その両側に形成されたP型ドレイン領域及びP型ソース領域とを含む。

(もっと読む)

不揮発性メモリ及びその製造方法

【課題】

不揮発性メモリ構造を提供する。

【解決手段】

必要に応じて、LDD領域が、アクティブ領域のゲートチャネル領域の保護のためのマスクを用いてイオン注入によって形成され得る。2つのゲートが、互いに離隔され、アクティブ領域の中央領域の2つの側方のそれぞれでアイソレーション構造上に配設される。これら2つのゲートの各々は、その全体がアイソレーション構造上に配置されてもよいし、部分的にアクティブ領域の中央領域の側方部分に重なってもよい。電荷トラップ層及び誘電体層が、格納ノード機能を果たすように、2つのゲートの間且つアクティブ領域上に形成される。これらは更に、スペーサとして機能するように、2つのゲートの全ての側壁上に形成されてもよい。ソース/ドレイン領域が、ゲート及び電荷トラップ層の保護のためのマスクを用いて、イオン注入によって形成される。

(もっと読む)

プリント不揮発性メモリ

【課題】低コストで高スループットなプリント技術を使用した不揮発性メモリセルを提供する。

【解決手段】同一水平レベルにおいて所定の距離で離間している第1及び第2の半導体アイランドであって、第1の半導体アイランド2が制御ゲートを構成し、第2の半導体アイランド3がソース端子及びドレイン端子を構成する、当該第1及び第2の半導体アイランドと、第1の半導体アイランド2の少なくとも一部の上のゲート誘電体層4と、第2半導体アイランドの少なくとも一部の上のトンネリング誘電体層5と、ゲート誘電体層4とトンネリング誘電体層5の少なくとも一部の上のフローティングゲート7と、制御ゲート2並びにソース端子及びドレイン端子に電気的に接触する金属層と、を備える。一つの効果的な実施形態では、不揮発性メモリセルを、「全プリント」加工技術を使用して製造することができる。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

フラッシュEEPROM(FLASHEEPROMMEMORY)の消去方法

【課題】電荷の蓄積を制御することによりメモリセルを消去するフラッシュEEPROMの消去方法を提供する。

【解決手段】フラッシュメモリの消去方法は、F/Nトンネリング期間において、ウェル電極と第二半導体領域に対し正極性の第一電圧バイアスを印加し、且つコントロールゲート電極に対し負極性の第二電圧バイアスを印加するステップと、F/Nトンネリング期間のあとのトラップ減少期間において、ウェル電極と第二半導体領域に対し正極性の第三電圧バイアスを印加し、且つコントロールゲート電極に対し第一ゼロ電圧バイアスを印加するステップと、トラップ減少期間のあとのトラップアシストトンネリング期間において、コントロールゲート電極に対し負極性の第四電圧バイアスを印加し、且つウェル電極と第二半導体領域に対し第二ゼロ電圧バイアスを印加するステップと、を有する。

(もっと読む)

半導体記憶装置へのデータの書込み方法及び半導体記憶装置

【課題】半導体記憶装置のメモリセルの参照セルとなる副記憶領域の読出し電流の変動を抑制して、メモリセルの読出し電流の判定時における誤判定を低減することができる半導体記憶装置へのデータの書込み方法及び半導体記憶装置を提供する。

【解決手段】メモリセルの第1不純物領域及び第2不純物領域に印加される電圧の大小関係が互いに異なる2つのデータ書込みステップによってメモリセルにデータの書込みをなす。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】特性を向上させる不揮発性メモリを有する半導体装置を提供する。

【解決手段】半導体装置を、制御ゲート電極CGと、制御ゲート電極CGと隣合うように配置されたメモリゲート電極MGと、絶縁膜3と、その内部に電荷蓄積部を有する絶縁膜5と、を有するよう構成する。このうち、メモリゲート電極MGは、絶縁膜5上に位置する第1シリコン領域6aと、第1シリコン領域6aの上方に位置する第2シリコン領域6bと、を有するシリコン膜よりなり、第2シリコン領域6bは、p型不純物を含有し、第1シリコン領域6aのp型不純物の濃度は、第2シリコン領域6bのp型不純物の濃度よりも低く構成する。

(もっと読む)

半導体装置

【課題】パーコレーションリークを抑制可能な構造を有する半導体装置を提供する。

【解決手段】ソース領域18、ドレイン領域18及びチャネル領域を有する半導体領域と、チャネル領域上に形成された第1のトンネル絶縁膜12と、第1のトンネル絶縁膜上に形成され、エネルギー障壁を有する障壁層13と、障壁層上に形成された第2のトンネル絶縁膜14と、第2のトンネル絶縁膜上に形成され、SiY(SiO2)X(Si3N4)1-X (ただし、0≦X≦1、Y>0)で表される絶縁膜を具備する電荷蓄積部15と、電荷蓄積部上に形成され、エネルギー障壁の高さを制御する制御電極17とを備え、X及びYは、[2×2X/(4−2X)+(4−4X)/(4−2X)]×[Y/(Y+7−4X)]≧0.016 なる関係を満たし、障壁層は、クーロンブロッケイド条件を満たす導電性微粒子を含んだ微粒子層で形成されている。

(もっと読む)

半導体記憶装置

【課題】 本発明の実施形態によれば、プロセッサの処理速度を低下させることなく、フラッシュメモリの信頼性を維持する半導体記憶装置を提供することができる。

【解決手段】 第1の電極に第1の電位を与え、全てのバックゲート電極に第1の電位よりも低い第2の電位を与え、第1乃至第n−1のフロントゲート電極に第1の電位よりも高い第3の電位を与え、第n以上のフロントゲート電極に第2の電位と第3の電位との間の第4の電位を与えることで半導体層に情報を書き込むことを特徴とする

(もっと読む)

半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな駆動方法を提供する。また、新たな駆動方法により、メモリ素子への書き込み電位のばらつきを低減し、信頼性を向上させる。

【解決手段】半導体装置の駆動方法において、書き込み電位を段階的に上昇させて、同時に読み出し電流を確認し、読み出し電流の結果を書き込み電位に利用して書き込みを行う。つまり、正しい電位で書き込みが行われたか確認しながら書き込みを行うことで、信頼性の高い書き込みを行うことが可能である。

(もっと読む)

半導体不揮発性メモリ

【課題】 本発明は、不揮発性メモリ・セルにおける電荷貯蔵層を論理工程において形成する方法を提供する。

【解決手段】 論理工程において不揮発性メモリ・セルにおける電荷貯蔵層を形成する方法は、基板のアクティブ領域の上にセレクト・ゲートを形成するステップ、その基板のアクティブ領域に部分的に重なる長いポリシリコン・ゲートを形成するステップ、及びその長いポリシリコン・ゲートの間に電荷貯蔵層を充填するステップを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGとp型ウエルPW1との間および制御ゲート電極CGとメモリゲート電極MGとの間には、絶縁膜5が形成されている。この絶縁膜5のうち、メモリゲート電極MGの下面と半導体基板1の上面との間の部分は、酸化シリコン膜9a,9bと酸化シリコン膜9a,9bに挟まれた窒化シリコン膜10aとを有している。絶縁膜5のうち、制御ゲート電極CGの側面とメモリゲート電極MGの側面との間の部分は、酸化シリコン膜6aからなり、窒化シリコン膜10aを有していない。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGとp型ウエルPW1との間および制御ゲート電極CGとメモリゲート電極MGとの間には、絶縁膜5が形成されている。この絶縁膜5のうち、メモリゲート電極MGの下面と半導体基板1の上面との間の部分は、酸化シリコン膜6a,6cと酸化シリコン膜6a,6cに挟まれた窒化シリコン膜6bとを有している。絶縁膜5のうち、制御ゲート電極CGの側面とメモリゲート電極MGの側面との間の部分は、酸化シリコン膜6a,6cと酸化シリコン膜6a,6cに挟まれた空洞CAVとを有し、窒化シリコン膜6bを有していない。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】不揮発性半導体記憶装置の高集積化と高歩留りを実現する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、複数のメモリストリングを有する第1乃至第4のフィン型積層構造9−1,9−2,9−3,9−4と、第1及び第2のフィン型積層構造9−1,9−2の第2の方向の一端を互いに接続する第1の部分P1と、第3及び第4のフィン型積層構造9−3,9−4の第2の方向の一端を互いに接続する第2の部分P2と、第1及び第3のフィン型積層構造9−1,9−3の第2の方向の他端を互いに接続する第3の部分P3と、第2及び第4のフィン型積層構造9−2,9−4の第2の方向の他端を互いに接続する第4の部分P4とを備える。第1及び第2の部分P1,P2は、ソース領域であり、第3及び第4の部分P3,P4は、ドレイン領域である。

(もっと読む)

半導体装置およびその製造方法

【課題】サイドウォール間に層間絶縁膜を埋め込むときに埋め込み不良の発生を防止できる半導体装置の製造方法を提供する。

【解決手段】シリコン基板2の表面上に、ゲート酸化膜6、ポリシリコン層(第1ゲート層)9、タングステンシリサイド層(第2ゲート層)10および絶縁層8が形成される。絶縁層8が所定のゲートパターンにエッチングされる。タングステンシリサイド層10が前記所定のゲートパターンにエッチングされる。タングステンシリサイド層10の側壁が後退される。この後、ポリシリコン層9が前記所定のゲートパターンにエッチングされる。ゲート酸化膜6が前記所定のゲートパターンにエッチングされる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板上に形成されたFETのソース側のエクステンション領域の抵抗値を低減し、半導体装置の動作速度を向上することができる技術を提供する。

【解決手段】ゲート電極4dの側壁に、ゲート電極4dのゲート長方向の幅が異なる第1サイドウォール6wおよび第2サイドウォール6nをそれぞれ形成する。これにより、第1サイドウォール6wおよび第2サイドウォール6nの形状によって第1サイドウォール6wおよび第2サイドウォール6nの下部に自己整合的に形成されるエクステンション領域37、38の半導体基板SBの上面の幅をそれぞれ異なる長さで形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板の結晶性の悪化を招くことなく、素子分離トレンチの幅を小さくできる半導体装置の製造方法を提供する。

【解決手段】マスク用窒化膜51およびパッド酸化膜52からなるハードマスクを用いて、シリコン基板2がエッチングされることにより、素子分離トレンチ21が形成される。素子分離トレンチ21の内面に熱酸化法によりライナー酸化膜22が形成される。続いて、半導体基板2を窒素雰囲気中に配置して、半導体基板2が熱処理される。熱処理後に、エッチングにより、ライナー酸化膜22が薄膜化される。そして、HDP−CVD法により、絶縁物23が素子分離トレンチ21内に埋め込まれる。

(もっと読む)

メモリストリングにダイオードを有する3次元アレイのメモリアーキテクチャ

【課題】信頼できる非常に小型の記憶素子を含む、3次元集積回路メモリ用の構造を低い製造コストで提供すること。

【解決手段】3次元メモリデバイスは、絶縁材料によって分離され、復号化回路を介してセンスアンプに結合可能なストリングとして配置された複数の隆起した形状スタック含む。ダイオードは、ストリングのストリング選択端部又は共通ソース選択端部のどちらか一方においてビット線構造に接続される。導電材料の帯片は、隆起した形状のスタックのサイドに側面を有する。ワード線として配列された複数の導電線は、行デコーダに結合することができ、複数の隆起した形状のスタックの上で直交して延びる。記憶素子は、スタック上の電導性帯片の側面と導電線との間の交点における界面領域の多層アレイに設けられる。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】安定した動作を実行可能な不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、複数のメモリストリング、選択トランジスタ、及びキャリア選択素子を備える。メモリストリングは、直列接続されたメモリトランジスタを含む。選択トランジスタは、メモリストリングの一端に一端を接続されている。キャリア選択素子は、選択トランジスタの他端に一端を接続されている。キャリア選択素子は、メモリトランジスタのボディを流れる多数キャリアを決定する。キャリア選択素子は、第3半導体層、金属層、第2ゲート絶縁層、及び第3導電層を備える。第3半導体層は、基板に対して垂直方向に延びる。金属層は、第3半導体層の上面から延びる。第3導電層は、第2ゲート絶縁層を介して、第3半導体層及び金属層を取り囲む。

(もっと読む)

不揮発性記憶装置

【課題】基板の活性領域と制御ゲート電極との間の高い耐電圧特性を有する不揮発性記憶装置を提供する。

【解決手段】素子分離絶縁溝を有する基板と、前記基板上の前記素子分離溝の両側に形成された第1および第2のトンネル絶縁膜、第1および第2の浮遊ゲート電極と、前記第1および第2の浮遊ゲート電極の上面を覆い、かつ前記第1の浮遊ゲート電極と第2の浮遊ゲート電極との間、前記第1のトンネル絶縁膜と第2のトンネル絶縁膜との間、および前記素子分離絶縁溝の少なくとも上部を埋めるように形成されたゲート間絶縁膜と、前記ゲート間絶縁膜上に形成された制御ゲート電極と、を有する不揮発性記憶装置を提供する。前記ゲート間絶縁膜は、電子トラップ性を有する第1の絶縁材料からなる電子トラップ層と、前記第1の材料よりも電子トラップ性が低い第2の絶縁材料からなり、前記電子トラップ層を挟む第1および第2の絶縁層とを含む。

(もっと読む)

21 - 40 / 527

[ Back to top ]