Fターム[5F083GA25]の内容

Fターム[5F083GA25]に分類される特許

181 - 200 / 686

半導体装置及びその製造方法

【課題】ゲート電極への水素の拡散を防止することにより、ゲート絶縁膜の劣化を抑制し、信頼性の高い半導体装置を提供すること。

【解決手段】半導体装置は、ポリシリコンを含むゲート電極と、ゲート電極の少なくとも上面を覆い、水素を貯蔵する機能を有する水素貯蔵層と、を備える。好ましくは、バリア層は、組成式SixNyOZの酸窒化膜を含有し、x:y:z=1:1:0.1〜0.7である。

(もっと読む)

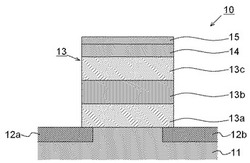

記憶素子及びその製造方法

【課題】素子を微細化しても、安定して動作させることができる記憶素子を提供する。

【解決手段】メモリセル毎に分離して形成され、抵抗値の変化により情報を記憶させることができる記憶層13と、メモリセル毎に分離して形成され、かつ、記憶層13と積層して形成され、Cu,Ag,Zn,Al,Zrから選ばれる少なくとも1種の元素及びTe,S,Seから選ばれる少なくとも1種の元素を含むイオン源層14と、記憶層13及びイオン源層14をメモリセル毎に分離する絶縁層17と、各メモリセルの記憶層13及びイオン源層14の周囲に設けられた、元素の拡散を防止する拡散防止用バリア18を含んで、記憶素子を構成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】筒状形状の容量を高容量にするとともに、下部電極に高抵抗領域が形成されるのを防ぐ半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体装置100は、筒状形状に形成された容量130を含む。半導体装置100は、基板102上に形成された絶縁膜104,106,108,110と、絶縁膜104,106,108,110に設けられた凹部内の底部には形成されず側壁に選択的に形成された第1の金属膜132、および凹部内の底部上および側壁の第1の金属膜132上に形成された第2の金属膜134を含み、筒状形状に形成された下部電極131と、下部電極131上に形成された容量膜136と、容量膜136上に形成された上部電極138とを含む。

(もっと読む)

半導体表示装置

【課題】作製工程を複雑化させることなく、高集積化を実現することが可能な、DRAM混載の集積回路の提供。

【解決手段】DRAMを有する集積回路であって、DRAMには、薄膜トランジスタを備えたメモリセルが複数設けられており、薄膜トランジスタは、活性層と、活性層が有するチャネル形成領域を間に挟んで重なり合っている第1の電極及び第2の電極とを有しており、データに従って薄膜トランジスタのドレイン電圧を制御することで、チャネル形成領域における正孔の蓄積の有無を選択し、正孔の蓄積の有無を把握することでデータを読み出すことを特徴とする集積回路。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供することを課題の一とする。また、信頼性の高い半導体装置の作製方法を提供することを課題の一とする。また、消費電力が低い半導体装置を提供することを課題の一とする。また、消費電力が低い半導体装置の作製方法を提供することを課題の一とする。また、量産性の高い半導体装置を提供することを課題の一とする。また、量産性の高い半導体装置の作製方法を提供することを課題の一とする。

【解決手段】酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すれば良い。具体的には、酸化物半導体層にハロゲン元素を添加した後に加熱処理を施し、不純物を除去して使用すれば良い。ハロゲン元素としては、フッ素が好ましい。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体膜の表面をレジストに曝すことなく、特性が異なる複数のキャパシタを有する半導体装置を製造する。

【解決手段】半導体装置の製造方法は、基板上方に絶縁膜を形成する工程、絶縁膜上方に下部電極層を形成する工程、下部電極層上に強誘電体膜を形成する工程、強誘電体膜上に第1上部電極層を形成する工程、第1上部電極層上に、第1領域を覆う第1レジストを形成する工程、第1レジストをマスクとしてエッチングを行うことにより、第2領域の第1上部電極層を除去するとともに、第2領域の強誘電体膜を削る工程、第1領域の第1上部電極層上及び第1領域以外の強誘電体膜上に、第2上部電極層を形成する工程、第1領域及び第2領域に第2レジストを形成する工程、第2レジストをマスクとして第1上部電極層、第2上部電極層、強誘電体膜及び下部電極層をエッチングし、第1のキャパシタ及び第2のキャパシタを形成する工程、を有する。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供することを課題の一とする。また、信頼性の高い半導体装置の作製方法を提供することを課題の一とする。また、消費電力が低い半導体装置を提供することを課題の一とする。また、消費電力が低い半導体装置の作製方法を提供することを課題の一とする。また、量産性の高い半導体装置を提供することを課題の一とする。また、量産性の高い半導体装置の作製方法を提供することを課題の一とする。

【解決手段】酸素欠損を生じることなく酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すればよい。具体的には、酸化物半導体層に酸素を添加した後に加熱処理を施し、不純物を除去して使用すればよい。特に酸素の添加方法としては、高エネルギーの酸素をイオン注入法またはイオンドーピング法などを用いて添加する方法が好ましい。

(もっと読む)

半導体装置

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。また、半導体装置の信頼性を向上させる。また、半導体装置の性能を向上すると共に、半導体装置の信頼性を向上する。

【解決手段】フローティングゲート電極FGを有するメモリトランジスタとこのメモリトランジスタに直列に接続された制御トランジスタとで構成されたメモリセルを、半導体基板の主面にX方向およびY方向にアレイ状に複数配列させる。そして、X方向に配列したメモリセルのメモリトランジスタのドレイン領域同士を接続するビット配線M1Bを、半導体基板上に形成された多層配線構造のうちの最下層の配線層に設け、このビット配線M1Bがフローティングゲート電極FG全体を覆うようにする。

(もっと読む)

半導体記憶装置

【課題】整流素子における整流特性を劣化させることなく、メモリ素子へのフッ素や水素等の不純物の拡散を防止できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第一方向に延びる導電線L2(j)と、第一方向と交差する第二方向に延びる導電線L3(i)と、導電線L2(j)と導電線L3(i)との間に直列接続された、可変抵抗膜または相変化膜17とp型半導体層及びn型半導体層を含むダイオードとから構成されるセルユニットを備える。さらに、可変抵抗膜または相変化膜17の側面に形成されたシリコン窒化膜20と、前記ダイオードの側面に形成され、シリコン窒化膜20より電荷トラップが少ないシリコン酸化膜21とを備える。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた高性能な半導体装置を提供する。

【解決手段】基板上に酸化物半導体層を形成し、酸化物半導体層上に第1の導電層を形成し、第1の導電層上に第2の導電層を形成し、第2の導電層をエッチングすることで、第1のパターンを形成し、第1のパターンを酸化することにより膨張させ、膨張後の第1のパターンをマスクとして第1の導電層をエッチングすることで、ソース電極及びドレイン電極となる第2のパターンを形成し、膨張後の第1のパターン及び第2のパターン及び酸化物半導体層を覆うゲート絶縁層を形成し、ゲート絶縁層上にゲート電極を形成する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】高集積化が容易な半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置の製造方法において、p形シリコン及びn形シリコンを順次堆積させることにより、シリコンダイオードを形成する工程と、前記シリコンダイオードを選択的に除去してピラーを形成する工程と、前記ピラーの周囲に過水素化シラザン重合体を含む溶液を配置する工程と、前記溶液を加熱することにより、シリコン酸化膜を形成する工程と、を実施する。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体キャパシタ及び常誘電体キャパシタの両方を有する半導体装置を比較的少ない工程で製造できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板110にトランジスタ等を形成した後、メモリセル形成領域及びロジック回路形成領域にそれぞれ強誘電体膜127を電極126a,128aで挟んだ構造の強誘電体キャパシタを形成する。その後、強誘電体キャパシタを覆う層間絶縁膜131を形成し、更にその上にアルミナからなる保護膜132を形成する。そして、ロジック回路形成領域の保護膜132を除去する。これにより、半導体装置の製造工程が完了するまでの間にロジック回路形成領域の強誘電体膜127に水素及び水分が侵入して強誘電体特性が劣化し、強誘電体キャパシタが常誘電体キャパシタとなる。一方、メモリセル形成領域の強誘電体キャパシタは、保護膜132により強誘電体特性が保持される。

(もっと読む)

キャパシタ素子とキャパシタ素子の製造方法および半導体装置

【課題】リーク電流の低減と静電容量の増加の両立を実現するキャパシタ素子とキャパシタ素子の製造方法および半導体装置を提供する。

【解決手段】本発明のキャパシタ素子は、少なくとも上面が第一の窒化金属からなる第一電極と、酸化ジルコニウム膜からなる容量絶縁膜と、ボロン、アルミニウム、ガリウムのいずれかが不純物としてドープされた酸化亜鉛膜からなる第一のバリア膜と、少なくとも下面が第二の窒化金属からなる第二電極と、がこの順で積層されてなることを特徴とする。

(もっと読む)

半導体装置

【課題】小型化が可能な半導体装置を提供する。

【解決手段】半導体装置において、第1の導電性材料からなる第1のコンタクトと、第2の導電性材料からなり、下端部が第1のコンタクトの上端部に接続された第2のコンタクトと、第3の導電性材料からなり、下面が第1のコンタクトの下面よりも上方に位置し、上面が第2のコンタクトの上面よりも下方に位置し、第1及び第2のコンタクトから離隔した中間配線と、を設ける。そして、第2の導電性材料に対する第1の導電性材料の拡散係数は、第2の導電性材料に対する第3の導電性材料の拡散係数よりも小さい。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いたトランジスタと、酸化物半導体以外の半導体材料を用いたトランジスタとを積層して、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと、第1のトランジスタ上に絶縁層と、絶縁層上に第2のトランジスタと、を有し、第1のトランジスタは、第1のチャネル形成領域を含み、第2のトランジスタは、第2のチャネル形成領域を含み、第1のチャネル形成領域は、第2のチャネル形成領域と異なる半導体材料を含んで構成され、絶縁層は、二乗平均平方根粗さが1nm以下の表面を有する半導体装置。

(もっと読む)

スパッタリングターゲットとそれを用いたTi−Al−N膜および電子部品の製造方法

【課題】FeRAMやDRAMなどに使用されるTi−Al−N膜などの成膜用のTi−Al合金ターゲットにおいて、不純物量の低減を図った上で、ターゲットの製造歩留りを高めると共に、膜品質の向上などを図る。

【解決手段】スパッタリングターゲットは、Alを5〜50原子%の範囲で含有するTi−Al合金からなる。このようなTi−Al合金ターゲットにおいて、ターゲットのCu含有量を10ppm以下およびAg含有量を1ppm以下とする。

(もっと読む)

圧電素子、液滴吐出ヘッド、および液滴吐出装置

【課題】圧電体を挟む2つの電極および圧電体層の結晶性の関係が良好な圧電素子を提供する。

【解決手段】圧電素子は、第1電極20と、第2電極40と、第1電極20および第2電極40の間に挟持された圧電体層30と、を含む圧電素子であって、第1電極20および圧電体層30は、ペロブスカイト型の結晶構造を有する酸化物を主成分とし、第2電極40は、面心立方の結晶構造を有する金属を主成分とし、第1電極20、圧電体層30および第2電極40は、それぞれ優先配向構造を有し、第1電極20、圧電体層30および第2電極40の、優先配向軸におけるX線回折強度測定のピークの半値幅を、それぞれf1、f2およびf3(°)としたとき、式(1):f1>f2>f3

の関係を満たす。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

半導体装置及び電子機器

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、ソース電極またはドレイン電極は、第1の導電層と、第1の導電層の端面よりチャネル長方向に伸長した領域を有する第2の導電層と、を含み、第2の導電層の伸長した領域の上に、前記伸長した領域のチャネル長方向の長さより小さいチャネル長方向の長さの底面を有するサイドウォール絶縁層を有する半導体装置である。

(もっと読む)

スパッタリングターゲットとそれを用いたTi−Al−N膜および電子部品の製造方法

【課題】FeRAMやDRAMなどに使用されるTi−Al−N膜などの成膜用のTi−Al合金ターゲットにおいて、不純物量の低減を図った上で、ターゲットの製造歩留りを高めると共に、膜品質の向上などを図る。

【解決手段】スパッタリングターゲットはAlを5〜50原子%の範囲で含有するTi−Al合金からなる。このようなTi−Al合金ターゲットにおいて、Zr含有量およびHf含有量をそれぞれ100ppb以下とする。

(もっと読む)

181 - 200 / 686

[ Back to top ]