Fターム[5F083GA25]の内容

Fターム[5F083GA25]に分類される特許

221 - 240 / 686

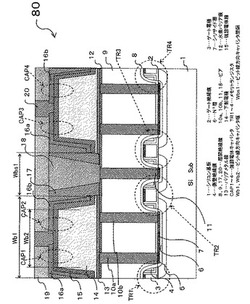

半導体記憶装置

【課題】強誘電体膜の膜質を均一化するチェインFeRAM型半導体記憶装置を提供する。

【解決手段】半導体記憶装置80は、同一素子形成領域に隣接配置される、一対のソース/ドレイン層5を有するメモリトランジスタTR1及びTR2と、メモリトランジスタのソース/ドレイン層5の他方とメモリトランジスタTR2のソース/ドレイン層5の一方に、ビア及びバリアメタル膜13を介して接続される強誘電体キャパシタCAP1及びCAP2とを有する。強誘電体キャパシタCAP1及びCAP2は、バリアメタル膜13上に設けられ、四角錐台形状の下部電極14と、下部電極14を覆うように設けられる強誘電体膜15とを共有し、強誘電体キャパシタCAP1は、強誘電体膜15上に設けられる第1の上部電極16aを有し、強誘電体キャパシタCAP2は、強誘電体膜15上に設けられ、第1の上部電極16aと離間して配置される第2の上部電極16bを有する。

(もっと読む)

半導体装置の製造方法

【課題】素子分離絶縁膜上に引き出したワード線がシリサイド層形成時に断線するのを防止する。

【解決手段】メモリセルトランジスタを形成する領域の外側では、広い範囲にわたり素子分離絶縁膜2aが形成されている。素子分離絶縁膜2aの表面に、ワード線WLと直交する方向に溝状の凹部2bを複数本形成する。この上部にワード線WLを形成すると、凹部2b内にワード線WLを構成する第2導電膜である多結晶シリコン膜が埋め込まれる。ワード線WLを形成後に、ワード線上部にシリサイド層を形成する。このとき、シリサイド反応に必要なシリコンは凹部2b内から不足分が供給できるので、断線の発生を防止できる。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体キャパシタの下部電極材料の選択自由度が高く、ビア工程の少ない半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板101上に形成されたスイッチングトランジスタ301A,301Bと、拡散層121と、トランジスタ301上に形成された層間絶縁膜131と、下部電極211、強誘電体膜212、及び上部電極213を含む強誘電体キャパシタ201A,201Bと、上部電極213の上方に形成された配線層141と、上部電極213と配線層141とを電気的に導通させる第1のプラグTWと、拡散層121と配線層141とを電気的に導通させる第2のプラグV1A,V1Bと、下部電極211の側方に配置されており、下部電極211と拡散層121とを電気的に導通させる第3のプラグCSFとを備える。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】金属配線上にダイオード等の選択素子を有し、選択素子と相変化メモリ等の記憶素子とを共に積層することにより、高性能化、高信頼化を実現し、製造コストを低減する半導体記憶装置とその製造方法を提供する。

【解決手段】第1、第2、第3ポリシリコン膜119,120,121によるダイオードDIODの上に、バッファ層122、相変化材料層123が形成され、層間膜127bより熱伝導率の高いダイオードDIODの一部分を加工せずに配線上に延在させて残すことにより、ダイオードDIODで発生する熱の散逸を大きくする。また、ダイオードDIODの一部をエッチストッパとして利用することで、積層化時のコンタクト開口を一括で行うことを可能とする。

(もっと読む)

半導体装置

【課題】動作速度が低下することを抑制することができる半導体装置を提供する。

【解決手段】半導体装置は、MOSトランジスタ9を有するシリコン基板5と、シリコン基板5上に形成され、配線および絶縁膜により構成された配線層が複数積層された多層配線層と、多層配線層内に埋め込まれた、下部電極(下部電極膜91)、容量絶縁膜92、および上部電極(上部電極膜93)を有しており、メモリ素子を構成する容量素子90と、を備え、容量素子90とMOSトランジスタ9との間にダマシン形状の銅配線(第2層配線25)が少なくとも1層以上形成され、1つの配線(第2層配線25)の上面と容量素子90の下面とが略同一平面上にあり、容量素子90上に銅配線(プレート線配線99)が少なくとも1層以上形成されている。

(もっと読む)

半導体装置

【課題】ヒューズの線幅の縮小化を図ることが可能な半導体装置を提供する。

【解決手段】この半導体装置1では、ヒューズFUに隣接してダミーヒューズDFUを設け、ヒューズFUおよびダミーヒューズDFUの各々の配線幅を最小線幅に設定し、ヒューズFUおよびダミーヒューズDFUの間隔を最小間隔に設定した。したがって、OPCによってヒューズFUおよびダミーヒューズDFUの露光条件が最適化されるので、最小線幅のヒューズFUを形成することができる。

(もっと読む)

半導体装置

【課題】本発明は、安価な半導体装置を提供することを課題とする。

【解決手段】本発明の半導体装置は、相変化メモリと、電磁波を交流の電気信号に変換するアンテナと、アンテナから供給される交流の電気信号を基に電源電位を生成し、生成した電源電位を相変化メモリに供給する電源回路を有する。相変化メモリは、第1の方向に延在するビット線、第1の方向と垂直な第2の方向に延在するワード線及びビット線とワード線の間に設けられた相変化層を有する。

(もっと読む)

無線通信機能を有する半導体装置

【課題】無線通信機能を有する半導体装置の低消費電力化、通信距離の拡大を図る。

【解決手段】メモリ部と、論理部と、メモリ部及び論理部間を電気的に接続する複数の信号線と、を備え、半導体装置及び通信装置間の転送レートをα[bps]、論理部で生成される第1のクロック周波数をKα[Hz](Kは1以上の整数)、複数の信号線のうち読み出し用信号線をn本(nは2以上の整数)、論理部で生成される第2のクロック周波数をLα/n[Hz](Lは、L/n<Kを満たす任意の整数)とした場合、メモリ部に格納されたデータを論理部へ読み出す場合は、第2のクロック周波数Lα/n[Hz]を用いて、n本の読み出し用信号線を介して行う。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】製造工程の簡略化および製造時間短縮を目的とする、メモリセルと周辺回路を備える半導体装置と製造方法を提供する。

【解決手段】トランジスタ形成層30上に、内部に配線10bを備え、かつ、表面に容量パッド14a,14bを有する絶縁層32を形成する工程と、絶縁層32を層間絶縁膜16で覆い、層間絶縁膜16を貫通する第一のホール16aと、第一のホール16aよりも大きい直径を有する第二のホール16bおよび第三のホール16cを、それぞれメモリセル部と周辺回路部に同時に形成する工程と、各ホール内を覆う下部電極18と容量絶縁膜19と上部電極20と容量サポート21を形成することにより第一のホール16aを充填するとともに、第二のホール16bと第三のホール16c内側に空洞を形成する工程と、空洞内に、配線10bと容量パッド14bにそれぞれ接続するコンタクト16d,16eを形成する工程と、を具備している。

(もっと読む)

半導体装置およびその製造方法

【課題】PMOS領域における素子分離膜のライナー窒化膜の除去を行う従来技術による問題を解決した半導体装置およびその製造方法を提供すること。

【解決手段】半導体装置の製造方法は、基板20をエッチングして複数のトレンチを形成するステップと、複数のトレンチ内に第1絶縁膜24Aを埋め込んで第1素子分離膜を形成するステップと、一部のトレンチ(CELL又はPERI NMOS領域のトレンチ)内に埋め込まれた第1絶縁膜24Aをリセスするステップと、リセスされたトレンチの全面にライナー膜26A、27Aを形成するステップと、ライナー膜26A、27Aが形成されたトレンチ内に第2絶縁膜28を埋め込んで第2素子分離膜を形成するステップとを含む。

(もっと読む)

結晶性珪素膜の成膜方法およびプラズマCVD装置

【課題】 プラズマCVD法により良質な結晶性珪素膜を高い成膜レートで成膜する方法を提供する。

【解決手段】 複数の孔を有する平面アンテナにより処理容器内にマイクロ波を導入してプラズマを生成するプラズマCVD装置を用い、式SinH2n+2(ここで、nは2以上の数を意味する)で表される珪素化合物を含む成膜ガスを前記マイクロ波により励起してプラズマを生成させ、該プラズマを用いてプラズマCVDを行うことにより被処理体の表面に結晶性珪素膜を堆積させる。

(もっと読む)

キャパシタおよび半導体装置の製造方法

【課題】 原子層堆積法により成膜された容量膜を含むキャパシタの信頼性を高める。

【解決手段】 本発明のキャパシタの製造方法において、容量膜は、Zr、Hf、LaおよびYからなる群から選択される一または二以上の金属元素を含む有機原料を成膜ガスとして原子堆積法により成膜される。本発明のキャパシタの製造方法は、成膜ガスを用いた原子堆積法における成膜温度と、当該成膜温度で成膜した容量膜の成膜速度との相関データに基づき、膜厚が増大し始める境界温度T(℃)を取得するステップ(S100およびS102)と、(T−20)(℃)以上(T+20)(℃)以下の温度で、成膜ガスを用いた原子層堆積法により容量膜を成膜するステップ(S104〜S112)と、を含む。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。一部の構造及び方法は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。一部の構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得る。  (もっと読む)

(もっと読む)

半導体メモリ装置およびその製造方法

【課題】 耐酸化性能に優れたシリコン窒化膜によってReRAMセルの側壁全面を覆うことによって、製造工程での可変抵抗膜等の酸化を抑制し、ReRAMセルの状態の安定性およびデータ保持性が高い半導体メモリ装置およびその製造方法を提供することを目的とする。

【解決手段】 ReRAMセルは、例えば、導電性材料からなる第1電極11、多結晶シリコンからなるダイオード12、導電性材料からなる第2電極13、遷移金属酸化膜からなる可変抵抗膜14、および導電性材料からなる第3電極15から構成されるものとする。また、ReRAMセルの側壁全面に、シリコン窒化膜を主成分とする側壁絶縁膜20が形成されており、更にその外側にはシリコン酸化膜を主成分とするセル間絶縁膜21が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】プログラム後の誤読み出しを抑制でき、高い信頼性を備える半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板1上のチャンネル領域に形成されたゲート酸化膜3と、前記ゲート酸化膜3上に形成されたゲート電極4と、前記チャンネル領域の少なくとも一部に形成されたシリサイド層2と、を有し、前記シリサイド層2は、前記チャンネル領域のうち前記ゲート電極4の全体を除く領域の少なくとも一部を被覆する。

(もっと読む)

半導体装置の製造方法及び基板処理システム

【課題】TiO2膜とHfO2膜との相互拡散を抑制でき、リーク電流の増加を抑制させる。

【解決手段】基板上に第1の高誘電率絶縁膜を形成する工程と、第1の高誘電率絶縁膜上に絶縁膜を形成する工程と、絶縁膜上に第2の高誘電率絶縁膜を形成する工程と、第1の高誘電率絶縁膜、絶縁膜および第2の高誘電率絶縁膜が形成された基板に対して熱処理を行う工程と、を有し、第1の高誘電率絶縁膜、絶縁膜および第2の高誘電率絶縁膜は、それぞれが異なる物質で構成されると共に、絶縁膜は、酸化アルミニウム膜、窒化アルミニウム膜、または、窒化シリコン膜で構成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】1容量素子当たりの面積を、微細加工に問題を起こすことなく縮小できるようにする容量素子を有するメモリーのような半導体装置を提供する。

【解決手段】酸素バリア膜16、層間絶縁膜17(酸化シリコン膜)上に、薄いエッチングストッパー膜18(窒化シリコン膜)、層間絶縁膜19(酸化シリコン膜)を形成し、酸素バリア膜16の直上にそれより大きい開口部をドライエッチングにより形成する。その後、強誘電体材料を容量絶縁膜とする容量素子の下部電極21を開口部20上を含むように形成する。開口部20を形成するための層間絶縁膜19のエッチングはエッチングストッパー膜18で容易に停止できるので、下地層間絶縁膜17がエッチングされない。こうして酸素バリア膜16を縮小し、容量素子占有面積を小さくできる。

(もっと読む)

半導体装置の製造方法、基板処理方法および基板処理装置

【課題】 膜中の炭素、水素、窒素、塩素等の不純物濃度が極めて低い絶縁膜を低温で形成する。

【解決手段】 基板を収容した処理容器内に所定元素を含む原料ガスを供給することで、基板上に所定元素含有層を形成する工程と、処理容器内に窒素を含むガスを活性化して供給することで、所定元素含有層を窒化層に変化させる工程と、大気圧よりも低い圧力に設定された処理容器内に酸素を含むガスと水素を含むガスとを活性化して供給することで、窒化層を酸化層または酸窒化層に変化させる工程と、を1サイクルとして、このサイクルを複数回繰り返すことで、基板上に所定膜厚の酸化膜または酸窒化膜を形成する工程を有する。

(もっと読む)

強誘電体記憶装置

【課題】強誘電体キャパシタの上部電極上にコンタクトプラグを容易に形成することができ、かつ、強誘電体キャパシタ上方の水素バリア膜の破損を抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板10上に設けられた複数のトランジスタと、複数のトランジスタ上に設けられた第1の層間絶縁膜ILD1と、第1の層間絶縁膜ILD1上に設けられた複数の強誘電体キャパシタCと、複数の強誘電体キャパシタCの上面および側面を被覆する第1の水素バリア膜HB1と、強誘電体キャパシタCの上方に設けられ、並びに、隣接する2つの強誘電体キャパシタC間に間隙または空孔Hを有する状態で埋め込まれた第2の層間絶縁膜ILD2と、間隙または空孔Hの開口部を閉じるように第2の層間絶縁膜ILD2上を被覆するカバー絶縁膜CIと、カバー絶縁膜CI上を被覆する第2の水素バリア膜HB2とを備える。

(もっと読む)

半導体装置

【課題】MONOS型不揮発性メモリの信頼性を向上させる。

【解決手段】メモリセルは、選択ゲート6とその一方の側面に配置されたメモリゲート8とを有している。メモリゲート8は、一部が選択ゲート6の一方の側面に形成され、他部がメモリゲート8の下部に形成されたONO膜7を介して選択ゲート6およびp型ウエル2と電気的に分離されている。選択ゲート6の側面にはサイドウォール状の酸化シリコン膜12が形成されており、メモリゲートの側面にはサイドウォール状の酸化シリコン膜9と酸化シリコン膜12とが形成されている。メモリゲート8の下部に形成されたONO膜7は、酸化シリコン膜9の下部で終端し、酸化シリコン膜12の堆積時にメモリゲート8の端部近傍の酸化シリコン膜12中に低破壊耐圧領域が生じるのを防いでいる。

(もっと読む)

221 - 240 / 686

[ Back to top ]