Fターム[5F083GA25]の内容

Fターム[5F083GA25]に分類される特許

21 - 40 / 686

半導体装置の製造方法

【課題】第1の領域において、第2の絶縁膜からゲート絶縁膜への酸化剤の侵入を防止する。第2の領域において、複数の第1の配線間に設けられた第2の絶縁膜を第1の絶縁膜に対して選択的に除去する。

【解決手段】半導体装置の製造方法では、基板の第1の領域には第1の積層体を形成し第2の領域には複数の第1の配線を形成する。第1の絶縁膜をマスクとして、第1の領域の主面に第1の不純物のイオン注入を施す。第1の積層体の側壁を覆いかつ複数の第1の配線間を埋設するように第2の絶縁膜を形成する。第2の絶縁膜をマスクとして、第1の領域の主面に第2の不純物のイオン注入を施す。第1のエッチングにより、第2の絶縁膜を第1の絶縁膜に対して選択的に除去した後、基板に熱処理を行う。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層の溝に埋め込まれた電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設ける。チャネル形成領域は、サイドウォールを側壁に有するゲート電極層と重なる位置に形成される。溝は、深い領域と浅い領域を有し、サイドウォールは、浅い領域と重なり、配線との接続は、深い領域と重なる。

(もっと読む)

Ru含有酸素拡散バリア

【課題】メモリデバイス中の酸素拡散バリアとしてRuおよび/またはRuO2を選択的に形成する方法と、そのようなRu系拡散バリアを有するメモリデバイスを提供する。

【解決手段】MIMキャパシタ構造を形成する方法は、導電性の下部電極プラグ33を露出させるリセスを備えたベース構造を得る工程と、ベース構造材料に比較した下部電極プラグ上へのRu成長の培養時間の違いに基づいて、下部電極プラグ上にRu50を選択成長させる工程と、選択成長したRu50を酸化する工程と、酸化したRu50の上にRu含有下部電極60を堆積する工程と、Ru含有下部電極60の上に誘電体層70を形成する工程と、誘電体層70の上に導電性の上部電極71を形成する工程とを含む。

(もっと読む)

記憶装置及びその製造方法

【課題】信頼性が高い記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る記憶装置は、下部電極層と、前記下部電極層上に設けられた絶縁性の芯材層と、前記芯材層上に設けられ、前記芯材層の側面上には設けられていない上部電極層と、前記芯材層の側面上に設けられ、前記下部電極層及び前記上部電極層に接し、複数の微小導電体が隙間を介して集合した抵抗変化層と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】放射線耐性能力をさらに向上することができる半導体装置を提供する。

【解決手段】半導体基板1の上方に形成された第1絶縁膜12と、第1絶縁膜12の上方に形成され、下部電極17と上部電極19に挟まれる強誘電体膜18を有するキャパシタQと、キャパシタの上に形成される第2絶縁膜26と、を有し、第1絶縁膜12と下部電極17の間に、Pb又はBiが添加された結晶を持つ絶縁材料膜から形成される第3絶縁膜16、38と、

を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】記憶素子の実効面積の減少を抑制する半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法は、基板上に第1導電プラグを形成する工程と、基板上に第1導電プラグの上面を覆う可変抵抗膜を形成する工程と、基板上に第1導電プラグの上面を覆う第1絶縁膜を形成する工程と、第1絶縁膜のうち第1導電プラグ上の部分を除去して、第1絶縁膜に孔部を形成する工程と、第1絶縁膜の上面から孔部内にわたって第1導電膜を形成して孔部内を埋め込むことで、孔部内で可変抵抗膜に接触し、かつ、可変抵抗膜を介して第1導電プラグに電気的に接続するように第1導電膜を形成する工程と、を含む。

(もっと読む)

半導体装置

【課題】良好な電気特性を維持しつつ、微細化を達成した半導体装置を提供する。また、信頼性の高い半導体装置を提供する。

【解決手段】ゲート電極層をマスクとした不純物の導入処理によって自己整合的にチャネル形成領域と一対の低抵抗領域とが形成される酸化物半導体層を有し、ゲート電極層を挟んで設けられる一対の配線層が低抵抗領域と電気的に接続し、配線層が形成される領域の下部に低抵抗領域と接する電極層が設けられている半導体装置である。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタ、ダイオード等の半導体用途に好適な材料を提供する。

【解決手段】ジルコニウムを含ませた酸化物半導体材料は結晶化しやすい材料とすることができ、成膜直後において、結晶構造を有する酸化物半導体膜を形成することができる。従って、酸化物半導体膜の成膜後の加熱処理を省略することができるため、量産に適したプロセスである。具体的には、少なくともインジウムと亜鉛を含む酸化物半導体材料に、4族元素の一つであるジルコニウムを含ませる。少なくともインジウムと亜鉛を含む酸化物半導体材料にジルコニウムを含ませた酸化物半導体材料膜(InZrZnOX膜)を提供する。

(もっと読む)

半導体装置

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。また信頼性の高い半導体装置を提供する。

【解決手段】チャネル形成領域と、ソース領域またはドレイン領域を有する島状半導体膜131と、ゲート絶縁膜と、ゲート電極103とを有する薄膜トランジスタと、層間絶縁膜と、層間絶縁膜中に形成され、ソース領域またはドレイン領域の一方に達する複数のコンタクトホールを含む第1のコンタクトホール142と、ソース領域またはドレイン領域の他方に達する第2のコンタクトホール141とを有し、第2のコンタクトホール141の径は、第1のコンタクトホール142に含まれる複数のコンタクトホール142のそれぞれの径より大きく、第1のコンタクトホールの底面積の合計と、第2のコンタクトホール141の底面積は等しい半導体装置に関する。

(もっと読む)

半導体装置

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ワード線抵抗を低減し、かつ、周辺回路のトランジスタの特性変化を抑制することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、複数のメモリセルと、周辺回路とを備える。メモリセルは、半導体基板の上方に設けられたフローティングゲートと、フローティングゲート上に設けられたゲート間絶縁膜と、ゲート間絶縁膜上に設けられたコントロールゲートとを含む。周辺回路は、互いに電気的に接続されたフローティングゲートおよびコントロールゲートと、少なくともフローティングゲートとコントロールゲートとの間の電気的接触部分に設けられ該フローティングゲートと該コントロールゲートとの間の電気的接続を妨げない絶縁薄膜とを含むトランジスタを含む。複数のメモリセルは、コントロールゲート内に絶縁薄膜を含まない。メモリセルおよび周辺回路において、コントロールゲートの少なくとも上部はシリサイド化されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】エッチング加工がし易く、データ保持の劣化を抑制する。

【解決手段】実施形態の不揮発性半導体記憶装置は、下地層と、前記下地層の上に設けられた積層体であって、それぞれ交互に積層された複数の電極層と複数の絶縁層と、前記複数の電極層と前記複数の絶縁層との間に設けられた拡散抑制層と、を有する前記積層体と、前記積層体を積層方向に貫通するホールの側壁に設けられたメモリ膜と、前記メモリ膜の内側に設けられたチャネルボディ層と、を備える。前記複数の電極層のそれぞれは、第1の不純物元素を含む第1の半導体層である。前記拡散抑制層は、前記第1の不純物元素とは異なる第2の不純物元素を含む第2の半導体層である。前記拡散抑制層は、前記第1の不純物元素の拡散を抑制する効果を有する膜である。

(もっと読む)

不揮発性半導体記憶装置

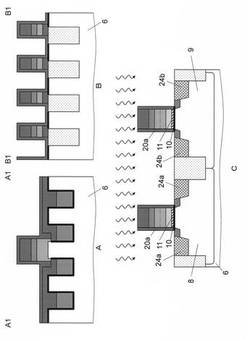

【課題】隣接する配線の間におけるリークを抑制することができる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1は、シリコンを含む基板11と、基板11の上に設けられた複数のメモリセルと、複数のメモリセルの上方に設けられた配線7と、配線7の上に設けられたリーク抑制層8と、前記リーク抑制層8の上方に設けられた層間絶縁膜10と、を備えている。そして、隣接するメモリセルの間、および、隣接する配線7の間には空隙12が形成され、リーク抑制層8の幅寸法は、配線7の幅寸法よりも短いこと、および、隣接するリーク抑制層8の間の寸法は、隣接する配線7の間の寸法よりも長いこと、の少なくともいずれかである。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】不純物添加シリコン層に添加された不純物が不純物無添加シリコン層に拡散するのを抑制する。

【解決手段】セレクトゲート電極SG1上にはワード線WL1が積層され、最上層のワード線WL1上にはセレクトゲート電極SG2がロウごとに形成されることで、NANDセルNC1が構成され、セレクトゲート電極SG1、SG2およびワード線WL1は、不純物添加シリコン層2と層間絶縁膜とを拡散防止層3を介して交互に積層することで構成し、ワード線WL1は、拡散防止層3にて挟まれた不純物添加シリコン層2にて構成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】高電界リークを低減して、書き込み特性を向上させる。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板における素子分離絶縁膜により区画された活性領域上にゲート絶縁膜を介して形成された電荷蓄積層と、前記素子分離絶縁膜の上面、前記電荷蓄積層の側面及び前記電荷蓄積層の上面に形成された電極間絶縁膜と、前記電極間絶縁膜上に形成された制御電極層とを備える。そして、前記電極間絶縁膜は、シリコン窒化膜もしくは高誘電率膜を2層のシリコン酸化膜で挟んだ積層構造または高誘電率膜とシリコン酸化膜の積層構造及び前記積層構造と前記制御電極層の間に形成された第2のシリコン窒化膜を有し、前記第2のシリコン窒化膜のうちの前記電荷蓄積層の上面上の部分を消失させた。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】チャネル領域にシリコンを含まない材料を用いる半導体装置であって、微細化に伴いゲート絶縁層が薄膜化されても、ゲートリーク電流が抑制された半導体装置を提供する。

【解決手段】ゲート絶縁層として熱酸化シリコン層を用いる。熱酸化シリコン層を用いることで、CVD法やスパッタリング法で形成された酸化シリコン層を用いる場合よりゲートリーク電流を抑制することができる。ゲート絶縁層に熱酸化シリコン層を用いるために、チャネル領域を含む半導体層を形成する基板とは別にシリコン基板を用意し、シリコン基板上に熱酸化シリコン層を形成する。そして熱酸化シリコン層を、チャネル領域を含む半導体層に貼り合わる。このようにして、半導体層の上に熱酸化シリコン層を形成し、熱酸化シリコン層をゲート絶縁層として用いたトランジスタを形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】隣接セルの書き込み閾値の変動を抑制すると共に、制御ゲート電極膜とシリコン基板との間のリーク電流を低減して消去特性を向上させる。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板における素子分離絶縁膜により区画された活性領域上にゲート絶縁膜を介して形成された電荷蓄積層と、前記素子分離絶縁膜の上面、前記電荷蓄積層の側面及び前記電荷蓄積層の上面に形成された電極間絶縁膜と、前記電極間絶縁膜上に形成された制御電極層とを備える。前記電極間絶縁膜は、第1のシリコン酸化膜、第1のシリコン窒化膜、第2のシリコン酸化膜および第2のシリコン窒化膜を積層形成した積層構造を有する。そして、前記電極間絶縁膜は、前記第2のシリコン酸化膜のうちの前記素子分離絶縁膜の上面上の部分の膜厚が前記電荷蓄積層の上面上の部分の膜厚より薄くなるように構成した。

(もっと読む)

SOI基板の作製方法

【課題】表面のP−V値が小さく、かつ、高い結晶性を有する半導体薄膜層を備えたSOI基板の作製方法を提供する。

【解決手段】半導体薄膜層の結晶性を高く保つため、水素イオン添加処理中の半導体基板の温度を200℃以下に抑制した。加えて、水素イオン添加処理後の半導体基板を100℃以上400℃以下に保持した状態で半導体基板に対してプラズマ処理を行うことにより、水素イオン添加処理により生じる、半導体薄膜層の分離に対して寄与度の高いSi−H結合を残存させたまま、半導体薄膜層の分離に対して寄与度の低いSi−H結合を低減した。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離絶縁膜の形成時に、浮遊ゲート電極膜の基板に対面する部分の幅寸法が細くなってしまうことを防止する。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成され、浮遊ゲート電極膜、電極間絶縁膜および制御ゲート電極膜が積層されたゲート電極とを備えた。そして、前記浮遊ゲート電極膜を、窒素を含む下層シリコン層と窒素を実質的に含まない上層シリコン層とを有する多結晶シリコン層で構成し、前記下層シリコン層のゲート幅方向の寸法を、前記上層シリコン層のゲート幅方向の寸法よりも大きく構成した。

(もっと読む)

21 - 40 / 686

[ Back to top ]