Fターム[5F083GA25]の内容

Fターム[5F083GA25]に分類される特許

241 - 260 / 686

半導体装置の製造方法

【課題】製造工程における強誘電体キャパシタの劣化を抑制する。

【解決手段】半導体装置の製造方法は、半導体基板100の上方に、Pbを含む強誘電体120を有するキャパシタ層を形成し、前記キャパシタ層をRIEにより加工して、前記強誘電体を有するキャパシタを形成し、Pb、酸素および鉛単体酸化物を含む雰囲気で、前記キャパシタを熱処理し、前記熱処理の際に、前記雰囲気内における前記鉛単体酸化物の分圧は、前記強誘電体内におけるPbにより生じる前記鉛単体酸化物の蒸気圧以上、かつ前記雰囲気内における前記鉛単体酸化物の蒸気圧以下である。

(もっと読む)

半導体基板、半導体装置及び半導体装置の製造方法

【課題】半導体層の界面に生じるダングリングボンドをフッ素で終端することで、界面準位を低減することができ、また、低熱履歴のプロセスでも活性領域のみへ効率よくフッ素を導入することができる半導体基板を提供する。

【解決手段】フッ素拡散防止膜6と該フッ素拡散防止膜6上に形成されたフッ素を含有するシリコン酸化膜7からなる絶縁層9と、前記絶縁層9上に形成された半導体層8と、を含み、前記半導体層8とフッ素を含有する前記シリコン酸化膜7とが接触していることを特徴とする。

(もっと読む)

抵抗変化メモリ

【課題】可変抵抗素子の抵抗値ばらつきに起因する誤動作を抑制する抵抗変化メモリを提供する。

【解決手段】抵抗変化メモリは、第1の電極14、抵抗変化膜15、及び第2の電極16が積層された積層構造からなり、かつ記憶データに基づいて低抵抗状態又は高抵抗状態を取り得る可変抵抗素子17と、可変抵抗素子17の側面に設けられた絶縁膜19と、絶縁膜19の側面に設けられた導電膜からなり、かつ可変抵抗素子17に並列接続された固定抵抗素子20とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中に含まれる不純物の拡散を防止することができ、さらに、ゲート絶縁膜の信頼性及びホットキャリア耐性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】N型シリコン基板1上にゲート酸化膜36およびP+型ゲート電極35を形成する。P+型ゲート電極35の両側にソース/ドレイン領域6を形成する。ゲート酸化膜36およびP+型ゲート電極35中には窒素がドープされ、窒素ドーピング領域30が形成される。

(もっと読む)

強誘電体キャパシタ、半導体装置、強誘電体キャパシタの製造方法

【課題】良好な特性の強誘電体キャパシタを提供する。

【解決手段】本発明の強誘電体キャパシタは、基板10の上に設けられた下部電極31と、下部電極31の上に設けられた上部電極33と、下部電極31と上部電極33との間に設けられた強誘電体膜32と、下部電極31と強誘電体膜32と上部電極33とを含んだ電荷蓄積部3の上に設けられ、アルミニウム酸化物を含んだ水素バリア膜37と、水素バリア膜37と電荷蓄積部3との間に設けられ、イリジウム酸化物からなる拡散防止膜36と、拡散防止膜36と電荷蓄積部3との間に設けられた絶縁膜35と、を備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極から電荷蓄積層に電荷を注入する不揮発性メモリにおいて、従来のゲート構造に比べて電荷の注入効率、電荷保持特性および信頼性を共に向上させる。

【解決手段】電荷蓄積層を構成する窒化シリコン膜に電子および正孔を注入し、トータルの電荷量を変えることによって書き込み・消去を行う不揮発性メモリにおいて、ゲート電極からの電荷注入を高効率で行うために、メモリセルのゲート電極を、ノンドープのポリシリコン層54とメタル材料電極層59の2層膜で構成する。

(もっと読む)

デバイスの製造方法及びデバイス

【課題】メモリ機能等を有する機能膜の水による劣化を防止すること。

【解決手段】成膜装置内で、機能膜が形成された基板上に、上記機能膜を覆うように、絶縁膜を形成する絶縁膜形成工程と、形成した上記絶縁膜の表面をプラズマに曝すプラズマ処理工程とを繰り返すこと。

(もっと読む)

半導体記憶装置

【課題】静電容量の大きなキャパシタを備え、低コストで製造が可能な、高集積化された半導体記憶装置を提供する。

【解決手段】半導体基板上にY方向に延在しY方向と垂直なX方向に互いに平行に配列されたワード線と、Y方向に互いに平行に配列され二つのワード線と交差する帯状の活性領域と、各活性領域上のその長手方向の両端部にそれぞれ接続する容量コンタクトプラグと、容量コンタクトプラグ上の第1下部電極と第1下部電極上の第2下部電極を含むスタック下部電極と、容量絶縁膜と、上部電極とを有し、第2下部電極の中心位置が第1下部電極の中心位置から所定の方向へシフトしている、半導体記憶装置。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】強誘電体キャパシタを高信頼性化する。

【解決手段】半導体記憶装置70に設けられる強誘電体キャパシタ50は、積層形成される下部電極膜14、強誘電体膜15、及び上部電極膜16から構成される。下部電極膜14は、メモリセルトランジスタ40のソース及びドレインの一方の上部に設けられるコンタクトプラグ11と電気的に接続される部分が下に凸となりコンタクトプラグ上部に埋め込まれる形状を有し、反応防止膜13を介してコンタクトプラグ11に接続される。上部電極膜16は、コンタクトプラグ23を介して配線層25に接続される。コンタクトプラグ11及び反応防止膜13が接続される界面の両端部とコンタクトプラグ11の上側面とは反応防止膜9で覆われる。強誘電体キャパシタ50は、コンタクトプラグ11及び23を除く領域が反応防止膜9と反応防止膜9と接する反応防止膜19により覆われる。

(もっと読む)

半導体装置の製造方法

【課題】CMP法によって層間絶縁膜を平坦化するときに、ダミーゲート電極の上端部の絶縁膜が消失するのを防ぐと共に、セルゲート電極の上端部の絶縁膜が取り除かれ過ぎるのを防ぐ半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、上面にSW窒化膜15が形成されたダミーゲート電極6の、半導体基板3の表面からの高さが、セルゲート電極5及び周辺ゲート電極7よりも高くされた状態で、CMP法によってBPSG膜21を平坦化し、セルゲート電極5、ダミーゲート電極6、及び周辺ゲート電極7の各マスク窒化膜13をそれぞれ露出させる工程を有する。

(もっと読む)

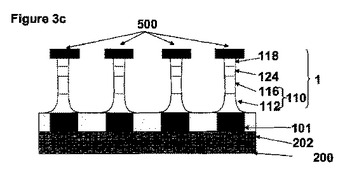

丸いコーナーを有する複数の柱を備えるクロスポイント形不揮発性メモリ装置およびその製造方法

不揮発性メモリ装置が複数の柱(1)を備え、複数の柱のそれぞれは、ステアリング素子(110)および記憶素子(118)を含む不揮発性メモリセルを備え、複数の柱のそれぞれのトップコーナーまたはボトムコーナーの少なくとも一方が丸くされる。不揮発性メモリ装置を製作する方法が、装置層のスタックを形成すること、およびこのスタックをパターン形成して複数の柱を形成することを含み、複数の柱のそれぞれは、ステアリング素子および記憶素子を含む不揮発性メモリセルを備え、複数の柱のそれぞれのトップコーナーまたはボトムコーナーの少なくとも一方が丸くされる。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】動作信頼性を向上させる不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】基板100上に形成された蓄積層105と蓄積層上に形成された制御ゲート電極107を備えた第1電極MTと、基板100上に形成された第2電極ST2及び第3電極ST2と、ゲート長方向に沿って対向する第2電極と第3電極ST2との側壁及び基板100上に形成された第2絶縁膜112と、第2、第3ゲート電極ST2間に埋設された第1絶縁膜113と、第2電極ST2及び第1電極MT間に埋設された第2絶縁膜109、110と、第1ゲート電極MT、第2ゲート電極ST2、第3ゲート電極ST2、及び第1、第2絶縁膜上113、112にそれぞれ形成され、且つ第1絶縁膜113における水素原子の拡散を防止する第3絶縁膜114とを具備する。

(もっと読む)

封入相変化セル構造および方法

相変化セル構造に関する方法およびデバイスを本明細書に記述する。1つまたは複数の実施形態において、相変化セル構造を形成する方法は、底部電極を含む、基板突起を形成することと、相変化材料を該基板突起の上に形成することと、導電材料を該相変化材料の上に形成することと、該導電材料の一部分および該相変化材料の一部分を除去して、封入スタック構造を形成することとを含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】多段キャパシタの形成およびキャパシタシリンダを支えるサポート絶縁膜の周辺回路領域における除去を工程数を増大させることなく達成する、キャパシタシリンダが多段に積層されたキャパシタを有する半導体装置の製造方法を提供する。

【解決手段】容量絶縁膜および上部電極の形成工程をそれぞれ1回の成膜工程で行うと共に、周辺回路領域のスルーホールエッチングや水素アニールの妨害となるサポート絶縁膜について、周辺回路領域の残すべき層間絶縁膜の最上層のみ、容量絶縁膜および上部電極形成時に一括して除去し、それより下層の周辺回路領域のサポート絶縁膜がある場合は、メモリセル領域のコア絶縁膜除去のための開口形成と同時に除去する。

(もっと読む)

抵抗変化メモリ

【課題】p-i-nダイオードをその特性の劣化なしに薄くする。

【解決手段】本発明の例に係わる抵抗変化メモリは、第一方向に延びる第一導電線L2(i)と、第一方向に交差する第二方向に延びる第二導電線L3(j)と、第一導電線と第二導電線との間に直列接続されるメモリ素子17及び整流素子13,14,15から構成されるセルユニットCU2とを備える。メモリ素子の抵抗値は、メモリ素子に印加される電圧を制御することにより、少なくとも第一値と第二値との間で可逆変化させる。整流素子は、p型半導体層、n型半導体層及びこれらの間の真性半導体層から構成されるp-i-nダイオードである。p-i-nダイオードは、少なくともp型半導体層の真性半導体層側の端部及びn型半導体層の真性半導体層側の端部に拡散防止領域を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁耐圧を向上し、接続プラグのリセスをなくすための高度な平坦化を不要にし、メモリの高集積化も可能にした、半導体装置及びその製造方法を提供する。

【解決手段】基板2と、駆動素子3と、駆動素子3に電気的に接続する第1プラグ8と、基板2の上方に形成されて、電極本体部14aの外側に延在してなる電極延在部14bの底面側で、第1プラグ8に電気的に接続する下部電極14と、下部電極14の電極本体部14a上に形成された強誘電体本体部15a、及び下部電極14の電極延在部14b上に、強誘電体本体部15aより薄厚に形成されてなる強誘電体延在部15b、からなる強誘電体膜15と、強誘電体膜15の強誘電体延在部15b上に形成されることなく、強誘電体本体部15a上に形成された上部電極16と、上部電極16に導通して形成された第2プラグ19と、を含む半導体装置1。

(もっと読む)

密封型半導体記録媒体及び密封型半導体記録装置

【課題】 密封型半導体記録媒体及び密封型半導体記録装置に関し、無線により電力を給電するとともに、相互干渉なしに無線でデータ通信を高速に行うことが可能な密封された高信頼性の半導体メモリを低コストで提供する。

【解決手段】 少なくとも1枚の半導体基板に最大辺が20mm以下のサイズの複数の読出専用メモリブロックを互いに電源配線を共有しない状態で設け、前記各読出専用メモリブロックに電力受給用コイルとデータ通信用コイルを備えるとともに、前記各読出専用メモリブロックに互いに異なったデータを書き込む。

(もっと読む)

不揮発性半導体記憶装置

【課題】デポジッション膜を形成することなく、ゲートとコンタクトのショートを抑制する不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1のコントロールゲート14を、フローティングゲート13側に位置する第1側面と、第1側面の反対に位置する第2側面と、コントロールゲート14の第1側面側の上部に形成されたシリサイド領域22と、コントロールゲート14の第2側面側の上部に形成された突出部8とを含むように構成する。そのサイドウォール絶縁膜21は、シリサイド領域22を覆うことなく突出部8の少なくとも一部を被覆する第1部分と、第1部分から連続的に設けられ、第2側面に接触して第2側面を被覆する第2部分とを含むものとする。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】エッチング処理時に発生した金属元素などによるウエハの裏面の汚染を抑えることができる不揮発性記憶装置の製造方法を提供する。

【解決手段】シリコンウエハ1の上面上に整流層21と抵抗変化層23を形成する層形成工程と、第1の方向に延在する複数の第1の配線11と第1の方向と交差する第2の方向に延在する複数の第2の配線31との各交差位置で整流層21と抵抗変化層23を備えてなる柱状構造のメモリセルが二次元に配列されてメモリセルアレイを形成するように、ドライエッチング法を用いて整流層21と抵抗変化層23のエッチングを行うエッチング工程と、を含み、層形成工程では、シリコンウエハ1の下面と側面が被覆されるようにシリコン膜101をさらに形成し、エッチング工程の後に、シリコンウエハ1の下面と側面に形成されたシリコン膜101を除去するシリコン膜除去工程を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】電極パッドの損傷を抑制することができる半導体装置を提供する。

【解決手段】半導体基板11と、半導体基板11の上方に形成された電極パッド30とを有し、電極パッド30は、第1の融点温度を有する材料からなる第1の層32と、第1の層32上に位置するとともに外に向けて表出し、第1の融点温度よりも高い第2の融点温度を有する材料からなる第2の層33とを含むことを特徴とする。これにより、外部から電極パッド30への圧力により第1の層32に達する傷ができても、必要に応じて第1の融点以上の温度で加熱することにより電極パッド表面の平坦性を修復することができる。

(もっと読む)

241 - 260 / 686

[ Back to top ]