Fターム[5F083JA02]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | 酸化物系 (9,104)

Fターム[5F083JA02]の下位に属するFターム

酸化膜を含む複合膜 (2,564)

酸化窒化膜 (1,013)

タンタル酸化膜(Ta2O5) (705)

ハロゲンを含む酸化膜 (7)

複酸化物 (3,106)

Fターム[5F083JA02]に分類される特許

1,581 - 1,600 / 1,709

半導体記憶装置の設計方法及び製造方法並びに半導体記憶装置

【課題】記憶素子の抵抗値及び抵抗比の製造時及び使用時の影響を考慮した最適な特性を有する半導体記憶装置の設計方法及び製造方法を得る。

【解決手段】ステップS1において電流型センスアンプのセンス時間が決定する。ステップS2において、MR比の変動を重視した第1の用途、RAの変動を重視した第2の用途、MR比及びRA双方の変動を重視する第3の用途のうち、いずれの用途を重視するかを決定する。ステップS3において、ステップS2で決定した重視用途に基づき、MR比,RAとセンス時間の関係を示すセンス時間一定曲線を参考にして、最適MR/RA領域(値)を決定する。ステップS4でTMR面積を入力した後、ステップS5において、ステップS3で決定したMR/RA領域(値)にあるMR比,RAを設定する。

(もっと読む)

半導体装置の製造方法

【課題】 キャパシタ部の形成にあたり写真製版による設計上の制約をなくし、且つキャパシタ部を効率よく使用できる半導体装置の製造方法を提供する。

【解決手段】 シリコン基板1に形成したリセス部14の側面にキャパシタ下層4を有し、リセス部14の底部で隣り合うキャパシタ下層4間を電気的に分離し、酸化膜を介してリセス部14に電極材料を埋め込んでなるキャパシタ部10を有する半導体装置の製造方法において、シリコン基板1にリセス部を形成するステップと、リセス部14の開口及びキャパシタ下層4を形成したい当該リセス部の深さ方向の寸法に基づき決定されたリセス部14の側壁でイオンビームがブロックされてリセス部14の底部にイオンが注入されない照射角度でイオン注入することによりキャパシタ下層4を形成するステップとを備える。

(もっと読む)

記憶素子、メモリ

【課題】 静電破壊を発生することなく情報の記録を行うことができると共に、情報の読み出しの際の出力を充分な大きさで得ることを可能にする記憶素子を提供する。

【解決手段】 情報を磁性体の磁化状態により保持する記憶層13と、磁化固定層11と、その間の非磁性層12とを有し、記憶層13の磁化固定層11とは反対側に、中間層14を介して、それぞれ独立したパターンで形成された、2つのスピン注入層21,22が設けられ、2つのスピン注入層21,22の磁化M21,M22の向きが互いに反対の向きであり、一方のスピン注入層から他方のスピン注入層へ、記憶層13を通じて電流を流すことにより、記憶層13の磁化の向きが変化して、情報の記録が行われる記憶素子10を構成する。

(もっと読む)

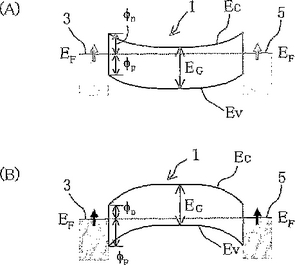

スピン依存伝達特性を有する電界効果トランジスタ及びそれを用いた不揮発性メモリ

ゲート電圧VGSの印加によって、強磁性ソースにおける金属的スピンバンドによるショットキー障壁幅が減少し、この金属的スピンバンドからのアップスピン電子がチャネル領域にトンネル注入される。このとき強磁性ソース3aの半導体的スピンバンドによるエネルギー障壁により非磁性コンタクト3bからダウンスピン電子は注入されない。すなわち、強磁性ソース3aからはチャネル層へアップスピン電子のみが注入される。強磁性ソース3aと強磁性ドレイン5aとが平行磁化の場合では、アップスピン電子は強磁性ドレインの金属的スピンバンドを伝導してドレイン電流となるが、反平行磁化を持つ場合では、アップスピン電子は強磁性ドレイン5aにおける半導体的スピンバンドによる高さΔEcのエネルギー障壁よって強磁性ドレイン5aを伝導することができない。 上記動作原理のMISFETに基づき、高性能・高集積密度の不揮発性メモリを構成することができる。  (もっと読む)

(もっと読む)

磁気抵抗効果素子および磁気メモリ

【課題】 素子の面積を小さくかつ面積のばらつきを小さくすることを可能にする。

【解決手段】 端面を有する第1電極4と、磁化の向きが固着された磁化固着層8a、磁化の向きが可変の磁化自由層8c、および磁化固着層と磁化自由層との間に設けられた非磁性層8bを有し、第1電極の端面に表面が接するように形成された磁気抵抗効果膜8と、磁気抵抗効果膜の第1電極に接する表面と反対側の表面上に形成された第2電極10とを備えている。

(もっと読む)

スケーラブル集積論理および不揮発性メモリ

スケーラブル論理トランジスタはドレインおよびソースのための一組のドープされた領域を有する。ゲート絶縁層は基板上でドレイン領域とソース領域の間に形成される。ゲートスタックは、ポリシリコンや金属のようなゲート層を、二つの窒化金属層の間に置くことで形成される。また、埋め込まれた金属ナノドット層を有する高K誘電率膜を、トンネル絶縁層とゲートスタックとの間に設けるようにして付加することによって、この基本的構成から互換性のある不揮発性メモリトランジスタを形成することもできる。 (もっと読む)

半導体装置及びその製造方法

【課題】 容量絶縁膜が酸化アルミニウムを含むスタック型のキャパシタを備える半導体装置であって、BT試験の際の半導体装置の劣化を抑制し、リーク電流の増大を抑制できる半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置50は、順次に形成された下部電極51、容量絶縁膜52、及び上部電極35を有する。下部電極51及び上部電極35が、窒化チタンで構成され、容量絶縁膜52が、下部電極51に接する膜厚が5nmの酸化アルミニウム膜で構成される。

(もっと読む)

ストレージキャパシタの製造方法及びストレージキャパシタ

【課題】生産収率を増大できるストレージキャパシタの製造方法及びストレージキャパシタを提供する。

【解決手段】製造方法は、半導体基板100上で層間絶縁膜112にコンタクトプラグ114を形成する段階と、食刻停止膜115及び鋳型酸化膜を所定厚さで積層する段階と、コンタクトプラグ114上の鋳型酸化膜及び食刻停止膜115を選択的に除去してトレンチを形成する段階と、全面にチタニウム膜123を形成し、チタニウム膜123上にチタニウム窒化膜124とチタニウム酸窒化膜125を積層してストレージ電極119を形成する段階と、全面に犠牲酸化膜126を形成し、前記鋳型酸化膜が露出されるように前記半導体基板100を平坦化して前記ストレージ電極119のノードを分離する段階と、前記犠牲酸化膜126及び鋳型酸化膜を除去する段階と、ストレージ電極119上にそれぞれ所定厚さの誘電膜及びプレート電極を形成する段階と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 スクラッチ又はクラックなどにより、キャパシタを構成する誘電体膜が水素劣化することを防止する。

【解決手段】 第1の層間絶縁膜(107)と、第1の層間絶縁膜(107)上に形成された絶縁性水素バリア膜(108)と、絶縁性水素バリア膜(108)上に形成された第2の層間絶縁膜(109)と、第1の層間絶縁膜(107)、絶縁性水素バリア膜(108)及び第2の層間絶縁膜(109)よりなる積層膜を貫通するコンタクトプラグ(111,112)と、第2の層間絶縁膜(109)上に形成され、コンタクトプラグ(111,112)と接続するキャパシタ(116)とを備える。そして、コンタクトプラグ(111,112)は、下から順に積層された導電層(111)及び導電性水素バリア膜(112)よりなり、導電層(111)の上面は、絶縁性水素バリア膜(108)の上面よりも下に位置している。

(もっと読む)

半導体集積回路装置の製造方法

【課題】DRAMの容量素子の下部電極上に形成した誘電体膜を酸素雰囲気中で熱処理する際、下部電極を透過した酸素がバリア層を酸化して、高抵抗、低誘電率の酸化物層を形成する不具合を防止する。

【解決手段】溝27を形成した後、溝27から露出するプラグ22の表面にRuシリサイド層25を形成し、そのRuシリサイド層25の表面にRuシリコンナイトライド層26を形成する。続いて、溝27の内部に下部電極28を形成した後、その上部に誘電体膜29を形成し、酸素を含む雰囲気中で誘電体膜29を熱処理する。その後、誘電体膜29の上に上部電極30を形成する。これにより、誘電体膜29を形成する工程で行われる酸素雰囲気中での高温熱処理の際に、Ruシリコンナイトライド層26が犠牲的に酸化されてRuシリコンオキシナイトライドとなり、Ruシリサイド層25の酸化の進行を防止できる。

(もっと読む)

半導体装置及びその製造方法

【課題】複雑な工程を追加することなく下部電極表面に凹凸を形成することにより、限られたセル面積の中で十分な容量を確保することができるMIM構造のキャパシタを提供する。

【解決手段】本発明の半導体装置の製造方法では、第2のホール15の表面に、キャパシタの下部電極となる窒化チタン膜16aを形成する。窒化チタン膜16aの形成は、化学気相成長法と、アンモニア雰囲気下でのアニールとを16回繰り返すことにより行う。この化学気相成長法を、低温、高圧力、原料ガスであるアンモニアに対する四塩化チタンの流量比を従来よりも高くした条件で行うことにより、窒化チタン膜16aの表面の凹凸を高くすることができる。一方、アンモニア雰囲気下でのアニールを行うことにより、窒化チタン膜16aが低抵抗化される。

(もっと読む)

強誘電体メモリ及びその製造方法

【課題】 強誘電体キャパシタの特性の劣化を防止するとともに、微細化及び多層化を実現可能な製造方法の提供。

【解決手段】 強誘電体メモリの製造方法は、(a)基体10の上方に形成された第1の絶縁層20に、第1及び第2のコンタクト部50,52を形成すること、(b)下部電極72、強誘電体層74及び上部電極76が順に積層された積層体70を形成すること、(c)積層体70の上方に導電性のハードマスクM1を形成し、積層体70のうちハードマスクM1から露出する領域をエッチングすることにより、第1のコンタクト部50の上方に強誘電体キャパシタ80を形成すること、(d)第1の絶縁層20の上方に、ハードマスクM1、強誘電体キャパシタ80及び第2のコンタクト部52を被覆する第2の絶縁層100を形成すること、(e)第2の絶縁層100に第2のコンタクト部52を露出するコンタクトホール102を形成すること、を含む。

(もっと読む)

強誘電体メモリ及びその製造方法

【課題】強誘電体キャパシタの特性の劣化を防止するとともに、微細化及び多層化を実現可能な強誘電体メモリ及びその製造方法を提供する。

【解決手段】(a)基体10の上方に形成された第1の絶縁層20に、第1及び第2のコンタクト部50,52を形成すること、(b)下部電極72、強誘電体層74及び上部電極76が順に積層された積層体70を形成すること、(c)積層体70をパターニングすることにより、第1のコンタクト部50の上方に強誘電体キャパシタ80を形成すること、(d)第1の絶縁層20の上方に、強誘電体キャパシタ80及び第2のコンタクト部52を被覆する第2の絶縁層100を形成すること、(e)第2の絶縁層100に第2のコンタクト部52を露出するコンタクトホール102を形成すること、(f)第3のコンタクト部130を形成するために、コンタクトホール102を含む領域に導電層110を設けること、を含む。

(もっと読む)

ジルコニウム酸化膜を有する半導体素子のキャパシタ及びその製造方法

【課題】70nm以下の金属配線を有する次世代DRAMで要求される容量、良好な漏れ電流特性を確保できるキャパシタ及びその製造方法を提供すること。

【解決手段】ストレージ電極15及びプレート電極17間のキャパシタの誘電膜16として、Al2O3/ZrO2、ZrO2/Al2O3、(ZrO2/Al2O3)n(2≦n≦10)、(Al2O3/ZrO2)n(2≦n≦10)、ZrO2/Al2O3/ZrO2の3重膜構造、窒化されたZrO2薄膜の単一膜、窒化Al2O3薄膜と窒化されたZrO2薄膜との2重膜、Al2O3薄膜と窒化されたZrO2薄膜との2重膜、又は、ZrO2薄膜、Al2O3薄膜及び窒化されたZrO2薄膜の3重膜を採用し、また、バンドギャップエネルギーの大きいZrO2(Eg=7.8eV、ε=20〜25)薄膜及び熱安定性に優れたAl2O3(Eg=8.7eV、ε=9)薄膜からなる多重誘電膜構造を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、2つのゲート電極部間に設けられるSAC構造のCBを有するDRAMにおいて、少なくともゲート電極部のCB側のエッヂにそれぞれ対応する半導体基板の表面部に拡散防止層を的確に形成できるようにする。

【解決手段】たとえば、リソグラフィ工程およびドライエッチングにより、ゲート電極部17,17の相互間に、CBを形成するためのコンタクト孔25aを開孔した後、さらに第2の層間膜35をプルバックにより除去する。そして、コンタクト孔25a内に露出する第1の側壁絶縁膜を剥離した状態で、第2の層間膜35をマスクに、CBハロー・I/Iにより、拡散層23aの拡散を防止するためのp導電型の拡散防止層31を形成する構成となっている。

(もっと読む)

強誘電体メモリ及びその製造方法

【課題】 強誘電体キャパシタの特性の劣化を防止するとともに、微細化及び多層化を実現することにある。

【解決手段】 強誘電体メモリの製造方法は、(a)基体10の上方に形成された第1の絶縁層20に、第1及び第2のコンタクト部50,52を形成すること、(b)下部電極、強誘電体層及び上部電極が順に積層された積層体を形成すること、(c)積層体の上方に導電性のハードマスクMを形成し、積層体のうちハードマスクMから露出する領域をエッチングすることにより、第1のコンタクト部50の上方に強誘電体キャパシタ80を形成すること、(d)第1の絶縁層20の上方に、ハードマスクM、強誘電体キャパシタ80及び第2のコンタクト部52を被覆する第2の絶縁層100を形成すること、(e)第2の絶縁層100に第2のコンタクト部52を露出するコンタクトホール102を形成すること、を含む。

(もっと読む)

フラッシュメモリ素子の製造方法及びそれによって製造されたフラッシュメモリ素子

【課題】フラッシュメモリ素子の製造方法及びそれによって製造されたフラッシュメモリ素子を提供する。

【解決手段】本発明のフラッシュメモリ素子の製造方法は、一実施形態で、半導体基板内に素子分離膜を形成して複数の平行な活性領域を限定することを具備する。前記活性領域上に前記活性領域の長さ方向に沿って互いに離隔された複数の第1導電膜パターンを形成する。前記第1導電膜パターンを有する半導体基板上にコンフォーマルな絶縁膜を形成する。前記絶縁膜上に第2導電膜を形成する。前記絶縁膜が露出するように前記第2導電膜をパターニングして前記第1導電膜パターンと重畳されるように前記活性領域及び素子分離膜を横切る複数の平行な第2導電膜パターンを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 高誘電体絶縁膜を使用し、キャパシタ電極中の空乏層の形成を抑制したトレンチ型キャパシタを有する半導体記憶装置及びその製造方法を提供することである。

【解決手段】 上記課題を解決した半導体記憶装置は、半導体基板中に形成されたトレンチと、前記トレンチ内壁に形成された高誘電体絶縁膜と、前記高誘電体絶縁膜に接する半導体基板中に形成され、導電性を与える不純物を含む第1の電極と、前記トレンチの内部を埋めて形成され、前記第1の電極と同一の不純物を少なくとも同等濃度に含む第2の電極と、前記第1の電極、高誘電体絶縁膜、及び第2の電極とを含み、動作時の空乏化率が0.9以上であるトレンチ型キャパシタとを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置が微細化しても細線効果による性能低下を抑制できる、高集積化に適した新たな3次元半導体装置及びその製造方法を提供することである。

【解決手段】 上記課題を解決した半導体装置は、半導体層中にこの半導体層表面に垂直に形成されたトレンチと、前記トレンチの側面及び底面の前記半導体層中に形成され、前記トレンチの深さ方向に形成された複数の素子分離と、前記トレンチの側面に沿って形成され、絶縁膜と電極とを備えた複数の機能素子と、前記電極に接続し、前記複数の機能素子を第1の方向に接続する第1の配線と、前記トレンチの側面及び底面の前記半導体層中に形成され、前記素子分離により分離され、前記機能素子を前記第1の方向は異なる第2の方向に電気的に接続する第2の配線とを具備する。

(もっと読む)

半導体装置

【課題】 ソース又はドレイン用の拡散層の深さが深くなることを防止することが可能な半導体装置を提供する。

【解決手段】 ソース又はドレイン用の拡散層28が形成された素子領域とキャパシタ用のトレンチとを有する半導体基板11と、トレンチの内面に形成されたキャパシタ誘電体膜21と、キャパシタ誘電体膜が形成されたトレンチ内に形成され、その上面が拡散層の上面よりも高く位置する蓄積電極22と、蓄積電極と拡散層とを接続するものであって、蓄積電極の上面及び拡散層の上面に接した導電性接続部32とを備える。

(もっと読む)

1,581 - 1,600 / 1,709

[ Back to top ]