Fターム[5F083JA02]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | 酸化物系 (9,104)

Fターム[5F083JA02]の下位に属するFターム

酸化膜を含む複合膜 (2,564)

酸化窒化膜 (1,013)

タンタル酸化膜(Ta2O5) (705)

ハロゲンを含む酸化膜 (7)

複酸化物 (3,106)

Fターム[5F083JA02]に分類される特許

1,661 - 1,680 / 1,709

高誘電率膜の処理装置および処理方法

【課題】効率の良い高誘電率膜の処理装置および処理方法を提供する。

【解決手段】

CVD(Chemical Vapor Deposition)処理、有機CVD処理あるいはMO−CVD(Metal Organic Chemical Vapor Deposition)処理などの高誘電率膜に所定の処理を施す処理装置であって、マイナスイオンを用いて、高誘電率膜の不純物と酸化反応させる。すなわち、膜中に残った炭素などの有機物と反応し、除去することを特徴とする。マイナスイオンは、酸化物高誘電率膜中の酸素欠陥に、効率良く選択的(優先的)に結合するため、酸化するイオンの量を制御することで、酸化がさらに抑制される。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】水素の触媒作用によるコンタクトプラグ不良を防止する。

【解決手段】ソース領域、ドレイン領域およびゲートからなるトランジスタが集積化された半導体基板上に、前記ソース領域またはドレイン領域に接続されたコンタクトプラグと、前記コンタクトプラグに接続された下部電極と、前記下部電極の間に埋め込まれた酸素バリアを有する絶縁膜と、前記容量絶縁膜に形成された上部電極からなる強誘電体キャパシタにおいて、前記下部電極が酸素に対する導電性バリアを含み、さらに前記下部電極と絶縁膜との間に前記下部電極との反応を防止するための絶縁性反応防止膜を備えた構造になっている。

(もっと読む)

不揮発性メモリーセル、メモリーセルアレイおよび不揮発性メモリーセルの製造方法

本発明は、不揮発性メモリーセル、メモリーセルアレイおよび不揮発性メモリーセルの製造方法に関するものである。不揮発性メモリーセルは、チャネル領域として設計されたナノ素子を有する垂直電界効果トランジスタと、ナノ素子を少なくとも部分的に取り囲む、電荷蓄積層として、および、ゲート絶縁層としての電気絶縁層とを備えている。この電気絶縁層は、電気的な電荷担体をその内部に選択的に注入でき、または、その内部から除去できるように設計されており、電気絶縁層に注入された電気的な電荷担体によって、ナノ素子の導電性に特徴的に影響を及ぼすように設計されている。  (もっと読む)

(もっと読む)

電極を有するキャパシタを備えた集積回路およびキャパシタを製造するための方法

【課題】メモリセルに好適に使用できる電極を有するキャパシタを備えた集積回路およびキャパシタを製造するための方法を提供すること。

【解決手段】本発明は、電極を有する少なくとも1つのキャパシタを備えた集積回路(IC)に関しており、キャパシタの電極のうちの少なくともいずれか一方(10または30)は、少なくとも表面がケイ化物化された半球状結晶粒のシリコンまたはシリコン合金から形成されている。

また、本発明は、ケイ化物化電極を有するこのようなキャパシタを得るための製造方法に関している。

(もっと読む)

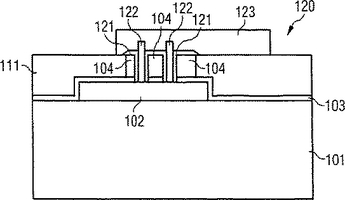

キャパシタと好ましくはプレーナ型のトランジスタとを有する集積回路構造およびその製造方法

プレーナ型であることが好ましいトランジスタ(142)とキャパシタ(144)とを有する集積回路構造(140)が開示されている。キャパシタ(44)の下部電極は、トランジスタ(142)のチャネル領域と共に、1つのSOI基板に配置されている。回路構造(140)は、簡単に製造でき、優れた電子特性を有している。  (もっと読む)

(もっと読む)

半導体不揮発性メモリセルアレイとその製造方法

【課題】半導体不揮発性メモリセルをより簡便な方法で動作させることができ、かつ製造コストの低減が可能であるメモリについて、メモリサイズの低減化とともに、ワード線と、情報を記録する第1及び第2電荷蓄積部との間隔を十分に確保してメモリセルをアレイ化できる実装構造を提供する。

【解決手段】半導体不揮発性メモリセルアレイは、複数個の半導体不揮発性メモリセルを有している。メモリセルは、制御電極30と、第1及び第2の主電極として働く、一対の不純物拡散領域21、22と、抵抗変化部24、26と、電荷蓄積部50、52とを有している。上述の複数の半導体不揮発性メモリセルの制御電極と電気的に接続されるワード線33と、ワード線と交差するように配置され、かつ不純物拡散領域からなるビット線とを有している。さらに、電荷蓄積部とワード線との間には、層間絶縁膜57、58が形成されている。

(もっと読む)

半導体記憶装置およびその製造方法並びに携帯電子機器

【課題】微細化が容易な半導体記憶装置を提供する。

【解決手段】半導体基板211上には、ゲート絶縁膜214を介して単一のゲート電極217を形成している。ゲート電極217の両側には、第1,第2のメモリ機能体261,262を形成している。半導体基板211のゲート電極217側の表面部にはP型のチャネル領域472を形成し、チャネル領域472の両側にN型の第1,第2の拡散領域212,213を形成している。チャネル領域472は、第1,第2のメモリ機能体261,262下に位置するオフセット領域401と、ゲート電極217下に位置するゲート電極下領域402とで構成されている。オフセット領域401にP型の導電型を与える不純物の濃度は、ゲート電極下領域402にP型の導電型を与える不純物の濃度に比べて実効的に薄くなっている。

(もっと読む)

Al2O3誘電体を用いるメモリ・セルの絶縁構造

【構成】この発明は,一例示的実施形態では,基板上に形成され,基板をバイアスし,集積回路構造(たとえば,DRAMメモリ・セル)の隣接する動作領域間を絶縁する絶縁ゲートを提供する。ゲート誘電体として,従来のゲート酸化物層ではなく,酸化アルミニウム(Al2O3)を用いて,トレンチ(溝)絶縁領域の下および近くに正孔過剰な蓄積領域を形成する。この発明の別の例示的実施形態は,シャロー・トレンチ(溝)絶縁(STI)領域の効果を高めるために絶縁領域内のライナとして利用される酸化アルミニウム層を提供する。これらの実施形態は,絶縁領域において一緒に用いることも可能である。 (もっと読む)

半導体記憶装置およびその製造方法

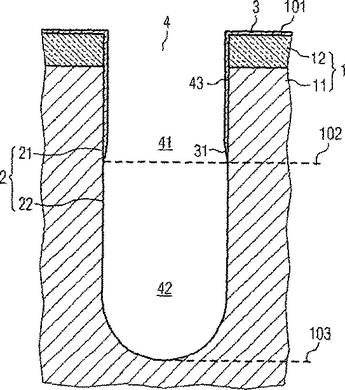

【課題】 カラー酸化膜を有する垂直トレンチの上端部に突出部がなく、該垂直トレンチへの埋込み性能を向上させた半導体記憶装置を提供する。

【解決手段】 半導体記憶装置の製造方法は、半導体基板10にトレンチ40を形成するステップと、トレンチ40の側壁にシリコン層50およびバリア層60を順次堆積するステップと、トレンチ40の下部にマスク材料70を充填するステップと、マスク材料70をマスクとしてトレンチ40の上部に堆積されたバリア層60を除去するステップと、マスク材料70を除去するステップと、バリア層60をマスクとしてトレンチ40の上部に堆積されたシリコン層50を酸化し、カラー酸化膜80を形成するステップと、カラー酸化膜80をトレンチ40の上方から異方的にエッチングするステップと、バリア層60を除去するステップと、トレンチ40内に導電材料90を堆積し、トレンチキャパシタを形成するステップとを備えている。

(もっと読む)

トランジスタ構造及びその製作方法

トランジスタ構造の少なくとも一部分が実質的に透明であるエンハンスメント・モード電界効果トランジスタである。該トランジスタの一変形形態は、ZnO、SnO2及びIn2O3から選択された実質的に絶縁性で実質的に透明な材料から構成されるチャネル層を含む。実質的に透明な材料から構成されるゲート絶縁体層は、チャネル層/ゲート絶縁体層境界面を形成するようにチャネル層に隣接して配置される。該トランジスタの第2の変形形態は、アニーリングにより生成される実質的に絶縁性のZnO、SnO2及びIn2O3から選択される実質的に透明な材料から構成されるチャネル層を含む。該トランジスタを含む装置、及び該トランジスタを作る方法も開示されている。  (もっと読む)

(もっと読む)

可変抵抗素子の駆動方法及び記憶装置

【課題】

電圧パルス印加により電気抵抗が変化するペロブスカイト型酸化物を備えてなる可変抵抗素子に対して可逆的な抵抗変化動作が安定して持続可能な駆動方法を提供する。

【解決手段】

可変抵抗素子は第1電極1と第2電極3の間にペロブスカイト型酸化物2を設けて形成され、第1電極1と第2電極3間に一定極性の電圧パルスを印加することにより第1電極1と第2電極3間の電気抵抗が変化し、更に、電圧パルスの印加における累積パルス印加時間の増加に対して抵抗値の変化率が正から負へと変化する抵抗履歴特性を有する。累積パルス印加時間が、抵抗履歴特性における累積パルス印加時間の増加に対する抵抗値の変化率が正から負へと変化する特定累積パルス印加時間を越えないように可変抵抗素子に電圧パルスを印加する。

(もっと読む)

ナノクラスタ電荷蓄積デバイスの形成方法

一実施形態では、ナノクラスタ電荷蓄積デバイスを形成する方法が提供される。半導体装置(10)の第1の領域(26および30)が1つまたは複数の非電荷蓄積デバイスを配置するために特定される。この半導体装置の第2の領域(28)が1つまたは複数の電荷蓄積デバイスを配置するために特定される。この1つまたは複数の非電荷蓄積デバイスのゲート絶縁体として使用されるゲート酸化物(22)がこの半導体装置の第1の領域(26および30)中に形成され、引き続きナノクラスタ電荷蓄積層がこの半導体装置の第2の領域(28)中に形成される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 基板面積の増大なしにキャパシタを容量増大できるDRAM又はこれとロジック回路とを混載した半導体装置の製造方法の提供。

【解決手段】 半導体装置の製造方法は次の通りである。基板上面に第1の絶縁膜50で埋められたトレンチを形成。第1の絶縁膜の一部の上部を除去し、トレンチ内及び基板の上面上に第2の絶縁膜を形成し、その上に導体膜を形成。導体膜及び第2の絶縁膜をパターニングし、ゲート電極16a、プレート電極16b及び容量絶縁膜15を形成。ゲート電極及びプレート電極をマスクとし、イオン注入によりメモリトランジスタの低濃度ドレイン拡散層17b及びソース拡散層18を形成。ゲート電極、プレート電極の側面上に、各々第1、第2のサイドウォール25a、25bを形成。尚、プレート電極は基板の上面の一部とトレンチの露出している側面とに亘る領域上に形成され、ソース拡散層は第1、第2のサイドウォールによって覆われる。

(もっと読む)

不揮発性半導体メモリ装置及びその製造方法

【課題】 トンネル絶縁膜を欠陥が生成されにくい高品質な絶縁膜にすることができ、書き込み・消去電圧を低減して、素子特性や信頼性の向上をはかる。

【解決手段】 第1導電型の半導体基板11の主面上に第1のゲート絶縁膜13を介して選択的に形成されたフローティングゲート電極14と、フローティングゲート電極14上に第2のゲート絶縁膜15を介して形成されたコントロールゲート電極16と、各ゲート電極に対応して基板11の主面に形成された第2導電型のソース・ドレイン領域18とを具備してなる不揮発性半導体メモリ装置であって、第1のゲート絶縁膜13は、シリコン窒化膜13aをシリコン酸化膜13b,13cで挟んで形成された3層構造であり、且つシリコン窒化膜13aは三配位の窒素結合となっている。

(もっと読む)

スピントランスファを利用する熱安定性磁性素子およびその磁性素子を用いるMRAMデバイス

熱的に安定した状態で、スピントランスファ効果を用いて書き込まれることができる磁性素子(120)、およびその磁性素子(120)を用いる磁気メモリを設けるための方法およびシステムを開示する。その磁性素子(120)は、第1(128)、第2(132)および第3(136)のピン止め層と、第1(130)および第2(134)の非磁性層と、自由層(140)と、非磁性スペーサ層(138)とを備える。第1(128)、第2(132)および第3(136)のピン止め層は強磁性であり、第1、第2および第3の方向にピン止めされた第1、第2および第3の磁化を有する。第1(130)および第2(134)の非磁性層はそれぞれ第1および第2の拡散障壁を含む。第1(130)および第2(134)の非磁性層はそれぞれ、第1のピン止め層(128)と第2のピン止め層(132)の間、および第2のピン止め層(132)と第3のピン止め層(136)との間に位置する。第1(128)および第2(132)のピン止め層、ならびに第2(132)および第3(136)のピン止め層は反強磁性結合される。非磁性スペーサ層(138)は導電性であり、自由層(140)と第3のピン止め層(136)との間に存在する。さらに、Coを含有する強磁性層にCrおよび/またはPtをドープすることによって、性能をさらに改善することができる。  (もっと読む)

(もっと読む)

金属酸化物薄膜の製造方法および薄膜複合材料

【課題】 高い温度で処理することなく、高誘電率を示す均質な金属酸化物薄膜の製造方法およびそれを用いた薄膜複合材料を提供する。

【解決手段】 (A)金属酸化物の結晶性微粒子の表面にシリカゾルを吸着させる工程、(B)(A)工程で得られたシリカゾル吸着結晶性微粒子を乾燥させることなく、金属酸化物の前駆体溶液中に分散する工程、(C)(B)工程で得られたシリカゾル吸着結晶性微粒子を分散した金属酸化物の前駆体溶液を基板上に塗布し、ゲル化させる工程、及び(D)(C)工程で形成したゲルを熱処理し、金属酸化物薄膜とする工程を含む金属酸化物薄膜の製造方法。前記の金属酸化物薄膜の製造方法により得られる金属酸化物薄膜と基板とからなる薄膜複合材料。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 誘電体膜の段差被覆性がよく、かつ誘電体物質の廃棄量を少なくする。

【解決手段】 下地膜8上に、パターニングされた下部電極11を形成する工程と、インクジェット方式の塗布機構を用いて、下部電極11上に誘電体物質を塗布する工程と、塗布された誘電体物質を加熱することにより、下部電極11上に誘電体膜12を形成する工程と、誘電体膜12上に上部電極を形成する工程とを具備する。上部電極を形成する工程は、下地膜8上及び誘電体膜12上に層間絶縁膜を形成する工程と、層間絶縁膜に、誘電体膜上に位置する開口部を形成する工程と、開口部の中及び層間絶縁膜上に導電体を堆積する工程と、層間絶縁膜上から導電体を除去することにより上部電極を形成する工程とを具備する。

(もっと読む)

インコンフォーマルな堆積を用いて半導体プロセス技術において基板を垂直にパターニングする方法

典型的には半導体ウェーハである基板(1)の、レリーフ状にパターニングされた基板表面(101)上に、堆積方法(ADL;atomic layer deposition:原子層堆積)を用いて、基板表面(101)に対して傾斜し、および/または垂直である処理表面(2)に、被覆層(3)が提供される。被覆層(3)は、前駆材料の少なくとも1つの処理量の制限によって、および/または堆積方法の時間的制限によって、簡易な方法において、基板表面(101)に対して垂直な方向にパターニングされ、後続のプロセス工程のための機能層あるいはマスクとして形成される。  (もっと読む)

(もっと読む)

超小型電子デバイスにおいて導電ワイヤの周囲のライナとして磁界コンセントレータを製造する方法

【課題】 書き込み磁界をMTJの自由層に集中させる磁気ライナ形状を効率的に生成することができる方法を提供する。

【解決手段】 MRAMセルにおいて、書き込み電流を低リラクタンス材料内に閉じ込める。この材料を、いくつかの方法のうち1つで処理して、保存要素に最も近い材料を無効として磁束を伝達し、これによって、磁束を保存要素へと集中させるU字形の断面を達成する。

(もっと読む)

不揮発性半導体メモリ装置およびその動作方法

【課題】電源電圧相当の電圧でメモリデバイスの閾値電圧を最大限に上昇させる動作を実現する。

【解決手段】半導体基板2とゲート電極6との間に形成され電荷蓄積能力を有する積層膜5を備えるメモリトランジスタ1は、書き込み時と読み出し時とで短チャネル効果が生じているか否かの境界として見積もられるチャネル長Lminが異なり、当該異なるチャネル長Lmin(R)とLmin(W)の間に、実デバイスのチャネル長Lを有する。

(もっと読む)

1,661 - 1,680 / 1,709

[ Back to top ]