Fターム[5F083JA02]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | 酸化物系 (9,104)

Fターム[5F083JA02]の下位に属するFターム

酸化膜を含む複合膜 (2,564)

酸化窒化膜 (1,013)

タンタル酸化膜(Ta2O5) (705)

ハロゲンを含む酸化膜 (7)

複酸化物 (3,106)

Fターム[5F083JA02]に分類される特許

1,601 - 1,620 / 1,709

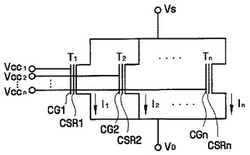

マルチビット不揮発性メモリセルを含む半導体素子及びその製造方法

【課題】マルチビット不揮発性メモリセルを含む半導体素子及びその製造方法を提供する。

【解決手段】不揮発性半導体素子は、ソース及びドレーン領域がそれぞれ共有される複数のトランジスタを備える単位セルを含み、複数のトランジスタは、それぞれ少なくとも一つのコントロールゲートと少なくとも一つの電荷蓄積領域とを含み、各コントロールゲートは各トランジスタのスレッショルド電圧をシフトするための少なくとも一つのコントロール電圧に連結される。これにより、フラッシュEEPROMの高集積化及びメガバイト当たり低コスト化を効果的に達成できる。

(もっと読む)

誘電体薄膜、薄膜誘電体素子及びその製造方法

【課題】 本発明の目的は、BST薄膜を膜厚が40nmを超えて200nm以下に極薄化させながらも、高誘電率の特性と低リーク電流密度の特性を両立させた誘電体薄膜及びそれを素子化した薄膜誘電体素子並びにその最適な製造方法を提供することである。

【解決手段】本発明にかかる誘電体薄膜は、膜厚が40nmを超えて200nm以下のチタン酸バリウムストロンチウム(Ba1−x,Srx)aTiO3)からなる誘電体薄膜であって、xが0.5<x≦0.7でaが1.0≦a≦1.2を満たす組成を有し、且つ比誘電率が250を超えてリーク電流密度が1.0×10−5A/cm2以下であることを特徴とする。本誘電体薄膜に上部・下部電極層を形成して薄膜誘電体素子とする。

(もっと読む)

磁気抵抗効果素子

【課題】半選択セルの誤書き込み防止とスイッチング磁場の低減を図る。

【解決手段】本発明の例に関わる磁気抵抗効果素子は、第1及び第2強磁性層とこれらの間に配置される非磁性層とからなる積層構造を有し、第1及び第2強磁性層のうちの少なくとも1つは、第1方向に磁気異方性を有する第1部分と、第1部分に結合され、第1方向及びこれと逆向きの第2方向とは異なる第3方向に磁気異方性を有する第2部分とから構成される。

(もっと読む)

キャパシタおよびキャパシタの製造方法および半導体装置

【課題】キャパシタの誘電体層にアモルファス層を導入することで、キャパシタの耐熱性を確保しつつキャパシタの誘電体層におけるリーク電流の発生を抑制することを可能とした。

【解決手段】第1電極11と第2電極16との間に誘電体層を備えたキャパシタ1において、この誘電体層は、高誘電体材料からなる第1高誘電体層13〜第3高誘電体層15を含み、少なくとも前記第1電極11、第2電極16および誘電体層の一部を構成する界面層(窒化シリコン層12)のいずれかと界面を有する第1、第3高誘電体層13、15は、第1電極11側および第2電極16側の少なくとも一方の側に結晶構造がアモルファスとなっているものである。

(もっと読む)

FeRAM装置に適用するSiO2、TiおよびIn2O3薄膜の選択的エッチング処理法

【課題】MFMoxに用いられるSiO2、チタンおよびIn2O3の薄膜の選択的エッチング技術を提供する。

【解決手段】本発明の上記薄膜の3層構造を選択的にエッチングする方法は、約10から30sccmの範囲内のC3F8と、約20から40sccmの範囲内のアルゴンとを使用し、約2から6mtorrの範囲内の圧力下での、約1000から3000wattの範囲内のRFソースと約400から800wattの範囲内のRFバイアスとを使用する、チタンの層で停止するSiO2のエッチングと、約10から50sccmの範囲内のBClと、約40から80sccmの範囲内の塩素と、約4から8mtorrの範囲内の圧力と約100から200wattの範囲内のRFバイアスとの下での約200から500wattの範囲内のTcpとを使用する、In2O3の層で停止するチタンのエッチング、とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 深孔の壁面におけるボーイングが抑制されたスタック型キャパシタを備える半導体装置を提供する。

【解決手段】 半導体装置100は、シリコン基板101の主面上部に形成された第三の層間絶縁膜123と、第三の層間絶縁膜123内に形成され上部に開口を有する筒状の下部電極125と、下部電極125の表面を覆って形成された筒状の誘電体膜126と、誘電体膜126上に形成され誘電体膜126を介して下部電極125と対向する上部電極127とを備えるキャパシタと、下部電極125の底部に金属シリサイド124を介して接続されるコンタクトプラグ122とを備える。下部電極125は、開口に隣接する上部電極部分が2層の多結晶シリコン膜153,154で構成され、金属シリサイド124に隣接する底部電極部分が2層の多結晶シリコン膜153,154の内で最上層の多結晶シリコン膜154で構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 成膜中に低誘電率界面層を生成させず、かつ熱処理後も低誘電率界面層の生成を抑制でき、ゲート絶縁膜としての High-k膜を有効利用する。

【解決手段】 Si基板10上にゲート絶縁膜12を形成した後にゲート電極13を形成する工程を含む半導体装置の製造方法であって、ゲート絶縁膜12として、Zr,Hf,Ti,及びランタノイド金属のうち少なくとも一つを含む酸化膜を、500℃以上800℃以下の温度領域で、且つ酸素分圧が1×10-4Pa以下の雰囲気下で成膜する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】SONOS構造の不揮発性メモリセルを有する不揮発性半導体記憶装置に関し、高速化・高集積化の2つの要求を同時に実現しうる不揮発性半導体記憶装置の構造及びその製造方法を提供する。

【解決手段】半導体基板内に形成されたチャネル領域と、チャネル領域上に、電荷保持絶縁膜を介して形成されたゲート電極と、第1の方向にチャネル領域を挟んで配置された第1のソース/ドレイン領域対と、第1の方向と交差する第2の方向にチャネル領域を挟んで配置された第2のソース/ドレイン領域対とを有し、第1のソース/ドレイン領域対を有する第1のメモリセルトランジスタと、第2のソース/ドレイン領域対を有する第2のメモリセルトランジスタとが、チャネル領域及びゲート電極を共用している。

(もっと読む)

磁気記録素子及びそれを用いた磁気記録装置

【課題】電流直接駆動磁化反転の際、平行→反平行の磁化反転時の反転電流を低減させ、反転電流の非対称性を改善する。

【解決手段】スピン偏極したスピン偏極電子を磁性体に流すことで情報が記録される磁気記録素子は、磁化が実質的に固定され強磁性材料で形成された固定層FPと、スピン偏極電子の作用により磁化が反転されマジョリティスピンバンド電子に対する第1の原子ポテンシャルとマイノリティスピンバンド電子に対する第2の原子ポテンシャルとを有する強磁性材料で形成された記録層FFと、固定層及び記録層間に設けられ非磁性材料で形成されたスペーサ層SPと、第1及び第2の原子ポテンシャルの中間値よりも低い第3の原子ポテンシャルを有する非磁性材料で形成され3nm以下の膜厚のキャップ層CPと、第3の原子ポテンシャルと異なる第4の原子ポテンシャルを有する非磁性材料で形成され、20nm以下の膜厚を有する反射層REFとを具備する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体基板4上にシリコン酸化膜5を介して例えばゲ−ト電極2を形成するに際し、このゲ−ト電極2を複数の多結晶シリコン層6の積層体で構成する。ゲ−ト電極2の部分は、非晶質層の堆積工程とこの非晶質材料の結晶化(再結晶化)工程とを有する薄膜の製造方法により形成する。この際、1回に成膜する非晶質層の厚さが不良事象に応じて決定される臨界応力値によって規定される厚み以下であるように非晶質層の堆積を複数回に分割して行い、各非晶質層の堆積工程後毎に非晶質材料を結晶化させ、かつ非晶質層堆積工程と非晶質材料結晶化工程を繰り返すことにより必要な膜厚の多結晶層6の積層構造体を得る。

【解決手段】 半導体装置の電気特性の劣化と、層間剥離,層内での割れ等の不良を防止し、かつ多結晶材料層の積層により、所望厚さで小粒径の多結晶層が得られる。

(もっと読む)

複数層のトンネリング障壁層を備える不揮発性メモリ素子及びその製造方法

【課題】データ保有時間及びデータ記録及び消去速度を向上させた不揮発性半導体メモリ素子及びその製造方法を提供する。

【解決手段】半導体基板21と、半導体基板21に形成されたソース22a領域及びドレイン22b領域と、ソース22a領域及びドレイン22b領域と接触して半導体基板21上に形成されたゲート構造体24と、を備える半導体メモリ素子において、ゲート構造体24は、相異なるバンドギャップエネルギーを持つ2層以上の複数層膜で形成されたトンネリング障壁層25を備える不揮発性メモリ素子。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】磁気抵抗効果素子をリソグラフィの解像限界以下のシャープな輪郭の形状にすることで、磁気特性の向上を図る。

【解決手段】磁気ランダムアクセスメモリは、複数のコーナーを有する平面形状であり、一つ以上のコーナーにおける曲率半径が20nm以下である磁気抵抗効果素子MTJを具備する。

(もっと読む)

不揮発性の半導体メモリ素子

【課題】ゲート電極層から電荷蓄積層への電子のバックトンネリング現象を防止し、記録の消去速度を速めた不揮発性の半導体メモリ素子を提供する。

【解決手段】半導体基板21と、基板に形成されたソース領域22a及びドレイン領域22b、及びソース及びドレイン領域と接触して半導体基板上に形成されたゲート構造体24とを備える半導体メモリ素子において、ゲート構造体は、4.4eV以上の高い仕事関数を有する物質を含んで形成されたゲート電極層28を備える。

(もっと読む)

不揮発性記憶素子及びその形成方法

【課題】不揮発性記憶素子及びその形成方法を提供する。

【解決手段】この素子は基板上に配置され、上へ突出したフィン、及びフィンを横切る制御ゲート電極を含む。制御ゲート電極とフィンとの間にフローティングゲートが介装される。フローティングゲートは第1及び第2貯蔵ゲートを含む。第1貯蔵ゲートはフィンの側壁上に配置され、第2貯蔵ゲートはフィンの上部面上に配置され、第1貯蔵ゲートと接続する。第1貯蔵ゲートとフィンの側壁との間に第1絶縁膜が介装され、第2貯蔵ゲートとフィンの上部面と間に第2絶縁膜が介装される。第2絶縁膜は第1絶縁膜に比べて薄い厚さを有する。制御ゲート電極とフローティングゲートとの間にブロッキング絶縁パターンが介装される。

(もっと読む)

記憶装置

【課題】状態遷移閾値に非対称なヒステリシスループが生じている抵抗変化素子を用いた場合であっても、その抵抗変化素子からの情報読み出しにあたって、誤書き込みや記憶情報破壊等が生じることなく、しかもその情報読み出し時における安定性を十分に確保する。

【解決手段】2つの電極11,12の間に記録層13を有してなり、前記電極11,12に極性の異なる電位を印加することにより前記記録層13の抵抗値が可逆的に変化する抵抗変化素子において、状態遷移閾値の絶対値が高抵抗状態から低抵抗状態への変化時と前記低抵抗状態から前記高抵抗状態への変化時とで互いに異なる場合に、前記記録層13の抵抗値を検出するための読み出し信号を、前記状態遷移閾値の絶対値が大きいほうの極性で、かつ、当該絶対値よりも小さい値で印加する。

(もっと読む)

記憶素子、メモリ及びメモリの記録方法

【課題】 安定して記録動作を行うことができ、高密度化を図ることができるメモリを提供する。

【解決手段】 情報を磁性体の磁化状態により保持する記憶層7と、この記憶層7に対して非磁性層4を介して設けられ、磁化の向きが固定された磁化固定層11とを少なくとも有し、記憶層7に対して、記憶層7よりも充分大きい抵抗値を有する抵抗層8を介して、スピン散乱の大きいスピン拡散層9が積層されている記憶素子20と、記憶素子20に電圧を印加するための電圧印加手段と、記憶素子20に磁場を印加するための磁場印加手段とを備えたメモリを構成する。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】フローティングゲート電極の充電容量を確保することが可能なフラッシュメモリ素子の製造方法を提供する。

【解決手段】本発明のフラッシュメモリ素子の誘電体膜形成方法は、半導体基板上にドーフトポリシリコン膜のフローティングゲート電極を形成し、前記ドフートポリシリコン膜上にHSG(Hemi Spherical Grain)形状のポリシリコン層を形成する段階と、前記HSG形状のポリシリコン層を形成した後、窒化処理工程を行う段階と、前記窒化処理工程済みの結果物上にAl2O3膜を形成する段階と、前記形成されたAl2O3膜上にコントロールゲート電極を形成する段階とを含む。

(もっと読む)

半導体記憶装置

【課題】一部を除去した配線パターンを利用して、ワード線に対するボーダーレスコンタクト或いは、ビット線に対するビアコンタクト等を歩留まり良く形成する。

【解決手段】メモリセルアレイ上の列方向に延伸する複数の活性領域パターンAAi,AAi+1,…,AAnと、行方向に延伸すると共に、非一様に配置される複数のワード線パターンWL1,WL2…と、複数のワード線パターンに平行に配列される複数の選択ゲート線パターンSG1,SG2…と、メモリセルアレイ上のワード線パターンの終端部分近傍において配置され、メモリセルアレイ端から引き出された配線の一部分に接触し、配線の隣の配線とは接触していないボーダーレスコンタクト14と、複数のワード線パターン及び選択ゲート線パターンの内の一部を2重露光により除去して形成したコンタクト形成予定領域内に配置されたビット線コンタクト(CB)11とを備える半導体記憶装置。

(もっと読む)

半導体記憶装置

【課題】 情報の読み出し時に、チャネル領域からの多数キャリアの放出による情報の変化と情報の保持時間の短縮を防止し、高速動作の可能な半導体記憶装置を提供する。

【解決手段】 半導体基板3上にチャネル領域4を直立に設け、このチャネル領域4の少なくとも一端にソース/ドレイン層5(6)を設け、チャネル領域4の両側面にゲート絶縁膜7、8を介して第1及び第2のゲート電極9、10を設ける。そして、チャネル領域4に情報の書き込みを行い、その情報の読み出しは、チャネル領域4とソース/ドレイン層5、6間のpn接合を逆方向バイアス状態にしておき、第1及び第2のゲート電極9、10に所定電位を印加することにより両ゲート電極9、10間に流れるトンネル電流量を検知することによって行う。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 トレンチの底部側の径に対する半導体基板表面部側のトレンチ径の比率が低くなっても、導電層の高抵抗化を抑制できるようにする。

【解決手段】 第2の導電層9の略中央に断面V字形状に溝部9aが形成されている。この溝部9aは、第2の導電層9を第1の導電層7上に埋込み形成する際に生じるシームの上部を開口することにより形成されている。この溝部9aには第3の導電層11が埋込み形成されている。これにより、第2および第3の導電層7および9の構造的な接触面積を増すことができ高抵抗化を抑制することができる。

(もっと読む)

1,601 - 1,620 / 1,709

[ Back to top ]