Fターム[5F083JA02]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | 酸化物系 (9,104)

Fターム[5F083JA02]の下位に属するFターム

酸化膜を含む複合膜 (2,564)

酸化窒化膜 (1,013)

タンタル酸化膜(Ta2O5) (705)

ハロゲンを含む酸化膜 (7)

複酸化物 (3,106)

Fターム[5F083JA02]に分類される特許

1,621 - 1,640 / 1,709

SOI上のMFIS強誘電体メモリアレイおよびその製造方法

【課題】薄く、完全に空乏化されたSOIデバイス上に形成されたデバイスに適したブロック消去の方法を提供する。

【解決手段】本発明によるMFISメモリアレイをブロック消去する方法は、複数のMFISメモリトランジスタゲートを接続するワード線を備えた複数のMFISメモリトランジスタを有するMFISメモリアレイを提供することを含む。共通のワード線に接続された全てのMFISメモリトランジスタ(49)は共通のソース(52)を有しており、各トランジスタのドレイン(50)がビット出力としての機能を果たし、ワード線に沿った全てのMFISチャネルがP+領域によって分離され、SOI基板上のP+基板領域(36)にさらに結合されている。本方法では、さらに、ワード線に沿った全てのビット出力、共通のソース、P+基板領域を一斉にグランド電位に維持する間において、ワード線に負のプログラミング電圧が印加される。

(もっと読む)

半導体装置およびその製造方法

【課題】 プロセスの手間のかからないDRAMセルを形成できるようにする。

【解決手段】 トレンチ4の内面にトレンチ面絶縁膜21を等方的に形成する。次に、トレンチ面絶縁膜21上のトレンチ4の内側壁上部についてプラズマ酸化(ラジカル酸化)により表層側絶縁膜22を形成する。その後、これらの絶縁膜21および22の内側に電極層7を埋込み形成する。

(もっと読む)

低消費電力磁気メモリ及び磁化情報書き込み装置

【課題】超低消費電力な高集積磁気メモリを提供する。

【解決手段】自由層311と、自由層の膜厚方向に形成された第一の固定層313と、自由層と第一の固定層との間に形成された絶縁障壁層312とを有する第一の素子部と、前記自由層311と、自由層の膜面方向に形成された第二の固定層315と、自由層と第二の固定層との間に形成された非磁性層314とを有する第二の素子部を備える。磁化情報の書き込みに際しては第二の素子部の膜面方向に電流Iwを流し、磁化情報の読み出しに際しては第一の素子部の膜厚方向に電流IRを流す。

(もっと読む)

メモリ及びその記録方法

【課題】 高速に情報を記録することができ、かつ信頼性の高いメモリを提供する。

【解決手段】 情報を磁性体の磁化状態により保持する記憶層4と、この記憶層4に対して非磁性層3を介して設けられ、磁化の向きが固定された磁化固定層2とを少なくとも有する記憶素子6と、非磁性層3を介して記憶層4と磁化固定層2との間に電流を流すための電流供給手段7と、記憶素子6に磁場を印加するための磁場印加手段8とを備えたメモリ10を構成する。

(もっと読む)

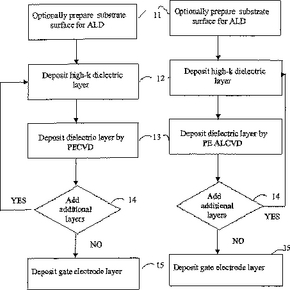

誘電体スタックの形成方法

本発明は、集積回路の中に誘電体スタックを形成する方法を提供し、(i)半導体基板上に高−k誘電体層を形成するステップと、(ii)高−k誘電体層を有する半導体基板を、プラズマ化学気相成長方法(PECVD)またはプラズマ原子層化学気相成長法(PEALCVD)において、窒素含有気相反応物およびケイ素含有気相反応物で処理するステップとを含む。さらに、本発明は、(i)少なくとも高―k材料を含む高―k誘電体層と、(ii)少なくともケイ素および窒素を含む誘電体層と、(iii)前記高―k誘電体層と前記誘電体層の間に配設された中間層とを含む集積回路中の誘電体スタックを提供し、前記中間層は前記高―k材料、ケイ素および窒素を含む。  (もっと読む)

(もっと読む)

記憶素子

【課題】 比較的単純な層構成でスピン注入磁化反転効率を上げることができ、微細加工が容易であり、高密度に集積可能な記憶素子を提供する。

【解決手段】 情報を磁性体の磁化状態により保持する記憶層17と、この記憶層17に対して非磁性層16を介して設けられた磁化固定層21とを少なくとも有し、非磁性層16を通じて、記憶層17と磁化固定層21との間に電流を流すことにより情報の記録が行われ、記憶層17に対して、磁化固定層21とは反対側に、非磁性層18を介して磁化の向きを変化させることが可能な磁化自由層19が設けられている記憶素子10を構成する。

(もっと読む)

磁気書き込み線を利用したMRAMメモリ

磁気ランダム・アクセス・メモリを提供して使用する方法およびシステムが開示される。この方法およびシステムは、複数の磁気メモリ・セル、第1の複数の書き込み線、および第2の複数の書き込み線を設けることを含む。第1の複数の書き込み線は、複数の磁気書き込み線である。複数の磁気線のうちの少なくとも1つ、および第2の複数の書き込み線のうちの少なくとも1つは、各々、複数の磁気メモリ・セルのうちの少なくとも1つに書き込むための電流を搬送する。好ましくは、複数の磁気書き込み線は、軟磁性の特性を有し、磁気ビット線であることが好ましい。磁気メモリ・セル内の磁気トンネリング接合スタックでは、磁気ビット線は、磁気メモリ・セルの自由層よりも遥かに厚く、これに近接して配置されていることが好ましい。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明は半導体装置及びその製造方法に関し、より詳細には一度データを入力すると時間が経ってもその状態を保持し、電気的にデータの入力と出力が可能なフラッシュメモリ装置及びその製造方法を提供する。

【解決手段】 フラッシュメモリ装置及びその製造方法において、半導体基板のセル領域上にはトンネル酸化膜とフローティングゲート及び高誘電率を有する物質からなる薄膜を含む誘電膜が形成されている。前記誘電膜上にはp型不純物がドーピングされたポリシリコン膜と金属物質からなる導電膜を含むコントロールゲートが形成されている。半導体基板の周辺回路領域上にはトンネル酸化膜と、フローティングゲートと同一の物質からなるポリシリコン膜パターン、及び前記導電膜と同一の導電膜パターンが形成されている。従って、不良の発生なしに簡略な工程を実施してもカップリング比が向上される。

(もっと読む)

記憶素子

【課題】 小さい電流で情報を記録することができ、かつ記録された情報を長期間保持することができる記憶素子を提供する。

【解決手段】 情報を磁性体の磁化状態により保持する記憶層17と、この記憶層17に対して非磁性層16を介して設けられた磁化固定層21とを少なくとも有し、非磁性層16を通じて、記憶層17と磁化固定層21との間に電流を流すことにより情報の記録が行われ、記憶層17がFe,Co,Niから選ばれる少なくとも1種の元素とGdとを含有する記憶素子10を構成する。

(もっと読む)

電荷トラッピング不揮発性メモリにおける検出の方法および装置

【課題】電荷トラッピング構造を有するメモリセルが、前記メモリセルの基板領域と、前記メモリセルのソース領域または前記メモリセルのドレーン領域のどちらか一方との間の電流を測定することによって、読み出される。

【解決手段】前記電荷トラッピング構造の他の部分が、関係のないデータを保存するとき、前記読出し動作は、前記電荷トラッピング構造の異なる部分の間の結合を低下させる。前記メモリセルの検出ウィンドウが、本読出し動作によって大幅に改善される。

(もっと読む)

磁気メモリ

【課題】 誤書き込みを防止でき、且つ書き込み電流を小さくできる磁気メモリを提供する。

【解決手段】 磁気メモリが備える複数の記憶領域のそれぞれは、外部磁界によって磁化方向が変化する第1磁性層41を含むTMR素子4と、書き込み電流によって第1磁性層41に外部磁界を提供する書き込み配線31と、空隙を介して対向する一対の端面5aを有する略環状体からなり、書き込み配線31の外周を囲むように配設された磁気ヨーク5と、書き込み電流の導通を制御する書き込みトランジスタとを有する。そして、TMR素子4は、その一対の側面4aが磁気ヨーク5の一対の端面5aと対向するように配設されている。この構成によれば、書き込み電流による磁界をTMR素子4へ効率よく提供できるので、第1磁性層41の磁化方向を小さな書き込み電流でもって反転させることができる。

(もっと読む)

磁気抵抗効果素子およびその製造方法

【課題】 高いMR比を有し、量産性を高め、実用性を高めた磁気抵抗効果素子およびその製造方法を提供する。

【解決手段】 この磁気抵抗効果素子(TMR素子10)は、一対の強磁性層とそれらの中間に位置するバリア層とから成る積層構造(TMR素子部12)を含むものであり、少なくとも一方の上記強磁性層は、少なくともバリア層に接する部分がアモルファス物質状態を有し、上記バリア層は単結晶構造を有するMgO層である。

(もっと読む)

不揮発性半導体記憶装置及び不揮発性半導体記憶装置の製造方法

【課題】 メモリセルトランジスタのショートチャネル効果を低減可能な不揮発性半導体記憶装置を提供する。

【解決手段】 絶縁層1と、絶縁層1上に複数のメモリセルトランジスタがマトリクス状に配置された不揮発性半導体記憶装置であって、メモリセルトランジスタM11は、絶縁層1上に配置された対向する第1導電型(n+型)のソース及びドレイン領域421,422と、ソース及びドレイン領域421,422に挟まれたソース及びドレイン領域421,422より不純物密度の低い第1導電型(n型)のチャネル領域411と、チャネル領域411上に絶縁されて配置された浮遊ゲート電極13と、浮遊ゲート電極13上に絶縁されて配置された制御ゲート電極15とを備えるデプレッション型のMISトランジスタである。

(もっと読む)

メモリ

【課題】 記憶素子の情報の読み出しと書き込みとの干渉に伴うエラーを本質的に低減させることができ、比較的容易に高い信頼性を実現することができるメモリを提供する。

【解決手段】 記憶層5に対して中間層4を介して磁化固定層3が設けられ、積層方向に電流を流すことにより、記憶層5の磁化の向きが変化して、記憶層5に対して情報の記録が行われる記憶素子10と、記憶素子10に対して積層方向の電流を流す配線とを備え、記憶層5に記録された情報を読み出す際には、記憶素子10の電気抵抗を高抵抗状態から低抵抗状態へと変化させるときの電流と同じ極性の電流が、配線を通じて記憶素子10に流れるメモリを構成する。

(もっと読む)

混合原子価導電性酸化物を用いたメモリ

【課題】

【解決手段】混合原子価導電性酸化物を用いたメモリが開示されている。そのメモリは、酸素欠乏状態で導電性が下がる混合原子価導電性酸化物と、酸素に対する電解質であり、酸素イオンの移動を引き起こすのに有効な電場を促進する電解質トンネル障壁と、を備える。

(もっと読む)

磁気メモリ

【課題】 大容量化および高速書き込みを可能にする。

【解決手段】 磁化の向きが外部磁界に応じて変化する磁気記録層4、磁化の向きが固着された磁化固着層8、および磁気記録層と磁化固着層との間に設けられた非磁性中間層6を有する記憶素子2と、磁気記録層の非磁性中間層と反対側に設けられ書き込み電流が流れる書き込み配線20と、書き込み配線の磁気記録層と反対側の面に接するように設けられたヨーク25と、を備えたメモリセルを含み、記憶素子の対向する一組の側面が書き込み配線およびヨークのそれぞれの対向する一組の側面とそれぞれ同一平面となるように構成され、磁気記録層の非透磁率が5以上であることを特徴とする。

(もっと読む)

SONOS記憶セル及びその形成方法

【課題】 SONOS記憶セル及びその形成方法を提供する。

【解決手段】 このセルは少なくとも一つの側壁を有する陥没された領域が配置された基板及び第1絶縁膜を介在して陥没された領域を満たすトラップ貯蔵パターンを含む。基板の上部面及びトラップ貯蔵パターンの上部面上に第2絶縁膜を介在して制御ゲート電極が配置される。制御ゲート電極両側の基板内に第1及び第2ソース/ドレイン領域が配置される。トラップ貯蔵パターンの上部面は平ら(flat)であり、少なくとも基板の上部面と同一の高さである。

(もっと読む)

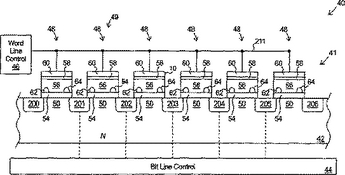

不揮発性メモリセルをプログラミングするための改良システム

デュアルビット誘電体メモリセル(48)のアレイ(40)は複数のビット線を有している。第1ビット線(201)はアレイ(40)内のメモリセルの列内の複数のメモリセル(38)のそれぞれにソース領域を形成する。第2ビット線(202)は列内の複数のメモリセル(38)のそれぞれにドレイン領域を形成する。第1ビット線(201)と第2ビット線(202)間には、逆の導電性のチャネル領域(50)が設けられており、それぞれと接合を形成している。選択ワード線(211)がチャネル領域(50)の上部に設けられており、また、同じ行内の複数のメモリセル(48)のそれぞれの上部にゲート(60)を形成している。複数の非選択ワード線(210、212)はそれぞれ選択ワード線(211)に並列であり、またそれぞれが複数のメモリセル(49)から選択されたメモリセル以外の列内の複数のメモリセル(48)の1つの上部にゲート(60)を形成している。ワード線制御回路(46)は選択ワード線(211)に正のプログラミング電圧(220)を印加し、また同時にビット線制御回路(44)はドレインビット線(202)に正のドレイン電圧を印加し、正のドレイン電圧よりも小さい正のソース電圧をソースビット線(201)に印加する。  (もっと読む)

(もっと読む)

トンネル磁気抵抗効果素子の検査方法及び装置、並びにトンネル磁気抵抗効果素子の製造方法

【課題】 TMR素子に関する信頼性の確認を、短時間かつ容易にしかも確実に行うことができるTMR素子の検査方法及び装置、この検査方法を用いたTMR素子の製造方法、並びにその製造方法によって製造されたTMR素子を提供する。

【解決手段】 TMR素子に互いに異なる電流値を有する複数のセンス電流をそれぞれ流した状態でこのTMR素子の抵抗値をそれぞれ測定し、測定した複数の抵抗値から抵抗変化量を求めてTMR素子の評価を行う。

(もっと読む)

半導体記憶装置

【課題】高強誘電体劣化を防止した信頼性の高い半導体記憶装置を得ること。

【解決手段】能動素子2と、能動素子2に接続される高強誘電体膜9を有する蓄積容量部と、前記蓄積容量部への水素の拡散を抑制するための拡散バリア層として設けられた絶縁膜とを具備することを特徴とする半導体記憶装置。

(もっと読む)

1,621 - 1,640 / 1,709

[ Back to top ]