Fターム[5F083JA02]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | 酸化物系 (9,104)

Fターム[5F083JA02]の下位に属するFターム

酸化膜を含む複合膜 (2,564)

酸化窒化膜 (1,013)

タンタル酸化膜(Ta2O5) (705)

ハロゲンを含む酸化膜 (7)

複酸化物 (3,106)

Fターム[5F083JA02]に分類される特許

1,681 - 1,700 / 1,709

半導体装置およびその製造方法

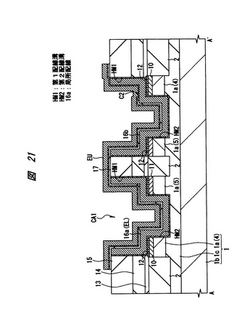

【課題】半導体装置、例えばSRAMのメモリセルのα線によるソフトエラーを低減する。

【解決手段】基板1aをエッチングして第1配線溝HM1を形成し、第1配線溝HM1下の素子分離2(または素子分離溝2および絶縁層1c)をエッチングして第2配線溝HM2を形成し、第1配線溝HM1および第2配線溝HM2の内壁に沿って局所配線16a,16bを形成し、一方の局所配線16aを下部電極ELとして、その下部電極EL上に容量絶縁膜となる窒化シリコン膜17、さらに上部電極EUを形成することにより、容量CA1の面積を増加させて、メモリセルの記憶ノードに相対的に大きな静電容量を付加する。

(もっと読む)

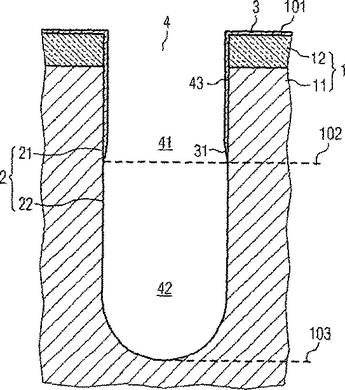

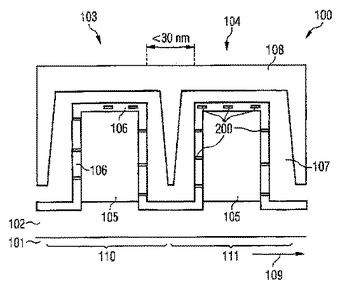

インコンフォーマルな堆積を用いて半導体プロセス技術において基板を垂直にパターニングする方法

典型的には半導体ウェーハである基板(1)の、レリーフ状にパターニングされた基板表面(101)上に、堆積方法(ADL;atomic layer deposition:原子層堆積)を用いて、基板表面(101)に対して傾斜し、および/または垂直である処理表面(2)に、被覆層(3)が提供される。被覆層(3)は、前駆材料の少なくとも1つの処理量の制限によって、および/または堆積方法の時間的制限によって、簡易な方法において、基板表面(101)に対して垂直な方向にパターニングされ、後続のプロセス工程のための機能層あるいはマスクとして形成される。  (もっと読む)

(もっと読む)

分離領域上に消去ゲートを有する不揮発性メモリ

本発明は、不揮発性メモリ装置及びそのような装置の製造方法を提供する。この装置は、浮遊ゲート(16)と、制御ゲート(19)と、分離した消去ゲート(10)とを備える。消去ゲート(10)は、基板(1)内に設けられた分離領域(2)中に、又はその上に設けられる。そのため消去ゲート(10)は、セル・サイズを増加させない。消去ゲート(10)と浮遊ゲート(16)との間の容量は、制御ゲート(19)と浮遊ゲート(16)との間の容量に比べて小さく、消去ゲート(10)と浮遊ゲート(16)との間の酸化物層を介してファウラー・ノルドハイム・トンネルによって浮遊ゲート(16)の帯電が消去される。  (もっと読む)

(もっと読む)

データ記録システムおよびこれを使用する方法

記憶層(2)はマイクロチップ(5)の配列に向かい合って配置される。記憶層(2)は電荷を記憶するように設計され絶縁された複数の導電性ドット(3)を備える。各マイクロチップ(5)はソース(8)とドレイン(9)を接続するトランジスタ・チャネル(7)と一体になっている高誘電率素子(6)を備える。チャネル(7)は高誘電率素子(6)に向かい合って配置されたドット(3)の電荷によって発生された電界によって変更されることができるコンダクタンスを有する。本システムは、マイクロチップ(5)に対する記憶層(2)の相対変位のためのアクチュエータを備えることができる。本システムは、1つのドット(3)から他のドット(3)への電荷の変位を引き起こすことができる電極の配列を備えることができる。  (もっと読む)

(もっと読む)

ゲート型電界効果デバイス及びその製法

本発明はゲート型電界効果デバイスに関し、その製法にも関する。一例では、ゲート型電界効果デバイスはソース/ドレーン領域ペアを含み、チャンネル領域をそれらの間に有している。ゲートはソース/ドレーン領域間でチャンネル領域に近接して受領される。ゲートはソース/ドレーン領域間にゲート幅部を有している。ゲート誘電体はチャンネル領域とゲートに近接して受領される。ゲート誘電体は少なくとも2つの異なる領域をゲートの幅部に沿って有している。これら異なる領域はそれぞれ異なる誘電率kを有する2つの異質領域を提供するように異なる材料で提供される。 (もっと読む)

ラテラルサイリスタ及びトラッピング層を有するシリコン‐オン‐インシュレータ読み取り‐書き込み不揮発性メモリ

改善した、サイリスタに基づくメモリセルを提供する。一例では、シリコン‐オン‐インシュレータ(SOI)技術を用いて、セル(10)をフローティング基板内に形成する。セルには、第2ワードラインによりゲート駆動されるとともに完全にフローティング基板内に形成されたラテラルサイリスタ(20)を有するのが好ましい。このサイリスタのカソードは、アクセストランジスタ(18)のソースをも有し、このアクセストランジスタのドレインは装置のビットラインに接続されており、このアクセストランジスタは第1ワードライン(14)によりゲート駆動される。フローティング基板内にはトラッピング層が形成され、セルに書き込みを行う場合、パルスを加えて、論理状態“1”に対し正孔をトラッピング層にトラッピングさせ、論理状態“0”に対し電子をトラッピング層にトラッピングさせる。トラッピング層に電荷をトラッピングさせることにより、記憶されたデータ状態に追加の余裕度を加え、これらデータ状態の劣化を回避し、セルを不揮発性とする。  (もっと読む)

(もっと読む)

NROMデバイス

【課題】1セルに対して複数のビットが記憶可能な高性能のフラッシュメモリトランジスタを提供する。

【解決手段】NROMフラッシュメモリセルのアレイは、4F2あたり少なくとも2ビットを記憶するように構成される。スプリット縦型チャネルは、隣接する柱状部の各側面に沿って形成される。単一の制御ゲートが柱状部及び柱状部間のトレンチ内にわたって形成される。スプリットチャネルは、トレンチ底部のn+領域、又はトレンチ底部を覆うように形成されるチャネルによって接続され得る。各ゲート絶縁層は、チャネル長の増大により、他の電荷記憶領域から十分に分離した状態で電荷を記憶することができる。

(もっと読む)

半導体構成のための電気的接続を形成する方法

本発明は、半導体構成に関連して電気的接続を形成する方法を含む。その上に導電線路を有し、導電線路に隣接して少なくとも2つの拡散領域を有する半導体基板が設けられる。パターン化されるエッチ・ストップが拡散領域の上に形成される。パターン化されるエッチ・ストップは、開口を貫通して延びる1対の開口を有し、開口は導電線路の軸に実質的に平行に一列に並んでいる。絶縁材料がエッチ・ストップ上に形成される。絶縁材料は、絶縁材料内にトレンチを形成し且つ開口をエッチ・ストップから拡散領域まで延ばすために、エッチングに対して露出される。トレンチの少なくとも一部分は開口の直上にあり、線路の軸に沿って延びる。導電材料が開口内とトレンチ内に形成される。  (もっと読む)

(もっと読む)

機能的中間層を持つ有機電子回路とその製法

特に高温での性能が改善された有機電子回路(C)であって、第1の電極(1a)と第2の電極(1b)との間に形成される有機エレクトレットまたは強誘電材料(2)で構成する。コンデンサ状の構造を持つセルが有機エレクトレットまたは強誘電材料(2)内に定義され、電極を介して直接または間接に電気的にアクセス可能である。少なくとも1つの機能的中間層(3a,3b)が電極(1a,1b)の1つと有機エレクトレットまたは強誘電材料(2)との間に形成される。中間層材料は一般に無機で、非導電で、有機エレクトレットまたは強誘電材料(2)に対して実質的に不活性である。一般に、中間層(3)は有機エレクトレットまたは強誘電材料(2)に対して、特に後者がフッ素を含む材料のとき、不活性である。マトリクス・アドレス可能なアレイを形成するために複数の回路(C)を用いる。中間層は、個別の中間層分子を解離せずに機能的中間層材料のソースから分子種として堆積される。  (もっと読む)

(もっと読む)

重合体中のナノ結晶体を用いるフラッシュメモリ装置

【課題】本発明は、重合体薄膜中に自発形成された金属又は金属酸化物のナノ結晶体を用いた高効率かつ低費用のナノフローティングゲートを有する、フラッシュメモリ素子及びその製造方法に関する

【解決手段】

本発明は、従来のフラッシュメモリ素子のナノ結晶体の形成過程と比較し非常に簡便にナノ結晶体を形成することを可能にする。全体的に均一な分布を有する結晶体であるため、重合体層中に結晶体の凝集現象を伴わずにナノ結晶体の大きさや密度を制御することが可能となる。更に本発明は、従来のナノフローティングゲートと比較し電気的または化学的に安全性を有するナノフローティングゲートを用いることにより、高効率かつ低費用のナノフローティングゲートを有するメモリ素子及びその製造方法を提供する。

(もっと読む)

ナノ対応可能なメモリデバイスおよび異方性電荷運搬アレイ

ナノ対応可能なメモリデバイスおよび異方性電荷運搬アレイ用の方法および装置が、記載される。一局面において、メモリデバイスは、基板と、基板のソース領域と、基板のドレイン領域とを含む。ナノエレメントの集団が、基板上のチャネル領域より上に堆積される。このナノエレメントの集団は、一実施形態において、金属量子ドットを含む。トンネル誘電体層が、チャネル領域の上に横たわる基板上に形成され、金属マイグレーションバリア層が、誘電体層全体にわたって堆積される。ゲートコンタクトは、ナノエレメントの薄膜全体にわたって形成される。ナノエレメントは、横への電荷移動を低減できる。メモリデバイスは、シングルステートまたはマルチステートのメモリデバイスであり得る。複数の離散的なエネルギレベルを有する1つ以上の量子ドットまたは分子を備えるマルチステートメモリデバイスにおいて、そのデバイスを充放電する方法が開示される。  (もっと読む)

(もっと読む)

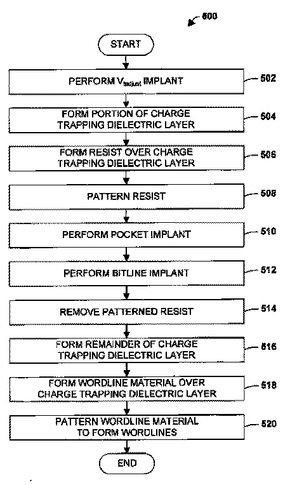

SONOSメモリセルの相補ビット妨害および蓄電の改善のためのポケット注入

デュアルビットメモリコアのアレイの少なくとも一部を形成する方法が開示される。最初に、電荷トラップ誘電層(608)の一部が基板(602)上に形成され、電荷トラップ誘電層(608)の一部の上にレジスト(614)が形成される。レジスト(614)がパターニングされ、ポケット注入(630)が所定の角度で実行され、基板(602)内にポケット注入部(620)が形成される。次に、基板(602)内に埋込みビット線(640)を形成するためにビット線注入(634)が実行される。次に、パターニングされたレジストが除去され、電荷トラップ誘電層(608)の残部が形成される。電荷トラップ誘電層の残部の上にワード線の材料(660)が形成されて、それはビット線(640)上にワード線(662)を形成するためにパターニングされる。ポケット注入部(620)は、特に、微細化によって生じるおそれのある相補ビット妨害(CBD)を軽減するのに役立つ。このように、ここに記載する発明思想により、半導体デバイスを小型化でき、高い実装密度を実現することができる。  (もっと読む)

(もっと読む)

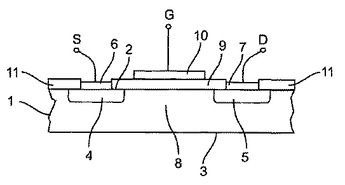

トンネル層に量子ドットを有するトランジスタ

本発明は、半導体本体(1)内に配置された半導体部品を記述したもので、前記半導体部品は、第1の導電型である少なくとも1つのソース領域(4)及び少なくとも1つのドレイン領域(5)を有し、ソース領域とドレイン領域の間に配置された第2の導電型である少なくとも1つの本体領域(8)を有し、絶縁層(9)により半導体本体から絶縁された少なくとも1つのゲート電極(10)を有し、前記絶縁層(9)は好ましくは焼結された一体化量子ドット含有層である。本発明は更に、量子ドット含有誘電性懸濁液が半導体本体に塗布され、次に例えば焼結によって一体化される上記の半導体部品の作製方法を記述する。  (もっと読む)

(もっと読む)

酸化ハフニウム層および酸窒化ハフニウム層または酸化ジルコニウム層および酸窒化ジルコニウム層のための前駆体としての溶解ハフニウムアルコキシドまたはジルコニウムアルコキシドの使用

本発明は、酸化ハフニウム層および酸窒化ハフニウム層用の前駆体としての高濃度の少なくとも1種のハフニウムアルコキシド溶液の使用に関するものである。本発明は特には、CVD法またはALD法用の酸化ハフニウム層および酸窒化ハフニウム層を製造するための濃度30〜90重量%の少なくとも1種のハフニウムアルコキシドの溶液の使用に関するものである。さらに本発明は、コーティング対象物上での酸化ハフニウム層および酸窒化ハフニウム層の製造方法、ならびに30〜90重量%の少なくとも1種のハフニウムアルコキシドを含むハフニウムアルコキシド溶液に関するものである。本発明の別の実施形態では、前記化合物において、ハフニウムをジルコニウムに置き換える。 (もっと読む)

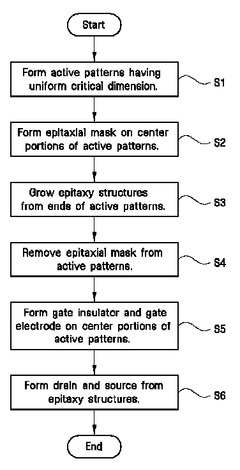

均一な臨界寸法のアクティブパターンで形成されたマルチゲートトランジスタ及びその製造方法

本発明は、均一な臨界寸法のアクティブパターンで構成されたマルチゲートトランジスタの製造方法を提供する。本発明はまた、均一な臨界寸法のアクティブパターンを具備するマルチゲートトランジスタを提供する。マルチゲートトランジスタの製造方法は先に少なくとも一つのアクティブパターンを形成する。以後、前記アクティブパターンの露出した領域から少なくとも一つのエピタキシ構造を成長させる。続いて、前記アクティブパターンの少なくとも2個の面にチャネル領域を形成する。  (もっと読む)

(もっと読む)

High−K材料とゲート間プログラミングとを使用する不揮発性メモリ・セル

不揮発性メモリ・デバイスは、ソース/ドレイン領域の間のチャネル領域と、フローティング・ゲートと、制御ゲートと、チャネル領域とフローティング・ゲートとの間の第1の誘電体領域と、フローティング・ゲートと制御ゲートとの間の第2の誘電体領域とを有する。第1の誘電体領域はHigh−K材料を含む。不揮発性メモリ・デバイスは、フローティング・ゲートと制御ゲートとの間で第2の誘電体領域を介して電荷を移動させることによってプログラムおよび/または消去される。 (もっと読む)

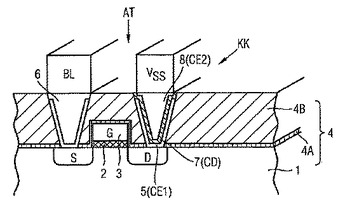

半導体メモリセルおよびその製造方法

本発明は、ストレージキャパシタが選択トランジスタ(AT)に接続されている半導体メモリセル、および、その製造方法に関するものである。本発明では、ストレージキャパシタは、ソース領域Sまたはドレイン領域Dのための少なくとも1つのコンタクトホールにおいて、コンタクトホールキャパシタ(KK)として形成されている。このような半導体メモリセルは、特にコスト効率よく製造することができ、かつ高集積度を達成できる。  (もっと読む)

(もっと読む)

集積回路メモリーセル及びその製法

【課題】セルデザインや工程を不必要に複雑化せずにセルサイズを減少させる。

【解決手段】

チャンネル30は、組み合わされた第1電極と第1ソース/ドレーンの半導電性上方延長部を含むことができる。メモリーセルは複数のメモリーセルのアレイを含んでおり、第2電極は複数の電極の中の共通電極である。メモリーセルは、第1電極とデジット線との間に直線導電通路を提供することができ、その通路は垂直トランジスターを通過して延びている。

(もっと読む)

ブリッジ電界効果トランジスタメモリセル、上記セルを備えるデバイス、および、ブリッジ電界効果トランジスタメモリセルの製造方法

本発明は、第1および第2の各ソース/ドレイン領域、第1および第2の各ソース/ドレイン領域の間に配置されたチャネル領域とを備え、これらの各ソース/ドレイン領域とチャネル領域とが半導体ブリッジに形成されている、ブリッジ電界効果トランジスタメモリセルに関するものである。

本発明のメモリセルは、さらに、半導体ブリッジの少なくとも部分上に堆積されている電荷記憶層と、電荷記憶層の少なくとも一部上の金属性で導電性のゲート領域とを備え、電荷記憶層は、ブリッジ電界効果トランジスタメモリセルに所定の電気的電圧を印加することにより、選択的に、電気的な電荷キャリアが、電荷記憶層に対し導入されるように、または、電荷記憶層から除去されるように配置されている。  (もっと読む)

(もっと読む)

高K誘電体膜

誘電体層(14,22,24,32)は、ランタン、ルテチウム、及び酸素により構成され、かつ2つの導体の間、または導体(14,20,34)と基板(12,26,30)との間に形成される。一の実施形態では、誘電体層は基板を覆って形成され、境界層を追加する必要がない。別の実施形態では、誘電体層(22,42,46)に含まれる元素の分布は、ランタン含有量またはルテチウム含有量に関して傾斜する、または誘電体層(22,42,46)は別の構成として、アルミニウムを含むことができる。更に別の実施形態では、絶縁層を導体または基板と誘電体層との間、または導体及び基板の両方と誘電体層との間に形成する。誘電体層は、分子ビームエピタキシー法によって形成することが好ましいが、原子層化学気相成長、物理気相成長、有機金属化学気相成長、またはパルスレーザ堆積によって形成することもできる。  (もっと読む)

(もっと読む)

1,681 - 1,700 / 1,709

[ Back to top ]