Fターム[5F083JA02]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | 酸化物系 (9,104)

Fターム[5F083JA02]の下位に属するFターム

酸化膜を含む複合膜 (2,564)

酸化窒化膜 (1,013)

タンタル酸化膜(Ta2O5) (705)

ハロゲンを含む酸化膜 (7)

複酸化物 (3,106)

Fターム[5F083JA02]に分類される特許

1,501 - 1,520 / 1,709

カーボンナノウォールの処理方法、カーボンナノウォール、カーボンナノウォールデバイス

【課題】ナノスケールを有する新規なカーボン構造物であるカーボンナノウォールの処理方法、カーボンナノウォール、カーボンナノウォールデバイスを提供する。

【解決手段】カーボンナノウォール(CNW)に対して形状処理を行う。形状処理としてはプラズマエッチング等のドライエッチング処理を採用できる。カーボンナノウォールを構成するグラフェンシートの少なくも先端部の厚みを根元部の厚みよりも減少させることが好ましい。

(もっと読む)

半導体装置及びその製造方法

【課題】 強誘電体キャパシタのダメージを防止しながら、安定した特性を得ることができる半導体装置及びその製造方法を提供する。

【解決手段】 配線より厚いAl2O3膜41を保護膜として形成した後、CMPにより、導電性バリア膜18が露出するまでAl2O3膜41を研磨する。つまり、Al2O3膜41に対して、導電性バリア膜18をストッパ膜としてCMPを行う。次に、例えば高密度プラズマ法によりシリコン酸化膜19を全面に形成し、その表面を平坦化する。次いで、シリコン酸化膜19上に、水素及び水分の侵入を防止する保護膜としてAl2O3膜20を形成する。更に、Al2O3膜20上に、例えば高密度プラズマ法によりシリコン酸化膜23を形成する。その後、シリコン酸化膜23、Al2O3膜20及びシリコン酸化膜19に、導電性バリア膜18まで到達するビアホールを形成し、その内部にWプラグ24を埋め込む。

(もっと読む)

超伝導ランダムアクセスメモリおよびその製造方法

【課題】 大部分の製造工程に高温プロセスを採用することができ、また、メモリセルの小型化が可能であり、さらに、直流のバイアス電流供給線路に効率的にインダクタンスを形成でき且つこのバイアス電流による磁場の影響を受けない、超高速で、大規模な、超伝導ランダムアクセスメモリのデバイス構造を提供する。

【解決手段】 最上層の超伝導グランド層である第1の超伝導グランド層(M7)上に、ジョセフソン接合(JJ)を含んだ超伝導ループと、複数層の超伝導配線層(M8〜M11)と、第1の抵抗層(RES1)とを有している。第1の超伝導グランド層(M7)下に、複数の超伝導配線層(M2、M4、M6)と、複数の超伝導グランド層(M1、M3、M5)と、第2の抵抗層(RES2)とを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】リーク電流を減少させ、かつ容量値を増加させることのできる薄膜キャパシタを提供する。

【解決手段】上部電極3および下部電極1は、TiN,Ti,W,WN,Pt,Ir,Ruの金属窒化物中から選ばれる少なくとも1つの材料から成り、容量絶縁膜2は、原子層成長(Atomic Layer Deposition:以下ALDという)法により形成したZrO2 、HfO2 、(Zrx ,Hf1-x )O2 (0<x<1)、(Zry ,Ti1-y )O2 (0<y<1)、(Hfz ,Ti1-z )O2 (0<z<1)あるいは(Zrk ,Til ,Hfm )O2 (0<k,l,m<1かつk+l+m=1)の少なくとも1つから選ばれる材料から成る。

(もっと読む)

半導体装置及びその動作方法

【課題】従来のメモリ素子とは異なり絶縁破壊等の現象を積極的に利用したメモリ素子を提供し、メモリ容量が増大されたメモリ装置を提供することを課題とする。

【解決手段】一対の電極間に、複数のメモリ材料層を積層させ、電圧印加によって順にメモリ材料層を破壊することを特徴とするメモリ装置及びその動作方法である。例えば、2つのメモリ材料層を積層した場合、一対の電極へ第1電圧を印加することにより当該メモリ材料層の一を破壊し、次いで第2電圧を印加することにより当該メモリ材料層の他を破壊するモリ装置を特徴とする。

(もっと読む)

トンネル磁気抵抗効果素子の検査方法及び装置、トンネル磁気抵抗効果素子の製造方法、並びにトンネル磁気抵抗効果素子

【課題】 TMR素子に関する信頼性の確認を、短時間かつ容易にしかも明確かつ確実に行うことができるTMR素子の検査方法及び装置、この検査方法を用いたTMR素子の製造方法、並びにその製造方法によって製造されたTMR素子を提供する。

【解決手段】 TMR素子に互いに異なる電圧値の複数の電圧を印加した状態でこのTMR素子の抵抗値をそれぞれ測定し、測定した複数の抵抗値から抵抗変化量を求めてTMR素子の評価を行う。

(もっと読む)

消去特性が改善されたメモリ素子の製造方法

【課題】消去特性が改善されたメモリ素子の製造方法を提供する。

【解決手段】(a)半導体基板上にトンネリング酸化層、電荷保存層及びブロッキング酸化層を順次に形成させる工程と、(b)トンネリング酸化層、電荷保存層及びブロッキング酸化層が形成された半導体基板を負電圧の固定酸化膜電荷を含むようにガス雰囲気で熱処理する工程と、(c)ブロッキング酸化層上にゲート電極層を形成させ、トンネリング酸化層、電荷保存層、ブロッキング酸化層及びゲート電極層の両側部をエッチングして基板の上面を露出させる工程と、(d)露出された基板の上面に不純物をドーピングして第1不純物領域及び第2不純水領域を形成させる工程と、を含む消去特性が改善されたメモリ素子の製造方法である。

(もっと読む)

誘電体層および対応する半導体デバイスを製造するための方法

【課題】多結晶誘電体層の形成方法と前記誘電体層を用いた半導体デバイスの提供。

【解決手段】多結晶誘電体層20は、酸化物または窒化物を含む第1の誘電体材料と前記誘電体層の重量の1重量%未満の第2の材料より形成される。第1の誘電体材料の粒子21境界に沿った漏洩電流が低減するように、前記第1の誘電体材料のエンタルピーより低いエンタルピーを有する非導電性の酸化物または窒化物を形成する第2の材料を含み、第1の誘電体材料の粒子境界に配置される。

(もっと読む)

強誘電体記憶装置および製造方法

【課題】基板上のトランジスタ部分のプラグと上部強誘電体キャパシタ電極とを接続する配線のあわせずれ防止のために余分なスペースが必要で、セルサイズの微細化に限界がある。

【解決手段】強誘電体メモリの強誘電体キャパシタとトランジスタ45が自己整合的に設けられることにより、キャパシタの電極90とトランジスタ45の拡散層40とを同じ配線90により接続することにより、あわせずれの問題を回避しセルサイズの微細化を達成する。

(もっと読む)

3つの状態を有する不揮発性メモリ及びその製造方法

【課題】十分容量を確保することができる不揮発性メモリ及びその製造方法を提供すること。

【解決手段】素子分離膜22が形成されたシリコン基板21と、基板21上に形成されたフローティングゲート28aと、基板21とフローティングゲート28aの両側の端部領域との間に配置されたトンネル酸化膜27と、基板21との間及びフローティングゲート28aとの間の拡散バリア膜を介して配置された強誘電体膜24と、ゲート酸化膜29を介してフローティングゲート28a上に形成されたコントロールゲート32と、積層されたフローティングゲート28a及びコントロールゲートを含む両側の側壁に形成されたスペーサ34と、スペーサ34が位置する領域を含み、コントロールゲート32の両側の端部領域に対応するの基板21のアクティブ領域の表層部に形成されたソース/ドレイン領域35とを備えている。

(もっと読む)

基板上への層の堆積法

本発明によれば、多孔性シリコン、シリカ、又はアルミナ基板の孔に屈折率nが電圧依存性を有する材料を堆積させる方法であって、堆積される前記材料の前駆体物質を前駆体溶液として設けること、前駆体溶液の液滴の微細ミストを形成すること、及び、前記液滴を前記多孔性基板に付着させること、を含む方法が提供される。本発明は初めて、充填率が少なくとも60%である多孔性シリコン、シリカ、及びアルミナ基板を提供するものである。100%近い充填率が実現可能である。上部電極及び下部電極が設けられると、充填された多孔性シリコン、シリカ、及びアルミナウェーハを電圧依存性を有するフォトニックデバイスとして使用することができる。例えばランダムアクセスメモリ等のマイクロ電子デバイスの製造において使用するべく、シリコン基板表面の溝を内張りするために、同じ方法を用いることができる。  (もっと読む)

(もっと読む)

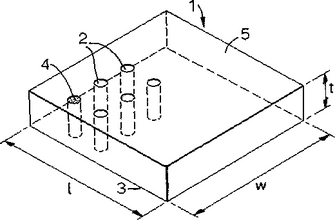

トレンチ・キャパシタ・アレイを含む構造およびその形成方法(SOIチップ用の簡略化した埋込プレート構造およびプロセス)

【課題】少なくとも一部がSOI基板の埋込酸化物層の下に配設されたトレンチ・キャパシタ・アレイを含む構造を提供すること。

【解決手段】各トレンチ・キャパシタは、埋込酸化物層の下に配設された第1のユニタリ半導体領域の少なくとも一部を含む共通のユニタリ埋込キャパシタ・プレートを共有する。この埋込キャパシタ・プレートの上部境界は、基板の主要表面に平行に、トレンチ・キャパシタ・アレイ全体にわたって横方向に延びる面を画定する。SOI基板またはバルク基板から開始する特定の実施形態では、トレンチ・アレイおよびコンタクト・ホールは、コンタクト・ホールがトレンチとほぼ同じ深さまで延びるように同時に形成する。好ましくは、コンタクト・ホールの幅は、トレンチの幅よりも実質的に広く、それによって、トレンチの壁に沿って延びるトレンチ・キャパシタを形成するのに用いる処理によって導電コンタクト・ビアを同時に形成することができる。

(もっと読む)

磁気メモリ装置及びその製造方法

【課題】磁性層のスピンの向きに基づく抵抗変化を利用した磁気メモリ装置及びその製造方法に関し、酸素や水素等による磁気抵抗効果素子の侵食を効果的に防止しうる磁気メモリ装置の構造及びその製造方法を提供する。

【解決手段】磁性層48,52を有し、磁性層48,52のスピンの向きに基づいて抵抗値が変化する磁気抵抗効果素子56と、磁気抵抗効果素子56上に形成され、化学量論的組成よりも酸素の組成比が少ない酸化物絶縁膜又は化学量論的組成よりも窒素の組成比が少ない窒化物絶縁膜よりなる不純物バリア層58とを有する。

(もっと読む)

金属窒化物をトラップサイトとして利用したメモリ素子及びその製造方法

【課題】金属窒化物をトラップサイトとして利用したメモリ素子及びその製造方法を提供する。

【解決手段】半導体基板21と、半導体基板21上に形成され、当該半導体基板21に形成された第1不純物領域22a及び第2不純物領域22bと接触するゲート構造体と、を備える半導体メモリ素子であって、ゲート構造体は、金属窒化物をトラップサイトとして利用している。

(もっと読む)

記憶素子及びメモリ

【課題】 比較的単純な構造で不揮発性メモリを構成することができる記憶素子を提供する。

【解決手段】 Zr,Hfから選ばれる少なくとも一種以上の元素の酸化物を主体とする酸化物層13と、この酸化物層13の下層及び上層に、それぞれTi,Zr,Hf,Taから選ばれる少なくとも一種以上の元素と窒素とから成る導電性窒化物層12,14が積層されて成る記憶素子10を構成する。

(もっと読む)

半導体記憶装置の製造方法

【課題】 キャパシタ特性の劣化を防いだ、高アスペクト比のキャパシタを有する半導体記憶装置の製造方法を提供する。

【解決手段】 メモリセル領域の選択用トランジスタのソース及びドレインのいずれか一方と接続された導電性プラグと周辺回路領域の回路の一部である第1の導電層とが埋設された絶縁膜を半導体基板上に形成する工程と、絶縁膜上に第1の層間絶縁膜を形成する工程と、第1の導電層と第1の層間絶縁膜よりも上層に設けられる第2の導電層とを繋ぐための接続プラグ42,43を第1の層間絶縁膜に形成する工程と、接続プラグを形成した後、キャパシタの下部電極51を第1の層間絶縁膜に形成する工程と、容量絶縁膜52を形成する工程と、キャパシタの上部電極53を形成する工程とを有する。

(もっと読む)

多ビット不揮発性記憶デバイス及びその形成方法

多ビット不揮発性記憶デバイスは、基板(10)上に形成された2つの絶縁層(12及び16)の間に挟まれた電荷蓄積層(14)を備える。厚い酸化層(18)は電荷蓄積層(14)の上に形成され、最小特徴部寸法の孔は厚い酸化層(18)内にエッチングされる。開口は厚い酸化層(18)内に形成される。電荷蓄積層上の孔の内壁に形成された側壁スペーサ(60)は、その間に最小特徴部寸法よりも小さな空隙(62)を有する。電荷蓄積層(14)がエッチングにより除去される際、側壁スペーサ(60)は、電荷蓄積層の一部をマスクする機能を果たし、側壁スペーサ(60)の下に2つの分離した電荷蓄積領域(55及び57)が形成される。デバイスは1つのマスク段階だけを使用して製造することができる。電荷蓄積領域を分離することにより、窒化物における電荷の側方伝導を防止できる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】王冠型の容量素子を備える半導体装置の製造に際し、容量電極の傾斜又は倒壊の発生を防止する方法を提供する。

【解決手段】半導体装置の製造方法は、絶縁膜20及びコンタクトプラグ22a,22b,22c上に絶縁23を介してポリシリコン27を堆積する工程と、ポリシリコン27にコンタクトプラグ22a,22b,22cの頂部を露出する開口26を形成する工程と、開口26の側壁に第1の容量絶縁膜30を形成する工程と、第1の容量絶縁膜30の表面に、コンタクトプラグ22a,22b,22cの頂部に接続する第2の導電性膜を形成し、容量電極32とする工程と、容量電極32及びコンタクトプラグ22a,22b,22cの表面に第2の容量絶縁膜33を形成する工程と、第2の容量絶縁膜33の表面に第3の導電性膜34を形成する工程と、第1の導電性膜27及び第3の導電性膜34を所定の電位に接続して対向電極に形成する工程とを有する。

(もっと読む)

電界効果トランジスタ及びその動作方法

【課題】 ゲート容量可変の電界効果トランジスタを用いた不揮発性メモリの消費電力と読み出しエラーとを低減する。

【解決手段】 シリコン基板101上にソース領域104とドレイン領域105を形成すると共にソース領域104とドレイン領域105とに挟まれた領域上に順次、絶縁膜102a、PCMO膜102b、ゲート電極103を積層して、電界効果トランジスタ1とする。PCMO膜102bに印加する書き込み電圧の電圧値を変えることによってデータを書き込み、PCMO膜102bに読み出し電圧を印加し、ドレイン電流を検出することによってデータを読み出す。

(もっと読む)

半導体記憶装置

【課題】トランジスタのスイッチ動作時に無駄に消費されていた蓄積電荷を有効利用して動作の高速化と低消費電力化を図る。

【解決手段】メモリセルMCは、ペアトランジスタを構成するトランスファゲート用のnMOSトランジスタ11a、11bと、nMOSトランジスタ11aに接続されたデータ記憶用の1個のキャパシタ12を含む。メモリセルMC内のnMOSトランジスタ11aのゲート電極はワード線WLに接続され、ドレインはビット線BLに接続されている。nMOSトランジスタ11bのゲート電極はワード線/WLに接続され、ドレイン及びソースはグランドに接続されている。キャパシタ12は、nMOSトランジスタ11aのソースとグランドとの間に接続されている。差動ビット線BL、/BLと差動データ線DL、/DLとの間にはY選択回路13が接続されている。Y選択回路13は、それぞれペアトランジスタを構成する2組のnMOSトランジスタ14a、14b及び15a、15bを有する。

(もっと読む)

1,501 - 1,520 / 1,709

[ Back to top ]