Fターム[5F083JA58]の内容

Fターム[5F083JA58]に分類される特許

161 - 180 / 368

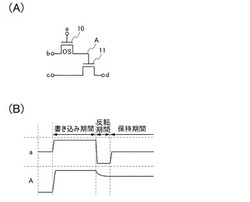

半導体装置の駆動方法

【課題】酸化物半導体層によってチャネル領域が形成されるトランジスタのソース及びドレインの一方に電気的に接続されたノードにおいて電荷の保持を行う半導体装置に記憶された情報の経時変化を抑制すること。

【解決手段】書き込み期間と保持期間の間に、トランジスタのゲートに強い負電位を与える期間(反転期間)を設ける。反転期間において、当該トランジスタのドレインから酸化物半導体層に対する正電荷の供給が促進される。これにより、酸化物半導体層内又は酸化物半導体層及びゲート絶縁膜の界面への正電荷の蓄積を短期間で収束させることができる。そのため、反転期間後の保持期間における当該トランジスタのドレインに電気的に接続されたノードにおける正電荷の減少を抑制することが可能である。すなわち、当該半導体装置に記憶された情報の経時変化を抑制することが可能である。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】本発明の実施形態は、電極間の短絡を防止することができ、電極との接触面積を大きくすることができる導電性ナノマテリアルを含む抵抗変化層を有する不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】実施形態によれば、基板の主面上を第1の方向に延在する第1の配線と、前記第1の方向と非平行な第2の方向に延在する第2の配線と、前記第1の配線と前記第2の配線との間に挟持され前記第1の配線と前記第2の配線とを介して印加される電圧または供給される電流により第1の抵抗状態と第2の抵抗状態との間を可逆的に変化可能な導電性ナノマテリアルを含む抵抗変化層と、を備え、前記抵抗変化層は、前記第1の方向及び前記第2の方向に対して略垂直な第3の方向に沿って密度が変化していることを特徴とする不揮発性半導体記憶装置が提供される。

(もっと読む)

不揮発性記憶装置

【課題】不揮発性記憶装置の特性を向上させる。

【解決手段】第1の配線と第2の配線とに接続された記憶セルを備え、前記記憶セルは、複数の層を有し、前記複数の層は、第1の電極膜と第2の電極膜に挟まれ、炭素を含有する記憶層と、前記第1の電極膜と前記記憶層との間および前記第2の電極膜と前記記憶層との間の少なくともいずれかに設けられた、炭素を含有するバリア層と、を有し、前記バリア層は、前記記憶層よりも電気抵抗率が低いことを特徴とする不揮発性記憶装置が提供される。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

半導体装置の製造方法

【課題】ビット線材料埋設体の形状のばらつきに起因するビット線の配線抵抗値のばらつきを防ぐ半導体装置の製造方法を提供する。

【解決手段】製造方法は、第一溝4内に第一のビット線材料埋設体6および第二のビット線材料埋設体10からなるビット線11を形成する第一工程と、ビット線11に含まれる不純物を拡散させて第一不純物拡散領域13を形成する第二工程と、ピラー部1bを形成する第三工程と、ピラー部1bに対向する配線17を第二溝15内に形成する第四工程と、ピラー部1bの先端部に、第二不純物拡散領域19を形成する第五工程と、を具備し、第一工程が、第一溝4を完全に埋め込むように第一ビット線材料を形成した後に第一ビット線材料表面を平坦化し、第一溝4底部に残るように第一ビット線材料をエッチバックする工程を具備する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルに書き込み用のトランジスタ、読み出し用のトランジスタおよび選択用のトランジスタを備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】書き込み電圧が小さいアンチヒューズを提供する。

【解決手段】アンチヒューズは読み出し専用の記憶装置のメモリ素子に用いられる。アンチヒューズは、第1導電層、絶縁層、半導体層、及び第2導電層を有する。アンチヒューズに含まれる絶縁層は、原料ガス中にアンモニアを添加して形成した酸化窒化シリコンであり、層中に1.2×1021以上3.4×1021atoms/cm3以下の水素、または3.2×1020以上2.2×1021atoms/cm3以下の窒素を含むことで、低電圧での書き込みが可能となる。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

薄膜キャパシタ

【課題】MIM構造の薄膜キャパシタにおいて、Ptに代わる上部電極を用いた場合であっても、IV特性や信頼性を維持する。

【解決手段】薄膜キャパシタ10は、基板12上に、下部電極14,誘電体層16,上部電極18を順次形成したMIM構造であり、上下の電極のうち、少なくとも上部電極18が、窒化物と金属を積層した積層電極となっている。窒化物としては、Ta,Tiなどの高融点金属を含むことが好ましく、また、窒化物と積層される金属が、前記窒化物に含まれる金属と同じであることが好ましい。更に、窒化物がSiを含んでいてもよい。少なくとも上部電極18に窒化物を含む積層電極を用いることで、Pt電極を用いる場合に必要だった特性回復のアニール処理の必要なく、同等のIV特性を得られるとともに信頼性も向上する。また、誘電体層16と上部電極18の密着性が改善され、剥離が生じない。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。また、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、半導体装置の各メモリセルを構成する、酸化物半導体を用いたトランジスタを直列に接続することにより、隣り合うメモリセルにおいて、酸化物半導体を用いたトランジスタのソース電極またはドレイン電極をお互いに接続させることができ、メモリセルの占有面積を低減することができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、容量素子は、第2のトランジスタのソース電極またはドレイン電極と、ゲート絶縁層と、第2のトランジスタを覆う絶縁層上に設けられた容量素子用電極を含み、第2のトランジスタのゲート電極と、容量素子用電極とは、絶縁層を介して少なくとも一部が重畳して設けられる半導体装置を提供する。第2のトランジスタのゲート電極と、容量素子用電極とを、異なる層で形成することで、半導体装置の集積度を向上させることができる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】絶縁層と、絶縁層中に埋め込まれたソース電極、およびドレイン電極と、絶縁層表面、ソース電極表面、およびドレイン電極表面、の一部と接する酸化物半導体層と、酸化物半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根(RMS)粗さが1nm以下であり、絶縁層表面の一部とソース電極表面との高低差、および絶縁層表面の一部とドレイン電極表面との高低差は、5nm以上の半導体装置である。

(もっと読む)

記憶素子及び記憶装置

【課題】情報の記録及び読み出しを容易に安定して行うことができ、比較的簡単な製造方法で容易に製造することができる記憶素子を提供する。

【解決手段】第1の電極2と第2の電極6との間に記憶用薄膜4が挟まれて構成され、記憶用薄膜4が絶縁材料又は半導体材料から成り、記憶用薄膜4と第1の電極2或いは第2の電極6との間に、Cu及びTeが含まれている薄膜3が形成されている記憶素子10を構成する。

(もっと読む)

記憶素子及びその製造方法

【課題】素子を微細化しても、安定して動作させることができる記憶素子を提供する。

【解決手段】メモリセル毎に分離して形成され、抵抗値の変化により情報を記憶させることができる記憶層13と、メモリセル毎に分離して形成され、かつ、記憶層13と積層して形成され、Cu,Ag,Zn,Al,Zrから選ばれる少なくとも1種の元素及びTe,S,Seから選ばれる少なくとも1種の元素を含むイオン源層14と、記憶層13及びイオン源層14をメモリセル毎に分離する絶縁層17と、各メモリセルの記憶層13及びイオン源層14の周囲に設けられた、元素の拡散を防止する拡散防止用バリア18を含んで、記憶素子を構成する。

(もっと読む)

半導体表示装置

【課題】作製工程を複雑化させることなく、高集積化を実現することが可能な、DRAM混載の集積回路の提供。

【解決手段】DRAMを有する集積回路であって、DRAMには、薄膜トランジスタを備えたメモリセルが複数設けられており、薄膜トランジスタは、活性層と、活性層が有するチャネル形成領域を間に挟んで重なり合っている第1の電極及び第2の電極とを有しており、データに従って薄膜トランジスタのドレイン電圧を制御することで、チャネル形成領域における正孔の蓄積の有無を選択し、正孔の蓄積の有無を把握することでデータを読み出すことを特徴とする集積回路。

(もっと読む)

半導体装置

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタは、半導体特性を示す金属酸化物により設けられ、下部のトランジスタが有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、該ゲート電極層と同一の層の一部を上部のトランジスタのバックゲートとして機能させる。下部のトランジスタは、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタのソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位変換回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体を用いて構成された半導体装置であって、ビット線の電位と等しい電位またはビット線の電位と異なる電位をソース線に選択的に与える機能を有する電位切り替え回路を備えた半導体装置とする。これにより、半導体装置の消費電力を十分に押さえることができる。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】専有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】書き込み用トランジスタと読み出し用トランジスタで、共通のビット線を使用することで、単位メモリセル当たりの配線数を削減する。情報の書き込みは、書き込み用トランジスタをオン状態とすることにより、書き込み用トランジスタのソース電極またはドレイン電極の一方と、読み出し用トランジスタのゲート電極が電気的に接続されたノードに、ビット線の電位を供給し、その後、書き込み用トランジスタをオフ状態とすることにより、ノードに所定量の電荷を保持させる。情報の読み出しは、容量素子に接続された信号線を読み出し信号線とするか、もしくは、読み出し用のトランジスタのソース電極またはドレイン電極の一方と接続された信号線を読み出し信号線として、読み出し信号線に読み出し用の電位を供給し、その後、ビット線の電位を検知することで行う。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと第2のトランジスタと容量素子とを各々含む複数のメモリセルをマトリクス状に配置し、メモリセルの一と他のメモリセルとを接続する配線(ビット線とも呼ぶ)と、第1のトランジスタにおけるソース電極またはドレイン電極と、が、第2のトランジスタにおけるソース電極またはドレイン電極を介して電気的に接続した構成とした半導体装置を提供する。これにより、第1のトランジスタにおけるソース電極またはドレイン電極と、第2のトランジスタにおけるソース電極またはドレイン電極と、を異なる配線に接続する場合と比較して配線の数を削減することができるため、半導体装置の集積度を向上させることができる。

(もっと読む)

161 - 180 / 368

[ Back to top ]