Fターム[5F083KA05]の内容

Fターム[5F083KA05]の下位に属するFターム

階層型ビット線 (163)

基板埋込型ビット線 (91)

拡散層で形成されたビット線 (218)

Fターム[5F083KA05]に分類される特許

1,021 - 1,029 / 1,029

半導体装置の製造方法および半導体装置

【課題】多層配線に挟まれたある層の層間絶縁膜が厚薄各部分を有する半導体装置を容易に製造可能な半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜中の一方領域においてコンタクトホールを比較的密に形成し、他方領域においてはコンタクトホールを比較的疎に形成して、層間絶縁膜の表面にCMPを施すことにより、比較的密なコンタクトホールの形成部分にエロージョンを発生させる。

(もっと読む)

磁気抵抗メモリセルアレイとこのアレイを含むMRAMメモリ

本発明は、論理的に編成された行と列に配列された磁気抵抗メモリセルを具備したマトリックスに関する。各メモリセルは、磁気抵抗素子を含む。マトリックスは、列のあるセルから読み出し、同時に列の別のセルに書き込む手段、または、行のあるセルから読み出し、同時に同じ行の別のセルに書き込む手段を備える。このようなマトリックスは、読み出し・書き込み同時処理型MRAMメモリに使用される。  (もっと読む)

(もっと読む)

半導体素子の製造方法

【課題】 シリコンを含むN型の導電領域と直接接続される導電パターンの形成時に、N型の導電領域と接続される部分のコンタクト抵抗の増大を防止し、バリア膜の厚さ増大に伴う導電パターンの寄生容量の増大を防止できる半導体素子の製造方法を提供すること。

【解決手段】 シリコンを含むN型の導電領域(207)にN型の不純物をドープして、N型の高濃度不純物拡散領域(212)を形成する工程と、CVD法を用いて高濃度不純物拡散領域(212)上にバリア用第1金属膜を蒸着し、高濃度不純物拡散領域(212)のシリコンと前記第1金属膜の金属とを反応させて、高濃度不純物拡散領域(212)と前記第1金属膜との間の界面に金属シリサイドを形成する工程、前記第1金属膜上に導電膜を形成する工程、及び、前記導電膜と前記第1金属膜とを選択的にエッチングして、導電パターンを形成する工程を含む。

(もっと読む)

半導体記憶装置

【課題】 データの破壊を効果的に防止する。

【解決手段】 一対のメモリセルMCL、MCRのドレイン拡散領域14、ソース拡散領域15にシリサイド層18が埋め込まれ、シリサイド層18の底面はシリコン酸化膜11まで達している。

(もっと読む)

メモリ・アレイ、メモリ・アレイを形成する方法、及びビット線に対するコンタクトを形成する方法

本発明は、メモリ・アレイと、メモリ・アレイを形成するために利用することができる方法を含む。ビット線コンタクト位置まで開口を残しながらストレージ・ノード・コンタクト位置を覆うパターン化されたエッチング停止層が、メモリ・アレイの製造期間に使用される。エッチング停止層上及びビット線コンタクト位置上に絶縁材料を形成し、絶縁材料を通ってトレンチが形成される。トレンチ内に導電材料を設け、ビット線コンタクト位置と電気的に接触し且つエッチング停止層によってストレージ・ノード・コンタクト位置から電気的に分離されたビット線相互接続線を形成する。後続の処理において、エッチング停止層を通って、ストレージ・ノード・コンタクト位置まで開口を形成する。次いで、開口内に、ストレージ・ノード・コンタクト位置と電気的に接触するようにメモリ記憶装置を形成する。  (もっと読む)

(もっと読む)

アレイ状に配置された垂直型カーボン・ナノチューブ電界効果トランジスタを製造する方法、並びに、それによって形成された電界効果トランジスタ及びアレイ

【課題】 カーボン・ナノチューブ電界効果トランジスタと、カーボン・ナノチューブ電界効果トランジスタのアレイと、デバイス構造体とを製造するための方法、及び、該方法によって形成されたデバイス構造体のアレイを提供する。

【解決手段】 本方法は、ゲート電極層と、各々がソース/ドレイン・コンタクトと電気的に結合された触媒パッドとを含む積層構造体を形成することを含む。ゲート電極層は多数のゲート電極に分割され、少なくとも1つの半導体カーボン・ナノチューブが、化学気相堆積プロセスによって触媒パッドの各々の上に合成される。完成したデバイス構造体は、ゲート誘電体によって覆われた側壁を有するゲート電極と、該ゲート電極の該側壁に隣接する少なくとも1つの半導体カーボン・ナノチューブとを含む。ソース/ドレイン・コンタクトを半導体カーボン・ナノチューブの両端と電気的に結合することによって、デバイス構造体が完成する。多数のデバイス構造体は、メモリ回路又は論理回路のいずれかとして構成することができる。

(もっと読む)

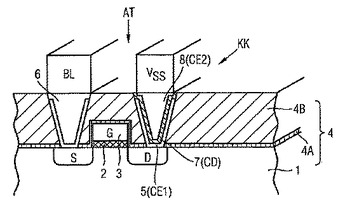

半導体メモリセルおよびその製造方法

本発明は、ストレージキャパシタが選択トランジスタ(AT)に接続されている半導体メモリセル、および、その製造方法に関するものである。本発明では、ストレージキャパシタは、ソース領域Sまたはドレイン領域Dのための少なくとも1つのコンタクトホールにおいて、コンタクトホールキャパシタ(KK)として形成されている。このような半導体メモリセルは、特にコスト効率よく製造することができ、かつ高集積度を達成できる。  (もっと読む)

(もっと読む)

縦型スプリットゲートNROMメモリ装置及びその形成方法

【課題】NROMセルの利点と縦型メモリセルの利点とを備えるメモリデバイスを提供する。

【解決手段】スプリットゲート縦型NROMメモリセル(1890)は、複数の酸化物柱状体(1830、1831)から構成される。複数の酸化物柱状体の各々の上部にはソース/ドレイン領域(1840、1841)が形成される。溝部が、酸化物柱状体の各対の間に形成される。ポリシリコン制御ゲート(1800)が、酸化物柱状体の対の間の溝部に形成される。ポリシリコンプログラムゲート(1805、1806)が、制御ゲートと各酸化物柱状体との間に形成される。プログラムゲートは、各酸化物柱状体の側壁に沿って延在する。ゲート絶縁層(1802、1803)が、各プログラムゲートとその近傍の酸化物柱状体との間に形成される。各ゲート絶縁層は、少なくともひとつの電荷を捕獲する電荷捕獲構造を有する。一実施形態において、ゲート絶縁構造は、酸化物−窒化物−酸化物の層である。中間絶縁層(1822、1824)が、プログラムゲートと制御ゲートとの間に形成される。

(もっと読む)

1T‐nメモリセル積層構造体

本発明は、クロスポイントと1T‐1セルとの双方の設計に基づくある種の利点を導入するためのメモリ技術及びメモリアレイに関する新規な変更に関する。これらの設計のある特徴を組み合わせることにより、1T‐1セル設計における読出し時間の高速化及び信号対雑音比の増大と、クロスポイント設計における高記録密度化との双方が達成される。そのために、単一のアクセストランジスタ16を用いて、“Z”軸方向に配置された複数のメモリアレイ層で垂直方向に互いに上下に積み重ねうる多重メモリセルを読出すようにする。  (もっと読む)

(もっと読む)

1,021 - 1,029 / 1,029

[ Back to top ]