Fターム[5F083KA07]の内容

Fターム[5F083KA07]に分類される特許

1 - 20 / 91

半導体装置の製造方法

半導体装置の製造方法

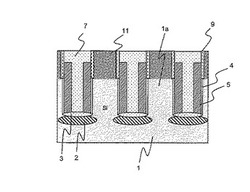

【課題】縦型トランジスタにおける上部拡散層の深さ方向のばらつきを低減することのできる半導体装置の製造方法を提供する。

【解決手段】本発明は表面が平坦なシリコン層からなる上部拡散層11を形成しようとするものであり、具体的には、ファセットを有するシリコン層を選択的に過剰成長させた後、層間絶縁膜7表面に形成されたシリコン層をCMPで擦り切ってシリコン層の表面を平坦化する。シリコン層の成長は、シリコン層を単結晶シリコンで選択的にエピタキシャル成長させる。この場合、ファセットが生じるので、最も成長が遅いファセットが層間絶縁膜表面より上方に位置するまで充分過剰に成長させる。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ別のマスクを用いた別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、ソース電極層またはドレイン電極層は、開口を埋め込むように絶縁層上に導電膜を形成し、絶縁層上の導電膜を化学的機械研磨処理によって除去することで形成される。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】本発明は、第1の不純物拡散領域と第2の不純物拡散領域との間に位置するピラーを流れるドレイン電流が、隣接するピラーにリーク電流として流れることを防止可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板13に立設されたピラー28と、Y方向に延在するように半導体基板13に設けられ、Y方向と交差するX方向において対向するピラー28の第2の側壁を露出する第1の溝16と、ピラー28の第2の側壁の下部に設けられた第1の不純物拡散領域と、ピラー28の上端に設けられた第2の不純物拡散領域と、半導体基板13に内設され、第1の溝16の底16Aに配置された絶縁層14と、を有する。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】酸化物半導体層、第1の導電層及び第2の導電層の積層によって構成されるソース電極層又はドレイン電極層、ゲート絶縁層、及びゲート電極層が順に積層されたコプレナー型のトランジスタにおいて、該ゲート電極層は、該第1の導電層と該ゲート絶縁層を介して重畳し、該第2の導電層と前記ゲート絶縁層を介して非重畳とする。

(もっと読む)

半導体装置

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層中に埋め込まれ、上面の少なくとも一部が下地絶縁層から露出した電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設け、電極層において、または、酸化物半導体層の低抵抗領域であって電極層と重畳する領域において、酸化物半導体層の上層に設けられる配線層との電気的な接続を行うトランジスタを提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造のフラッシュメモリーの提供

【解決手段】

半導体基板1上にシリコン窒化膜2及びシリコン酸化膜3が選択的に設けられ、シリコン酸化膜3上には、選択的に横(水平)方向エピタキシャルSi層5が設けられ、Si層5の両側面には、それぞれ側面を接して横(水平)方向エピタキシャルSi層6が設けられた構造からなる半導体層が素子分離領域のシリコン窒化膜4により絶縁分離されている。Si層6の残りの周囲には第1のゲート酸化膜10を介して包囲型フローティングゲート電極11が設けられ、包囲型フローティングゲート電極11の周囲には第2のゲート酸化膜12を介して包囲型コントロールゲート電極13(ワード線)が設けられ、Si層5には概略ソースドレイン領域9が設けられている2重包囲型ゲート電極を有するMIS電界効果トランジスタより構成したフラッシュメモリー。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールに埋め込まれたコンタクトプラグが埋め込み配線と非導通になることを防止した半導体装置及びその製造方法を提供する。

【解決手段】ゲート絶縁膜を介してピラー部9の側面と対向する位置において幅広となる形状を有する第1の溝部8を形成し、この第1の溝部8の幅広となる部分8bに埋め込まれた状態で第1の埋め込み配線15を形成し、複数のピラー部9が並ぶ領域よりも外側の領域において、第1の溝部8の間に位置すると共に、第1の溝部8の幅広となる部分8bに埋め込まれた第1の埋め込み配線15に至る深さで第1のコンタクトホール25を形成する。

(もっと読む)

半導体デバイスの製造方法

【課題】チャネル領域となる領域の直下だけに熱拡散によってビット線となる拡散層を形成することができる半導体デバイスの製造方法を提供する。

【解決手段】半導体基板の法線方向に複数の半導体ピラーを形成する工程、前記半導体ピラーで挟まれた溝の側面を覆うように絶縁膜を形成する工程、前記溝の内部全体を覆うように第1のポリシリコン膜を形成する工程、前記第1のポリシリコン膜上に前記半導体基板内へ拡散させる不純物で構成された不純物層を形成する工程、前記不純物層上に第2のポリシリコン膜を形成する工程、前記第2のポリシリコン膜上に前記不純物の外方拡散を防止する第1の拡散防止膜を形成する工程を経た後、前記不純物を前記溝の底部において前記半導体ピラー内に熱拡散させてビット線となる拡散層を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ワードライン間の素子分離を行い、メモリセルの微細化が可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10内に形成されたビットライン14と、ビットライン14上にビットライン14の長手方向に連続して設けられた絶縁膜ライン18と、ビットライン14間の半導体基板10上に設けられたゲート電極16と、ゲート電極16上に接して設けられ、ビットライン14の幅方向に延在したワードライン20と、ビットライン14間でありワードライン20間の半導体基板に形成されたトレンチ部22と、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】ウェル給電領域の面積を縮小して、半導体装置の微細化を行う。素子形成領域間のウェル電位のばらつきを抑制する。分離部の幅を細くする。

【解決手段】半導体装置は、半導体基板の表面に形成され、底部がウェル領域内に位置する溝状の分離部を有する。分離部は、ウェル領域と電気的に接続された導体配線と、底部に導体配線を埋め込む絶縁膜とを有する。分離部に囲まれるようにして区画されたウェル領域の一部は素子形成領域を形成し、素子形成領域には半導体素子が配置される。

(もっと読む)

半導体メモリ素子及びその製造方法

【課題】垂直型トランジスタを形成する過程において、ゲートと接触する活性領域の面積を増加させてゲートの接触抵抗特性を改善し、チャネル幅を増加させる半導体メモリ素子及びその製造方法を提供する。

【解決手段】第1の方向に延長するように形成された下部ピラーと、下部ピラー上に第1の方向と垂直な第2の方向に突出するように形成された上部ピラー290と、下部ピラーの一側壁に配置された埋め込みビットライン接合領域265と、トレンチを一部埋め込む埋め込みビットライン280と、エッチング停止膜285a上に形成された少なくとも上部ピラーの外周側面の一部を露出するようにリセスされた第1の層間絶縁膜290と、第1の層間絶縁膜上に形成された第2の層間絶縁膜295と、側面の一部が露出した上部ピラーの外周側面を覆いつつ、埋め込みビットラインと相互交差するゲート320aとを備えるように形成される。

(もっと読む)

埋め込みビットラインを備えた半導体装置の製造方法

【課題】埋め込みビットラインの抵抗を減少させることができる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板201に活性領域203を分離するトレンチ202をエッチングにより形成するステップと、活性領域203の何れか1つの側壁の一部を露出させた開口部207を有する絶縁膜205を形成するステップと、絶縁膜205上にトレンチ202を部分的に埋め込み、開口部207を埋め込むようにシリコン膜パターン208Aを形成するステップと、シリコン膜パターン208A上に金属膜209を形成するステップと、金属膜209及びシリコン膜パターン208Aを反応させて、埋め込みビットラインとなる金属シリサイド膜211を形成するステップとを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極の幅を十分に確保して、ゲート電極の抵抗値を小さくすることが可能で、かつゲート電極間の容量を小さくすることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板に設けられ、Y方向に延在する第1の溝15と、半導体基板に設けられ、第1の溝15と交差するXの方向に延在する第2の溝25と、第1及び第2の溝15,25に囲まれ、第2の溝25に露出された対向する第1及び第2の側面26a,26bを有するピラー26と、ゲート絶縁膜28を介して、ピラー26の第2の側面26bに接触するように、第2の溝25の下部に設けられた1つのゲート電極29と、ゲート電極29の側面とピラーの第1の側面26aとの間に配置された空隙と、を有する。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

埋め込み配線を備える基板、その製造方法、これを利用する半導体装置およびその製造方法

【課題】 低抵抗の埋め込み配線を備える基板の製造方法を提供する。

【解決手段】 始めに半導体用基板100の第1面S1上に導電層120を形成する。次に、導電層120をパターニングして第1方向に延長する線形の導電層パターン122を形成する。導電層120をパターニングするとき露出する半導体用基板100をエッチングして導電層パターン120の下部に第1方向に延長する線形の半導体パターン104を形成する。次に導電層パターン120および半導体パターン104上に絶縁層150を形成する。半導体用基板100の第1面S1側の絶縁層150が支持基板160と当接するように支持基板160上に配置する。次に半導体用基板100のイオン注入層102側の絶縁層150が露出するように半導体用基板100を除去する。これにより、導電層パターン120は、半導体パターン104の埋め込み配線として利用することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】更なる微細化に対応した高集積度のDRAMを得ることが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2の表層に、第1の方向Yに延在する第1の溝部3と、第2の方向Xに延在し且つ第1の溝部3よりも深くなる第2の溝部5と、第1の溝部3と第2の溝部5との交差部分において第2の溝部5よりも深くなる第3の溝部7と、第1の溝部3と第2の溝部5との間から突出されたピラー部8と、ピラー部8に形成された下部拡散層9、チャネル領域10及び上部拡散層11と、第2の溝部5の内側において第2の方向Xに延在するビット配線層と、第1の溝部3の内側においてピラー部8の側面を覆うゲート絶縁膜と、第1の溝部3の内側においてゲート絶縁膜を介してピラー部8の側面を横切るように第1の方向Yに延在するワード配線層とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】高速動作が可能な半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、第1の方向に平行に延在する第1素子分離溝部とそれに交差する方向に延在する第2素子分離溝部とが交互に連なってなる素子分離溝に第1絶縁膜を埋め込んで形成された素子分離領域を複数備え、素子分離領域間に第1素子形成部と第2素子形成部とが交互に連なってなる素子形成領域を複数備え、各第1素子形成部は所定数の第1半導体ピラーを備え、各第2素子形成部は第2半導体ピラーを備え、各素子形成領域はピラーの下部に不純物拡散層からなる第1のビット線を備え、ピラーの上部に上部不純物拡散層を備え、各素子形成領域の第2半導体ピラーの上部不純物拡散層に電気的に接続する第1のビット線より低抵抗の第2のビット線を備え、ピラーの下部側壁に第2絶縁膜を介して第2の方向に延在するワード線を備えることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、微細化された埋め込みビット線を容易に形成可能であると共に、埋め込みビット線の抵抗値を低くすることで高性能化を実現可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板13の主面13aに形成された第1の溝15と、第1の溝15の底面15a、及び第1の溝15の底部15Aに位置するピラー26の側壁面26a,26bに設けられ、側壁面26aを露出する第1の開口部16A、及び側壁面26bを露出する第2の開口部16Bを有した絶縁膜16と、第1の開口部16Aから露出された側壁面26aに形成された半導体基板と反対導電型の下部不純物拡散領域18と、絶縁膜16を介して、第1の溝15の底部15Aに設けられ、第1及び第2の開口部16A,16Bを埋め込むと共に、下部不純物拡散領域18及び側壁面26bと接触し、かつ金属膜よりなる埋め込みビット線21と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】シリサイド層の成長に起因するゲート電極と半導体基板との間のショートの発生を抑制した上で、シリサイド層を厚く形成可能な半導体装置の製造方法を提供する。

【解決手段】ピラー26の側面にゲート絶縁膜27を介して、ゲート電極51、52を形成し、ピラー26の上端に上部不純物拡散領域36を形成し、上部不純物拡散領域36上に形成された層間絶縁膜39、68を貫通し、かつ上部不純物拡散領域36の上面を露出するシリンダ孔71を形成し、シリンダ孔71の底部に、上部不純物拡散領域36の上面を覆うと共に、シリンダ孔71の一部を埋め込むシリコン膜42を形成し、シリコン膜42の上面、シリコン膜42よりも上方に位置するシリンダ孔71の内面を覆うように下部電極57を形成すると共に、下部電極57を形成する際の熱により、シリコン膜42に含まれるSiと下部電極57に含まれる金属とを反応させてシリサイド層43を形成する。

(もっと読む)

1 - 20 / 91

[ Back to top ]