Fターム[5F083KA06]の内容

Fターム[5F083KA06]に分類される特許

1 - 20 / 163

記憶装置

半導体メモリ装置およびその駆動方法

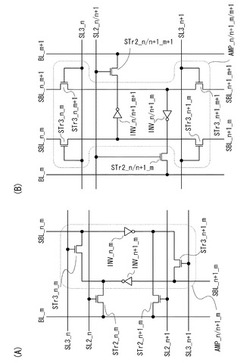

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。メモリブロックMB_n_mはサブビット線SBL_n_mと書き込みスイッチと複数のメモリセルを有する。サブビット線SBL_n_mと隣接するサブビット線SBL_n+1_mは2つのインバータと2つの選択スイッチよりなる増幅回路AMP_n/n+1_mに接続し、増幅回路は選択スイッチによりその回路構成を変更できる。また、増幅回路は読み出しスイッチを介してビット線BL_mに接続する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n/n+1_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。第n行のメモリブロックはサブビット線SBL_n_mと複数のメモリセルを有する。メモリセルはトランジスタと容量素子を直列に接続し、容量素子の電極の一をサブビット線SBL_n_mに接続する。さらに第n行のメモリブロックは書き込みトランジスタWTr_n_mと読み出しトランジスタRTr_n_mを有し、また、読み出しトランジスタRTr_n_mには相補型インバータ等の増幅回路AMP_n_mを接続する。サブビット線SBL_n_mの電位変動を増幅回路AMP_n_mで増幅する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】 可変抵抗素子への電圧印加極性が異なる2種類の書き込み動作後の各ベリファイ動作を夫々低消費電力且つ高速に実行可能な半導体記憶装置を提供する。

【解決手段】 書き込み回路22が、メモリセルの一端側から可変抵抗素子を経由して他端側へ電流を流すことで可変抵抗素子の電気抵抗を低抵抗化させるセット動作と、メモリセルの他端側から可変抵抗素子を経由して一端側へ電流を流すことで可変抵抗素子の電気抵抗を高抵抗化させるリセット動作を夫々実行可能に構成され、読み出し回路21が、メモリセルの一端側から可変抵抗素子を経由して他端側へ電流を流すことで可変抵抗素子の抵抗状態を読み出す第1読み出し動作と、メモリセルの他端側から可変抵抗素子を経由して一端側へ電流を流すことで可変抵抗素子の抵抗状態を読み出す第2読み出し動作を夫々実行可能に構成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択メモリセルトランジスタに電荷を蓄積する際の電圧を従来よりも自由に設定し得る不揮発性半導体記憶装置を提案する。

【解決手段】不揮発性半導体記憶装置1では、選択メモリセルトランジスタ115に電荷を蓄積させる際、電圧の高い書き込み禁止電圧をP型MOSトランジスタ9bから印加し、電圧の低い書き込み電圧をN型MOSトランジスタ15aから印加して、選択メモリセルトランジスタ115又は非選択メモリセルトランジスタ116へ電圧を印加する役割分担を、P型MOSトランジスタ9b及びN型MOSトランジスタ15aに分けたことで、P型MOSトランジスタ9b及びN型MOSトランジスタ15aそれぞれのゲート電圧やソース電圧を個別に調整でき、最終的にゲート基板間電圧を例えば4[V]等に設定し得る。

(もっと読む)

半導体装置

【課題】オン電流が少ないトランジスタを含むメモリセルと積層方向に延びるビット線により、低い製造コストで高速動作を実現可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、例えば、記憶素子とその読み出し電流経路に挿入される第1のトランジスタとを含むメモリセルMCと、このメモリセルMCの一端に直接接続され、記憶素子の情報を伝送する第1のビット線LBLと、第2のトランジスタを含み第1のビット線LBLを介して伝送される記憶素子の情報を増幅する第1のアンプLSAとを備えている。第1のアンプLSAは基板L0に形成され、メモリセルMCは基板L0の上部の第1の層L1〜L8に形成され、第1のビット線LBLは積層方向に延びる配線構造を含んで形成される。第1のトランジスタのチャネル中のキャリアの移動度は、第2のトランジスタのチャネル中のキャリアの移動度よりも低い。

(もっと読む)

半導体記憶装置

【課題】データの読み出し速度を向上する。

【解決手段】半導体記憶装置1は、メモリセルアレー1aと、コラム線1bと、第1および第2のデータ線1d,1eと、データの読み出し時には、コラム線1bに第1および第2のデータ線1d,1eの一方を選択して接続し、データの書き込み時には、コラム線1bに第1および第2のデータ線1d,1eを接続するスイッチ1cと、第1および第2のデータ線1d,1eに接続された読み出し回路1fと、第1および第2のデータ線1d,1eに接続された書き込み回路1gと、を有する。

(もっと読む)

ダイオードストラッピングを備えた熱アシストフラッシュメモリ

【課題】フラッシュメモリの動作速度及び耐久性を向上させる技術の提供。

【解決手段】メモリが、行及び列を含むメモリセルのアレイを有している。該メモリは、アレイ内の単数又は複数のワード線上の第1の離隔位置のセットに第1のバイアス電圧を印加するとともに、単数又は複数のワード線上の第2の離隔位置のセットに第1のバイアス電圧とは異なる第2のバイアス電圧を印加する、ワード線に結合された回路部を有し、第1の離隔位置のセットにおける位置は、第2の離隔位置のセットの位置の間に介在しており、それにより、第1の離隔位置のセットにおける位置と第2の離隔位置のセットにおける位置との間に、単数又は複数のワード線の加熱をもたらす電流の流れが誘導される。

(もっと読む)

半導体装置及び情報処理システム

【課題】ビット線構成が階層化されたメモリセルアレイにおいて、回路規模が小さくチップ面積の増加及びタイミングスキューを抑制可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、ビット線構成がローカルビット線LBLとグローバルビット線GBLとに階層化され、ローカルビット線LBLとグローバルビット線GBLとの間の接続を制御する階層スイッチSWを備えている。階層スイッチSWの制御のため、ローカルスイッチ制御線LSLとメインスイッチ制御線MSLが配置される。ローカルスイッチ制御線LSLはローカルスイッチドライバLSDにより駆動され、メインスイッチ制御線MSLはメインスイッチドライバMSDにより選択的に活性化される。メモリセルアレイの規模が大きくなっても、ローカルスイッチドライバLSDとメインスイッチドライバMSDの配置によるレイアウト面積の増大及びタイミングスキューを抑制することができる。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは容量素子の容量を減らすと、データの読み出しエラーが発生しやすくなった。

【解決手段】1つの主ビット線MBL_mに複数個のセルを接続させる。各セルはサブビット線SBL_n_mと2乃至32個のメモリセル(MC_n_m_1、等)を有する。さらに各セルは選択トランジスタSTr_n_mと読み出しトランジスタRTr_n_mを有し、読み出しトランジスタRTr_n_mのゲートにはサブビット線SBL_n_mを接続する。サブビット線SBL_n_mの寄生容量は十分に小さいため、各メモリセルの容量素子の電荷情報を読み出しトランジスタRTr_n_mでエラーなく増幅でき、主ビット線MBL_mに出力できる。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは容量素子の容量を減らすと、データの読み出しエラーが発生しやすくなる。

【解決手段】1つのビット線MBL_mに複数個のセルを接続させる。各セルはサブビット線SBL_n_mと4乃至64個のメモリセル(CL_n_m_1、等)を有する。さらに各セルは選択トランジスタSTr1_n_mとSTr2_n_mを有し、また、選択トランジスタSTr2_n_mには相補型インバータ等の増幅回路AMP_n_mを接続する。サブビット線SBL_n_mの寄生容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n_mでエラーなく増幅でき、ビット線に出力できる。

(もっと読む)

半導体メモリ

【課題】ビット線間の寄生容量による影響を低減することにより、高精度のデータの読出しを可能にする半導体メモリを提供する。

【解決手段】1つの主ビット線に互いに異なるタイミングでオン駆動するセレクタ素子及び当該セレクタ素子のそれぞれに接続された副ビット線を介して当該副ビット線のそれぞれにメモリセルが接続され、当該主ビット線に並置されるとともに固定電位に接続された固定電位線が設けられていること。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み可能回数が多く、信頼性の高い不揮発性半導体記憶装置を提供する。

【解決手段】複数の第1の配線、複数の第1の配線に交差する複数の第2の配線、並びに複数の第1及び第2の配線の各交差部に配置された電気的書き換え可能な抵抗値をデータとして不揮発に記憶する可変抵抗素子を含む複数のメモリセル、を有するメモリセルアレイと、複数の第1の配線の少なくとも一端に接続され、第1の配線を選択する第1のデコーダと、複数の第2の配線の両端に接続されて第1のデコーダが選択した第1の配線と第2の配線の両端との距離に応じていずれか一方が第2の配線を選択する少なくとも一対の第2のデコーダと、第1のデコーダ及び第2のデコーダによって選択された第1の配線及び第2の配線間に所定の電圧を印加する電圧印加回路とを備える。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】メモリセルアレイを構成する複数のメモリセルが、複数行ごとに複数のブロックに分割され、共通ビット線は、各ブロックにおいて、選択トランジスタを介して分割ビット線と電気的に接続されており、メモリセルの一は、第1のチャネル形成領域を含む第1のトランジスタと、第2のチャネル形成領域を含む第2のトランジスタと、容量素子と、を有し、ソース線は、第1のソース電極と接続され、分割ビット線は、第1のドレイン電極および第2のソース電極と接続され、ワード線は、容量素子の電極の一方と接続され、信号線は、第2のゲート電極と接続され、第1のゲート電極と、第2のドレイン電極と、容量素子の電極の他方とが接続される半導体装置を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体素子を有する構造体を複数積層して形成される半導体装置において、上層の構造体を形成する工程で用いられるレーザーによって、下層の構造体に熱負荷が生じることを防ぐ技術を提供する。

【解決手段】積層された複数のメモリマトリクスにより構成される相変化メモリにおいて、下層のメモリマトリクスと、下層のメモリマトリクス上に形成された上層のメモリマトリクスとの間に金属膜19を配置する。これにより、上層のメモリマトリクスを形成する際に用いられるレーザーを金属膜19により反射させることで、レーザーが金属膜19を透過することを防ぎ、下層のメモリマトリクス内の相変化材料層16などが直接レーザーによって加熱されることを防ぐ。

(もっと読む)

半導体装置

【課題】集積度の高い相変化メモリを実現する。

【解決手段】本発明による半導体装置は、複数のワード線と、複数のワード線と直交する複数のビット線との交点に配置された複数のメモリセル群を有する。複数のメモリセル群は、直列接続された第一乃至第二のメモリセルを有する。第一乃至第二のメモリセルの各々は、並列接続される選択トランジスタと抵抗性記憶素子とを有する。第一のメモリセルにおける選択トランジスタのゲート電極は、第一のゲート線に接続され、第二のメモリセルにおける選択トランジスタのゲート電極は、第二のゲート線に接続される。そして、複数のワード線を駆動する第一の回路ブロック(ワードドライバ群WDBK)は、第一乃至第二のゲート線を駆動する第二の回路ブロック(相変化型チェインセル制御回路PCCCTL)と、複数のメモリセル群(メモリセルアレーMA)との間に配置される。

(もっと読む)

半導体装置

【課題】ライト動作などの制御に比較的長い時間を要する半導体装置を小型化する。

【解決手段】第1及び第2のメモリセルアレイに其々対応して設けられたビット線制御回路BLC(1U,1)、BLC(1U,2)と、ビット線制御回路BLC(1U,1)、BLC(1U,2)に共通に接続され、第1の制御信号XCont(1U)を伝送する制御信号線と、ビット線制御回路BLC(1U,1)、BLC(1U,2)に其々接続され、第2及び第3の制御信号YCont(1),YCont(2)を其々伝送する制御信号線と、を備える。ビット線制御回路BLC(1U,1)は、第1及び第2の制御信号が活性化された場合に第1のメモリセルアレイに対する動作制御を行い、ビット線制御回路BLC(1U,2)は、第1及び第3の制御信号が活性化された場合に第2のメモリセルアレイに対する動作制御を行う。

(もっと読む)

メモリセル電荷記憶素子あたりに二重のコントロールゲートを有するフラッシュメモリセルアレイ

【課題】フローティングゲートが少なくとも2つのコントロールゲートラインと容量的に結合するようになっているフラッシュNANDタイプのEEPROMシステムの提供。

【解決手段】コントロールゲートラインはフローティングゲートの側壁と結合するようにフローティングゲート間に位置し、メモリセルの結合比が望ましく高められる。フローティングゲートの選択された行の両側の両方のコントロールゲートラインは普通同じ電圧まで高められ、隣接するフローティングゲートの選択されていない行に結合された第2のコントロールゲートラインは低く保たれる。選択されたフローティングゲートの領域でその電圧を選択的に高めるために、コントロールゲートラインを基板と容量的に結合させる。フローティングゲートの長さとコントロールゲートラインの厚さとは、スペーサのエッチマスクを形成することによってプロセスの最小分解エレメントより小さくされ得る。

(もっと読む)

半導体記憶装置

【課題】電力消費をより低減可能な新たなビット線階層化方式を備えた半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、行列状に設けられた複数のメモリブロックBと、複数のメモリブロックBに対応して設けられた複数の主ビット線GLとを具備する。メモリブロックBは、行列状に設けられた複数のメモリセルCと、列ごとに設けられた複数の副ビット線BLと、列及び行ごとに設けられ、複数のメモリブロックBに共通である複数のワード線WLと、対応する主ビット線GLを複数の副ビット線BLのいずれかに接続するスイッチ回路SCとを備える。読出し対象の対象セルC1の読出し動作時に、対象セルC1に対応する主ビット線GL1を選択し、対象セルC1の列に対応する副ビット線BL1をスイッチ回路SC1により選択し、複数のワード線WLのうち、対象セルC1の列及び行に対応するワード線WL1を選択する。

(もっと読む)

不揮発性半導体記憶装置

【課題】生産性及び動作安定性の向上を可能とする不揮発性半導体記憶装置を提供する。

【解決手段】交互に積層された複数の電極膜14及び絶縁膜を含み、X軸方向に延在する第1、第2積層構造体Sa1、Sa2と、これらに積層された第1、第2選択ゲート電極SGa1、SGa2と、これらのそれぞれを貫通し、下端が接続された第1、第2半導体ピラーSPa1、SPa2と、電極膜14と記憶層と、X軸方向と交差する第1、第2配線LL1、LL2と、交互に積層された複数の電極膜14及び絶縁膜を含む積層構造体Sbと、それに積層された選択ゲート電極SGbと、これらを貫通し下端が接続された第1及び第2選択部半導体ピラーSPb1,SPb2と、第4方向に延在する第3、第4配線LL3,LL4と、第4配線LL4は第2配線LL2に接続され、第3配線LL3の上に設けられ第3配線L3に接続された第5配線LL5と、を備える。

(もっと読む)

1 - 20 / 163

[ Back to top ]