Fターム[5F083LA26]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | チップレイアウト (365) | 周辺回路がチップ4周辺部に配置 (27)

Fターム[5F083LA26]に分類される特許

1 - 20 / 27

半導体装置

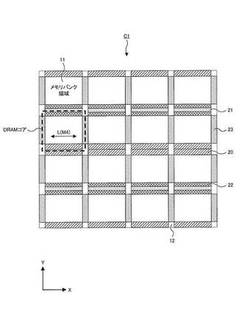

【課題】半導体チップに構成されるメモリコアにおける電源系を容易に分離可能な配線構造を実現しスループットの向上が可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体チップC1に複数のメモリコア(DRAMコア)が構成される。各メモリコアは、第1電源によって動作しパラレルデータを双方向に伝送するデータバスを駆動する第1回路領域と、第1電源と分離された第2電源によって動作しデータバスを伝送されるパラレルデータと外部端子を介して入出力されるシリアルデータとを双方向に変換する第2回路領域と含む。第1貫通電極群23は、第1回路領域に第1電源を供給する複数の貫通電極をY方向に並べて配置され、第2貫通電極群21は、第2回路領域に第2電源を供給する複数の貫通電極をY方向と交差するX方向に並べて配置される、それぞれの貫通電極群を経由して第1及び第2電源の配線群が互いに分離した配置で形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】セルトランジスタが形成された第1領域と周辺回路トランジスタが形成された第2領域を有する半導体装置において、周辺回路トランジスタの上部拡散層のチャネル領域への導電型ドーパントの分布を抑制し、セルトランジスタと周辺回路トランジスタにおける駆動電流の閾値電圧依存性のばらつきを低減する半導体装置の製造方法を提供する。

【解決手段】基板を第1領域と第2領域に区分し、前記第2領域の前記基板上面を前記第1領域の前記基板上面より所定の掘り下げ量だけ掘り下げる工程と、前記第1領域に第1ピラーを、前記第2領域に前記第1ピラーよりも高さが前記掘り下げ量だけ低い第2ピラーを各々形成する工程と、前記第1及び第2ピラーの下部に第1拡散層を、上部に第2拡散層を各々形成する工程と、前記第1及び第2ピラーと前記第1拡散層の側面にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜側面にゲート電極を形成する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】非晶質炭素膜を用いて形成する電極のアスペクト比を増大させる。

【解決手段】半導体装置の製造方法は、半導体基板上に第1非晶質炭素膜を形成し、周辺回路領域の第1非晶質炭素膜を除去してメモリセル領域の第1非晶質炭素膜を第2非晶質炭素膜とし、第2非晶質炭素膜を覆う第1シリコン酸化膜を基板全面に形成し、第2非晶質炭素膜上の第1シリコン酸化膜を除去して周辺回路領域の第1シリコン酸化膜を第2シリコン酸化膜とし、第2非晶質炭素膜と第2シリコン酸化膜を覆う第1絶縁膜を形成し、第1絶縁膜に第1開口を形成し、第1開口を埋め込む第2絶縁膜を形成し、第2絶縁膜に第2開口を形成し、第2開口と第1開口が重なる位置に露出する第2非晶質炭素膜にホールを形成し、ホール内に下部電極を形成し、第2絶縁膜を除去して第1開口内に第2非晶質炭素膜を露出させ、露出した第2非晶質炭素膜を全て除去する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

記憶装置

【課題】記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

【解決手段】基板に設けられた駆動回路と、駆動回路上に設けられ、駆動回路によって駆動される複数のメモリセルアレイと、を有し、複数のメモリセルアレイはそれぞれ複数のメモリセルを有し、複数のメモリセルはそれぞれ、酸化物半導体層と重畳する第1のゲート電極と、を有する第1のトランジスタと、ソース電極又はドレイン電極と、第1のゲート絶縁層と、導電層と、を有する容量素子と、を有し、複数のメモリセルアレイは重ねて配置される。こうして、記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

(もっと読む)

記憶装置、集積回路装置、及び電子機器

【課題】マルチポートメモリーとして機能する場合に、クロストークノイズを大幅に低減して、誤動作を防止して回路動作の安定化を図る記憶装置等を提供する。

【解決手段】メモリーセルアレイ10を有する半導体記憶装置100は、第1の方向に並ぶメモリーセルを選択するための第1のワードラインと、第2の方向に並ぶメモリーセルを選択するための第2のワードラインと、第1のワードラインによって選択されたメモリーセルに接続される一対の第1のビットライン及び第1の相補ビットラインと、前記第2のワードラインによって選択されたメモリーセルに接続される第2のビットラインとを含み、第2のワードラインは、対応する一対の第1のビットライン及び第1の相補ビットラインに対し、上面から見て第1の方向又は該第1の方向の反対方向に隣接して、第2の方向に延びるように配置される。

(もっと読む)

半導体装置

【課題】半導体装置を小型化することを課題の一とする。また、記憶素子を有する半導体装置の駆動回路の面積を縮小することを課題の一とする。

【解決手段】入力端子と出力端子の位置が固定された複数のセルを第1の方向に配置し、各セルの入力端子および出力端子とそれぞれ電気的に接続される配線を複数のセル上に積層させ、且つ、その配線の延在方向をセルが並べられた第1の方向と同方向とすることで、駆動回路の小型化を図った半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】チャネル領域を従来よりも拡大することが可能な半導体装置を提供する。

【解決手段】埋め込みゲート用の溝部9,10のうち、活性領域6に形成される第1の溝部9よりも素子分離領域5に形成される第2の溝部10の深さを深くすることによって、第2の溝部10の底面の間から活性領域6の一部が突き出した第1のフィン部12aと、埋め込みゲート用の溝部9,10の少なくとも上面開口部よりも下部側において、第1の溝部9よりも第2の溝部10の第1の方向における幅を大きくすることによって、第2の溝部10の両側面の間から第1のフィン部12aに連続して活性領域6の一部が突き出した一対の第2のフィン部と12bとを形成する。

(もっと読む)

不揮発性半導体記憶装置及び不揮発性半導体記憶装置の製造方法

【課題】不揮発性半導体記憶装置の製造プロセスを大幅に変更することなく、電極間のショートを避けることができる、不揮発性半導体記憶装置及び不揮発性半導体記憶装置の製造方法を提供するものである。

【解決手段】不揮発性半導体記憶装置は、半導体基板上に形成された第1の絶縁膜を有し、且つ、第1の絶縁膜上に複数の周辺トランジスタが形成された、周辺回路領域と、半導体基板上に形成された、第1の絶縁膜と厚さが異なる第2の絶縁膜を有し、且つ、第2の絶縁膜上に複数のメモリセルトランジスタが形成された、セルアレイ領域と、半導体基板に埋め込まれた状態に形成された、周辺回路領域とセルアレイ領域とを分離する、上面が面一に構成された、第1の素子分離絶縁膜と、これらの上部に全体的に形成された層間絶縁膜と、を備える。

(もっと読む)

メモリアレイの下方に配置されたセンスアンプ回路とセンス・アンプ・インターフェイス等ではないページレジスタとを有する3Dメモリ装置

不揮発性記憶デバイスは、基板と、その基板の一部分の上方に配置された不揮発性記憶素子のモノリシック3次元メモリアレイと、その不揮発性記憶素子と通信する複数のセンスアンプと、そのセンスアンプと通信する複数の一時記憶デバイスと、その一時記憶デバイスと通信するページレジスタと、1つまたは複数の制御回路と、を含む。この1つまたは複数の制御回路は、ページレジスタ、一時記憶デバイスおよびセンスアンプと通信する。センスアンプは、モノリシック3次元メモリアレイの下方にある基板上に配置される。一時記憶デバイスは、モノリシック3次元メモリアレイの下方にある基板上に配置される。ページレジスタは、モノリシック3次元メモリアレイの下方ではない領域にある基板上に配置される。センスアンプによって不揮発性記憶素子から読み出されたデータは、一時記憶デバイスに転送され、その後1つまたは複数の制御回路に応答してページレジスタに転送される。不揮発性記憶素子にプログラムされるデータは、その1つまたは複数の制御回路に応答してページレジスタから一時記憶デバイスへと転送される。 (もっと読む)

半導体装置及びその製造方法

【課題】階段状に加工された複数の導電層と、各導電層に達し深さの異なる複数のコンタクトホールとの接続構造の信頼性を高めた半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、基板10の第2のコンタクト領域5上に設けられ、第2のコンタクト領域5と第1のコンタクト領域4との間に段差を形成する下地層45bと、下地層45bを覆って基板10上に設けられ、下地層45b上に積層された上段部81が階段状に加工された下層側積層体91と、下層側積層体91における第1のコンタクト領域4上に積層された下段部82の上に設けられ、階段状に加工された上層側積層体92と、階段状に加工された部分を覆う層間絶縁層62と、層間絶縁層62を貫通し階段状に加工された部分の各々の導電層WLに達して形成されたコンタクトホール内に設けられたコンタクト電極51と、を備えた。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】半導体基板の表面に形成された拡散層領域における半導体基板の膨張の発生を抑制することが可能な、半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板111と、半導体基板111の表面に形成され、半導体基板111の表面に平行な所定方向に沿って交互に設けられ、素子分離層121の上面の高さが活性層122の上面の高さよりも低くなっている素子分離層121及び活性層122と、活性層122の表面に形成された拡散層131と、拡散層131の上面及び側面に形成され、半導体基板111を形成する半導体よりも格子定数の小さい材料で形成されたストレスライナー132とを備える。

(もっと読む)

半導体記憶装置

【課題】最小加工寸法幅で並列され、コンタクトの抵抗抑制が可能な素子領域を有する半導体記憶装置を提供する。

【解決手段】素子領域33aが、曲折部35の両端部にそれぞれ接続され、最小加工寸法幅の直線部34を有し相異なる素子領域方向21に延在し、素子領域33aと同形状の素子領域33b、cが、素子領域方向21から45度のワード線方向23に曲折部35があるように、それぞれ素子分離領域31を隔てて並行し、半導体基板11に垂直なコンタクトプラグ41が、曲折部35にそれぞれ接続され、素子領域33でそれぞれ構成の選択トランジスタ46に共通の選択ゲート線38が、絶縁膜39上で、コンタクトプラグ41に近接しワード線方向23に並列延在し、素子領域33でそれぞれ構成のメモリセル45に共通のワード線37が、絶縁膜39上で、選択ゲート線38に対してコンタクトプラグ41の反対側でワード線方向23に並列延在する。

(もっと読む)

不揮発性半導体記憶装置

【課題】NAND型フラッシュメモリのセルアレイの行方向端におけるSTI 領域の突出側面に沿って列方向に浮遊ゲート形成用ポリシリコン膜のエッチング残りが発生しても、NANDセル内のトランジスタの積層ゲート間絶縁膜およびゲート絶縁膜の破壊を防止する。

【解決手段】NAND型フラッシュメモリの半導体基板30上に積層ゲート構造を有する複数のメモリセルトランジスタに直列に積層ゲート構造を有する選択ゲートトランジスタを接続したNANDセルのセルアレイの行方向端には列方向にSTI 領域20が形成され、行方向端部にダミー用NANDセルが形成されている。このダミー用NANDセルの選択ゲートトランジスタの積層ゲート33、32間の絶縁膜34にはゲート間接続用溝35が存在せず、この選択ゲートトランジスタの積層ゲート間が導通しない状態に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、ポケット注入によるロールオフ現象の抑制と共に、セルキャパシタにおいて電荷を長期間保持できるようにすること。

【解決手段】チャネル領域におけるシリコン基板30の上にゲート絶縁膜40を形成する工程と、ゲート絶縁膜40上に第1の方向D1に延在する第1のワード線45aと第1の方向D1に交差する第2の方向D2に延在する第2のワード線45aとを形成する工程と、第1のワード線45aの上面の一部を覆うレジストパターン47を形成する工程と、レジストパターン47をマスクに使用し、基板表面の垂直方向からビットコンタクト領域Iに傾いた方向であって、且つ、第1の方向D1と第2の方向D2の両方に対して斜めの方向から、チャンネル領域と同導電型の不純物をビットコンタクト領域I側の活性領域にイオン注入する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、周辺回路素子領域に配置した補償容量素子により信号遅延が生じる問題があった。

【解決手段】本発明にかかる半導体装置は、メモリセルが配置される第1の領域と、機能回路が配置される第2の領域10と、第1の領域に形成されるセルコンデンサと、第2の領域10に形成される補償容量素子(36〜38)と、を備え、補償容量素子(36〜38)は、セルコンデンサと同一の下部電極36と、容量絶縁膜37と、上部電極38とからなり、機能回路のトランジスタのドレイン拡散層44、46又はゲート電極32の上方を除いて、第2の領域10の上層を覆うように形成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の動作を安定化できる。

【解決手段】本発明の例に関わる半導体は、半導体基板1と、半導体基板1内に設けられる2つの拡散層7と、2つの拡散層7間のチャネル領域上に設けられるゲート絶縁膜2と、ゲート絶縁膜2上に設けられる複数の導電膜3A,3B,4Aと複数の絶縁膜5A,5B,5Cとが積層された積層体6と積層体6上に設けられるシリサイド層4Bとからなるゲート電極10と、を具備し、積層体6のうち、シリサイド層4Bとは異なる構成の導電膜3Aが、ゲート絶縁膜2と接触することを特徴とする半導体装置。

(もっと読む)

半導体装置及びその制御方法

【課題】可変抵抗型メモリ素子を備えた半導体装置におけるデータ書き込み動作の安定性向上。

【解決手段】可変抵抗12及びダイオード14が直列に接続されてなるメモリセルMCと、メモリセルMCのアノード側に接続されたワード線WLと、メモリセルMCのカソード側に接続されたデータ線DLと、ワード線WL及びデータ線DLの一方に接続され、メモリセルMCを選択する選択信号をメモリセルに対して印加する選択回路WDrと、ワード線WL及びデータ線DLの他方に接続され、選択信号がメモリセルに対し印加されている間に、可変抵抗12を高抵抗状態に変化させる第1パルス及び可変抵抗12を低抵抗状態に変化させる第2パルスのいずれかである書き込みパルスをメモリセルMCに対して印加する書き込み回路DDrと、を具備することを特徴とする半導体装置

(もっと読む)

不揮発性半導体メモリ

【課題】信頼性の高い不揮発性半導体メモリを提供できる。

【解決手段】本発明の例に関わる不揮発性半導体メモリは、複数のメモリセルが配置されるメモリセルアレイ領域100と、メモリセルアレイ領域100の周囲を取り囲む周辺回路領域と、周辺回路領域とメモリセルアレイ領域100との境界部分であるセルアレイ隣接領域105と、メモリセルアレイ領域100内に層間絶縁膜を介して設けられる複数の第1導電線SLと、セルアレイ隣接領域105内に層間絶縁膜を介して設けられる複数の第2導電線M2とを具備し、複数の第2導電線M2はその配線内にスリット50が形成されていることを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】ロウデコーダ内のリーク電流を低減でき、メモリセルの誤消去の発生の防止に対して有利な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、複数のブロックにより構成されるメモリセルアレイと、電流経路の一端が前記複数のワード線に電気的に接続された複数の転送トランジスタをそれぞれ有し、前記複数のブロックに対応して設けられ、ワード線方向に隣接して配置される第1,第2ブロック選択回路RDn,RDn+3を備えたロウデコーダ22とを具備し、前記転送トランジスタの電流経路の一端である拡散層Sは、前記第1,第2ブロック選択回路内でそれぞれ対向するように配置され、ワード線方向の前記第1,第2ブロック選択回路に隣接する前記拡散層間の幅W2は、ワード線方向の同一の前記第1,第2ブロック選択回路内に隣接する前記拡散層間の幅W1より大きく配置される(W2>W1)。

(もっと読む)

1 - 20 / 27

[ Back to top ]