Fターム[5F083LA29]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | チップレイアウト (365) | 周辺回路が中央部に配置 (38)

Fターム[5F083LA29]に分類される特許

1 - 20 / 38

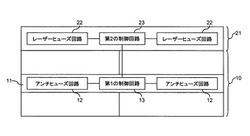

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

抵抗変化型メモリデバイスおよびその駆動方法

【課題】リファレンスセルの抵抗状態に応じて、読み出し電流を設定する構成で、誤書き込みによる抵抗の変化が発生することなく、より信頼性の高いリファレンス電流を得ることが可能な抵抗変化型メモリデバイスおよびその駆動方法を提供する。

【解決手段】素子両端に極性の異なる信号を印加することで可逆的に記憶素子の抵抗値が変化するメインメモリセルを含むメモリアレイ部と、素子両端に極性の異なる信号を印加することで可逆的に抵抗値が変化する記憶素子を含み、メインメモリセルのデータを識別するために必要な参照電流を発生させるリファレンスセルを含むリファレンスセル部と、を有し、リファレンスセルの抵抗状態に応じた参照電流の印加電流の向きが設定されている。

(もっと読む)

半導体装置の製造方法

【課題】非晶質炭素膜を用いて形成する電極のアスペクト比を増大させる。

【解決手段】半導体装置の製造方法は、半導体基板上に第1非晶質炭素膜を形成し、周辺回路領域の第1非晶質炭素膜を除去してメモリセル領域の第1非晶質炭素膜を第2非晶質炭素膜とし、第2非晶質炭素膜を覆う第1シリコン酸化膜を基板全面に形成し、第2非晶質炭素膜上の第1シリコン酸化膜を除去して周辺回路領域の第1シリコン酸化膜を第2シリコン酸化膜とし、第2非晶質炭素膜と第2シリコン酸化膜を覆う第1絶縁膜を形成し、第1絶縁膜に第1開口を形成し、第1開口を埋め込む第2絶縁膜を形成し、第2絶縁膜に第2開口を形成し、第2開口と第1開口が重なる位置に露出する第2非晶質炭素膜にホールを形成し、ホール内に下部電極を形成し、第2絶縁膜を除去して第1開口内に第2非晶質炭素膜を露出させ、露出した第2非晶質炭素膜を全て除去する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

記憶装置

【課題】記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

【解決手段】基板に設けられた駆動回路と、駆動回路上に設けられ、駆動回路によって駆動される複数のメモリセルアレイと、を有し、複数のメモリセルアレイはそれぞれ複数のメモリセルを有し、複数のメモリセルはそれぞれ、酸化物半導体層と重畳する第1のゲート電極と、を有する第1のトランジスタと、ソース電極又はドレイン電極と、第1のゲート絶縁層と、導電層と、を有する容量素子と、を有し、複数のメモリセルアレイは重ねて配置される。こうして、記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

(もっと読む)

不揮発性半導体記憶装置及び不揮発性半導体記憶装置の製造方法

【課題】不揮発性半導体記憶装置の製造プロセスを大幅に変更することなく、電極間のショートを避けることができる、不揮発性半導体記憶装置及び不揮発性半導体記憶装置の製造方法を提供するものである。

【解決手段】不揮発性半導体記憶装置は、半導体基板上に形成された第1の絶縁膜を有し、且つ、第1の絶縁膜上に複数の周辺トランジスタが形成された、周辺回路領域と、半導体基板上に形成された、第1の絶縁膜と厚さが異なる第2の絶縁膜を有し、且つ、第2の絶縁膜上に複数のメモリセルトランジスタが形成された、セルアレイ領域と、半導体基板に埋め込まれた状態に形成された、周辺回路領域とセルアレイ領域とを分離する、上面が面一に構成された、第1の素子分離絶縁膜と、これらの上部に全体的に形成された層間絶縁膜と、を備える。

(もっと読む)

半導体装置

【課題】 レイアウト面積の増加を抑制しつつ、更なる高速動作を可能にする半導体装置を提供する。

【解決手段】

半導体装置は、半導体基板141と、半導体基板中に埋め込まれ、かつ第1の方向に延伸して形成された第1のローカルビット線501と、半導体基板上に形成された第1の絶縁層142と、第1の絶縁層上に形成された第1のグローバルビット線GBLと、第1の絶縁層中に形成され、第1のローカルビット線の一端と第1のグローバルビット線とを接続する第1の経路502と、第1の絶縁層中に形成され、第1のローカルビット線の他端と第1のグローバルビット線とを接続する第2の経路503とを備えている。

(もっと読む)

半導体メモリ装置及びそれを含む半導体パッケージ

【課題】高性能及び低電力が要求される多様な装置及びシステムを支援できる、マルチチャネルインタフェース方式のワイド入出力を有する半導体メモリ装置及びそれを含む半導体パッケージを提供する。

【解決手段】本発明の一実施形態に係る半導体メモリ装置は、複数のメモリセルアレイを含む半導体ダイからなり、半導体ダイの中央部に形成される入出力バンプパッド部を含む。入出力バンプパッド部は、前記それぞれのメモリセルアレイを外部装置と独立的に接続するための複数のチャネルを提供する。マルチチャネル方式のワイド入出力インタフェースを通じて動作周波数の減少及びバンド幅の拡張を図ることによって、高性能の装置及びシステムを支援すると同時に電力消耗を減少させる。

(もっと読む)

半導体装置、そのプローブテスト方法及びその製造方法

【課題】本発明は、プローブテストが行われてから、プローブテストのためのロジック回路を除去し得る半導体装置を提供する。

【解決手段】本発明の半導体製造装置は、第1のチップ;前記第1のチップの周囲に配置されるスクライブレーン;及び、前記第1のチップのプローブテストを行うプローブテストロジック回路を含み、前記プローブテストロジック回路は、前記スクライブレーンの一部分に位置することを特徴とする。

(もっと読む)

NAND型フラッシュメモリ

【課題】チップ内のメモリプレーン数が増えてもロウデコーダ数の増加を抑える。

【解決手段】NAND型フラッシュメモリは、第1及び第2メモリプレーン11A,11B間に配置され、第1NANDブロックBKi内の第1ワード線WL0〜WLn及び第3NANDブロックBKi内の第2ワード線WL0〜WLnに共通接続される第1転送トランジスタ18と、第1メモリプレーン11Aの第2メモリプレーン11B側とは反対側の第1端に配置され、第2NANDブロックBK(i+1)内の第3ワード線WL0〜WLnに接続される第2転送トランジスタ18と、第2メモリプレーン11Bの第1メモリプレーン11A側とは反対側の第2端に配置され、第4NANDブロックBK(i+1)内の第4ワード線WL0〜WLnに接続される第3転送トランジスタ18とを備える。

(もっと読む)

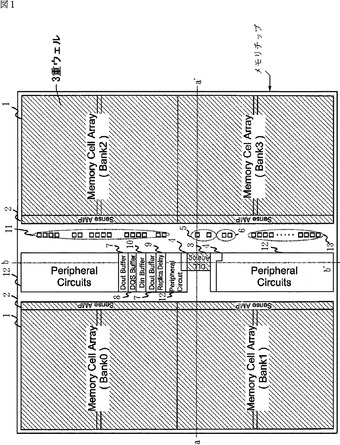

ダイナミック型半導体記憶装置

【課題】安定したクロック発生動作、高精度で低消費電力を実現しDLLを備える。

【解決手段】内部クロック信号を生成するDLL回路、内部クロック信号で動作を制御される周辺回路とメモリセルアレイを含む。第1電源電圧を供給するために同期回路に接続された第1電源パッド、第1電源電圧より低い第2電源電圧を供給するために同期回路に接続された第2電源パッド、周辺回路とメモリセルアレイに第3電源電圧を供給するための第3電源パッド、周辺回路とメモリバンクに第3電源電圧より低い第4電源電圧を供給する第4電源パッドを含む。複数のメモリセルアレイは第1領域と第2領域に分割して配置される。複数の周辺回路は第1領域と第2領域の間の第3領域に配置される。第1、2、3,4電源パッドは第1領域と前記第3領域の間の第4領域に配置されている。

【選択図】図1  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、ポケット注入によるロールオフ現象の抑制と共に、セルキャパシタにおいて電荷を長期間保持できるようにすること。

【解決手段】チャネル領域におけるシリコン基板30の上にゲート絶縁膜40を形成する工程と、ゲート絶縁膜40上に第1の方向D1に延在する第1のワード線45aと第1の方向D1に交差する第2の方向D2に延在する第2のワード線45aとを形成する工程と、第1のワード線45aの上面の一部を覆うレジストパターン47を形成する工程と、レジストパターン47をマスクに使用し、基板表面の垂直方向からビットコンタクト領域Iに傾いた方向であって、且つ、第1の方向D1と第2の方向D2の両方に対して斜めの方向から、チャンネル領域と同導電型の不純物をビットコンタクト領域I側の活性領域にイオン注入する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置及びその製造方法

【課題】追加工程なくフューズ下に配線等を配置可能な半導体装置及びその製造方法を提供する。

【解決手段】この半導体装置は、絶縁層に設けられた複数の第1キャパシタ孔52と、第1キャパシタ孔52に形成された容量素子Cと、容量素子Cと結合するトランジスタTrとからなるDRAMセルと、絶縁層に設けられた複数の第2キャパシタ孔40と、第2キャパシタ孔40の間に形成されるフューズ素子(31、51)と、を備えている。

(もっと読む)

半導体装置

【課題】基板上に複数のメモリチップとコントローラチップを搭載した半導体装置において、チップ間の配線を短縮するチップレイアウトを実現して性能向上を実現することができる半導体装置を提供する。

【解決手段】本発明の実施の形態に係る半導体装置は、半導体基板と、一方の表面上の中央部に複数のパッドが形成され、前記半導体基板上に搭載されたメモリチップと、前記メモリチップの外形サイズより外形サイズが小さく、一方の表面上の周辺部に複数のパッドが形成され、前記メモリチップの一方の表面上の中央部を除く一部分に搭載されたコントローラチップと、前記メモリチップの一方の表面上の中央部に形成された複数のパッドと前記コントローラチップの一方の表面上の周辺部に形成された複数のパッドとを電気的に接続する複数の金属ワイヤと、を備える。

(もっと読む)

強誘電体メモリ装置およびその動作方法

【課題】リフレッシュペナルティーなく各メモリサイクル間にランダムなアクセスが可能な強誘電体メモリ装置およびその動作方法

【解決手段】ビット線BLとワード線WLおよびプレート線PLの交差部に配置され強誘電体キャパシタCFとメモリセルトランジスタQMからなる強誘電体メモリセル60と、ビット線とビット線容量制御線BLCの交差部に配置され、負荷容量CLと負荷容量調整トランジスタQLからなる負荷容量調整セル64とを備える強誘電体メモリからなるメモリセルアレイを備える複数のメモリバンク18,180,181,…,1862,1863と、メモリバンクのデータをコピーするキャッシュバンク20と、複数のメモリバンクおよびキャッシュバンク20のアクセス及びリフレッシュをするためのメモリバンク/キャッシュ制御シーケンサ32と備え、リフレッシュ動作の遅延なく各メモリサイクル間に強誘電体メモリへのランダムなアクセス制御が可能である。

(もっと読む)

三次元積層不揮発性半導体メモリ

【課題】BiCSメモリの周辺回路の面積増大を抑える。

【解決手段】本発明の例に係る三次元積層不揮発性半導体メモリは、第一方向に並んで配置される第一及び第二ブロックBK<i>, BK<i+1>から構成されるメモリセルアレイと、メモリセルアレイの第一方向に直交する第二方向の一端に配置されるドライバ33Lとを備える。第一ブロックBK<i>内の複数の第一セレクトゲート線SGD<0>, …SGD<5>と第二ブロックBK<i+1>内の複数の第一セレクトゲート線SGD<0>, …SGD<5>とは、メモリセルアレイの第二方向の一端において一対一に共通接続されたうえでドライバ33Lに接続される。

(もっと読む)

半導体記憶装置

【課題】DRAMにおいて微細化を進め、さらにメモリセルに縦型のMOSトランジスタを使用すると、隣接ワード線間の寄生容量が増加する。DRAMを安定動作させるためには、この寄生容量によって発生するカップリングノイズを低減する必要がある。また、ワード線間のカップリングノイズを低減する際にチップサイズの増加を抑制する必要がある。

【解決手段】ワード線(上層ワード線UWL)の配線順序を入れ換えるツイスト接続部WCA1をワード線のほぼ中央部に設け、そのツイスト接続部WCA1の下部領域に、ワード線の非選択状態の電位レベルを出力するレベル安定化回路TRを配置する。

(もっと読む)

不揮発性半導体記憶装置

【課題】負領域に存在する複数の閾値分布を判別する読み出し方式を提案する。

【解決手段】本発明の例に係る不揮発性半導体記憶装置は、半導体領域と、半導体領域内に形成され、第1及び第2拡散層、電荷蓄積層及びコントロールゲート電極を有するセルトランジスタと、第1拡散層に接続されるビット線と、第2拡散層に接続されるソース線と、半導体領域、ビット線、及び、ソース線を制御する制御回路とを備える。制御回路は、ビット線を第1電位にプリチャージした後にビット線をフローティングにする手段と、ビット線がフローティングの状態で半導体領域及びソース線に第2電位を与えてビット線を第1電位から第3電位に変化させる手段と、ビット線を第3電位にした後にセルトランジスタのデータをビット線に読み出す手段とから構成される。

(もっと読む)

半導体記憶装置

【課題】チップサイズを削減することができ、かつ、安定した動作を得ることのできる、半導体記憶装置を提供する。

【解決手段】情報として電荷が蓄積される複数のメモリセルを備える、アレイ状に配置された複数のマット10と、一端が外部電源から供給される電圧を降圧または昇圧する内部電源に共通に接続された複数の電源線30とを有する半導体記憶装置であって、各電源線30は、複数のマット10が形成された領域上に、一定方向に延伸するように配線されており、各電源線30の他端が端マット10a上で共通に接続されている。

(もっと読む)

半導体記憶装置

【課題】チップの中央に周辺回路が集中配置されたフロアプランを有する半導体記憶装置において、入出力データ幅による回路特性の変化を抑制する。

【解決手段】バス領域121,122と、中心線Aに沿って配置された第3のバス領域123と、辺101とバス領域121との間に配置されたセル領域111と、辺102とバス領域122との間に配置されたセル領域112と、バス領域121,122間に配置され、バス領域123から見て辺103,104側にそれぞれ配置されたセル領域113,114と、バス領域123に沿って配置されたデータ入出力パッド列DQ0〜DQ15とを備える。本発明によれば、入出力データ幅を変更してもデータ入出力バスの遠近端差はほとんど変化しない。したがって、選択された入出力データ幅によって特性が変化しにくく、優れた回路特性を得ることが可能となる。

(もっと読む)

1 - 20 / 38

[ Back to top ]