Fターム[5F083NA05]の内容

Fターム[5F083NA05]に分類される特許

1 - 20 / 54

半導体装置

【課題】素子分離すべき領域にダミーの補助ゲートを配置することで、電気的に分離する方法(FS方式)を採用しつつ、補助ゲートに給電するための新たな専用の配線を設けることによるチップの縮小化の弊害を解消する半導体装置を提供する。

【解決手段】半導体基板2に埋め込み形成された素子分離膜によって、複数のセル部活性領域が区画された半導体装置1であって、半導体基板2に設けられたゲート溝内に、ゲート絶縁膜を介して形成された補助セルゲート28aが、半導体基板2と電気的に接続されている。

(もっと読む)

半導体メモリ

【課題】素子間リークを低減できる半導体メモリを提供する。

【解決手段】本実施形態の半導体装置は、第1のゲート絶縁膜上の電荷蓄積層と、第1の絶縁体を介して電荷蓄積層上に設けられる制御ゲート電極とを含むメモリセルと、アクティブ領域AAH上の第2のゲート絶縁膜20Hと、第2のゲート絶縁膜上の第1の電極層21Hと、を含むトランジスタHTと、素子分離絶縁膜15H上に設けられるシールドゲート電極SIGと、を有する。シールドゲート電極SIGの底部は、素子分離絶縁膜15Hの最も高い上面より半導体基板10の底部側に位置している。

(もっと読む)

半導体装置の製造方法、並びにデータ処理システム

【課題】チャネル領域を拡大することが可能な半導体装置の製造方法を提供する。

【解決手段】素子分離用の溝部3を形成した後、素子分離絶縁膜4として、当該溝部3に埋め込まれた状態で基板2の面上を覆うシリコン酸化膜26,31を形成する工程と、シリコン酸化膜26,31上に少なくとも埋め込みゲート用の溝部10を形成する位置に開口部を有するマスクパターンを形成する工程と、マスクパターンの開口部を通してシリコン酸化膜31を異方性エッチングにより選択的に除去することによって、当該シリコン酸化膜31に第1の溝部9と同じ幅及び深さとなる第2の溝部10を形成する工程と、第2の溝部10の底面及び側面に位置するシリコン酸化膜26,31を等方性エッチングにより選択的に除去することによって、当該第2の溝部10を活性領域6に形成される第1の溝部9よりも深く、且つ、第1の溝部9よりも大きい幅とする工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】素子分離用ゲート電極のみのしきい値電圧を高くすることができ、素子分離用ゲート電極の底部にチャネルが形成されない半導体装置を提供する。

【解決手段】半導体基板1に形成された複数の活性領域と、これら活性領域同士を区画する素子分離領域と、活性領域内を複数の素子領域に区画する第1素子分離用トレンチ32Aと、隣接する第1素子分離用トレンチ32A間に設けられ、第1素子分離用トレンチ32Aの深さよりも浅く形成されたゲートトレンチ31Aと、絶縁膜25を介して第1素子分離用トレンチ32A内に形成された素子分離用電極32と、ゲート絶縁膜26Aを介してゲートトレンチ31A内に形成されたゲート電極31と、を具備してなり、素子分離用電極32底部に成膜されている絶縁膜25の膜厚が、ゲート電極31の底部に成膜されているゲート絶縁膜26Aの膜厚よりも厚いことを特徴とする。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】隣接セル間干渉を抑制した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1メモリストリングと、ソースコンタクトと、第2メモリストリングと、シールド導電層と、を備えた不揮発性半導体記憶装置を提供する。第1メモリストリングは、第1軸に沿って並ぶ第1メモリセル及び第2メモリセルを含む。ソースコンタクトは、第1メモリストリングのソース側の端に設けられる。第2メモリストリングは、第1軸に対して直交する第2軸に沿って第1メモリセルと並ぶ第3メモリセルを含み、第1軸に沿って延在する。シールド導電層は、第1メモリストリングと第2メモリストリングとの間において第1軸に沿って延在し、ソースコンタクトと電気的に接続される。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法に関し、工程マージンを向上させる。

【解決手段】半導体素子は、半導体基板10に備えられるメインゲート20及び素子分離構造、前記素子分離構造の上部に備えられる分離パターン40及び前記分離パターンの両端に備えられるコンタクトプラグ54を含む。格納電極コンタクトと活性領域との間のフルオーバーラップを提供し、食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させる。

(もっと読む)

半導体装置及びその製造方法

【課題】活性領域とビット線コンタクトとの間の接触面積が大きく、コンタクト抵抗の低下が図られた半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置100は、基板1に形成された第1の方向に延在する第1の溝4と、第1の溝4の下部を埋めこんで形成された第2の絶縁層6と、基板1に形成された第1の方向に直交する第2の方向に延在する複数の第2の溝と、第2の溝の下部を埋めこんで第2の溝内に形成されたワード線と、第1の溝4と第2の溝とによって基板1内に区画して形成され、基板1に垂直に立設すると共に、上部に拡散領域23aを有する半導体ピラー1dと、第1の方向に並ぶ所定数ごとの半導体ピラー1dにその上部の側面を介して拡散領域23aに接続するビット線コンタクト22aと、ビット線コンタクト22aに接続するビット線26と、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】埋め込みゲート型トランジスタの電流駆動能力の低下を防止可能な半導体装置を提供する。

【解決手段】本発明の半導体装置100は、半導体基板1において素子分離領域5によって複数の活性領域50が区画されると共に、前記半導体基板1内に埋め込まれたワード線8を有する半導体装置100であって、前記ワード線8は、第一の溝部8a内にゲート絶縁膜7aを介して埋め込まれた導電層8bからなり、前記素子分離領域5は、前記第一の溝部8aよりも幅の狭い第二の溝部5aに前記ゲート絶縁膜7bを介して埋め込まれた前記導電層5bからなることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】活性領域をライン上に形成することで、コンタクト領域のばらつきを抑制し、リセスゲート電極を用いて隣接するトランジスタ間の分離を行う構造を提供する。

【解決手段】半導体基板中に第1の方向に延在して形成される素子分離領域で分離された活性領域と、第1の方向と交差する第2の方向に延在し、素子分離領域及び活性領域に連通する溝内に形成されたリセスゲート電極と。リセスゲート電極で分断された活性領域であって、リセスゲート電極の底面より浅い領域に形成されるMOSトランジスタのソース/ドレイン領域とを備えた半導体装置であって、リセスゲート電極は、MOSトランジスタのゲート電極を構成する制御ゲート電極162tと、第1の方向に隣接するMOSトランジスタを素子分離する補助ゲート電極162iで構成される。

(もっと読む)

半導体装置の製造方法

【課題】隣接する活性領域の間で横方向に成長するシリコン膜が連結されることを防ぎつつ、活性領域上に十分な厚みのシリコン膜を形成可能とした半導体装置の製造方法を提供する。

【解決手段】ゲート電極6aを挟んだ両側の活性領域5上に第1のシリコン膜12aを選択的にエピタキシャル成長させる工程と、複数のワード配線層WLの各間に第1のシリコン膜12aを覆うのに十分な厚みでマスク絶縁膜を埋め込んだ後、このマスク絶縁膜を第1のシリコン膜12aの表面が露出するまでエッチングにより除去する工程と、第1のシリコン膜12a上に第2のシリコン膜12bを選択的にエピタキシャル成長させる工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】隣接する活性領域の間で電気的な短絡(ショート)が発生することを防止した半導体装置の製造方法を提供する。

【解決手段】ゲート電極6aを挟んだ両側の活性領域5上にシリコン膜12を選択的にエピタキシャル成長させる工程と、複数のワード配線層WLの各間に反射防止膜を埋め込んで平坦化した後、この平坦化した面上に、互いに隣接する活性領域5の各間において第1の方向Xに延在する開口部を有するマスクパターンを形成する工程と、マスクパターンの開口部から露出した部分を半導体基板の表面が露出するまでドライエッチングにより除去する工程とを含む。これにより、互いに隣接する活性領域5の間でシリコン膜12が横方向にエピタキシャル成長することによって連結された部分を、ドライエッチングにより切断し除去することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】フィールドシールド用トランジスタのゲート長を、背景技術と比べて長く取れるようにする。

【解決手段】半導体装置1は、底面並びに第1及び第2の側面を有するセル用ゲートトレンチ10と、トレンチ10より幅の狭いフィールドシールド用ゲートトレンチ11と、トレンチ10とトレンチ11の間に設けられた上部拡散層と、トレンチ10を挟んで第1の上部拡散層の反対側に設けられた第2の上部拡散層と、トレンチ11を挟んで第1の上部拡散層の反対側に設けられた第3の上部拡散層と、トレンチ10の底面に設けられた下部拡散層と、それぞれ第1及び第2の上部拡散層と電気的に接続された第1及び第2の記憶素子と、下部拡散層と電気的に接続されたビット線BLと、ゲート絶縁膜を介して第1及び第2の側面をそれぞれ覆うワード線WLと、ゲート絶縁膜を介してトレンチ11に埋め込まれたフィールドシールド用ゲート電極DWLとを備える。

(もっと読む)

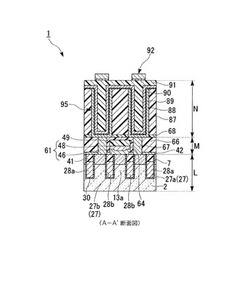

半導体装置及びその製造方法

【課題】本発明は、コンタクトプラグと埋め込み型のゲート電極との間に配置される絶縁膜の厚さを十分に確保可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート絶縁膜16を介して、半導体基板11に形成された凹部14の凹部14の一部を埋め込むゲート電極41と、ゲート電極41の上端面41aを覆うように凹部14内を埋め込む絶縁膜18と、凹部14の一方の側面14a側に位置する半導体基板11の主面11aに形成された不純物拡散領域43と、不純物拡散領域43の上面43aを覆うシリコン層21と、半導体基板11の主面11aに形成された第1及び第2の層間絶縁膜23,31に内設され、シリコン層21の上面21aと接触し、かつ下端34bがシリコン層21の上面21aと絶縁膜18の上面18aとの間に配置されたコンタクトプラグ34と、を備える。

(もっと読む)

抵抗変化型半導体メモリ

【課題】セル面積の縮小及び動作特性の向上に優れたレイアウトを提案する。

【解決手段】実施形態によれば、抵抗変化型半導体メモリは、第1方向に並ぶ第1乃至第4メモリセルを備える。第1乃至第4メモリセルの各々は、第1ソース/ドレインが第1方向に延びる第1ビット線BLA1に接続され、ゲートが第2方向に延びるワード線WL1, WL2, WL3, WL4に接続されるセルトランジスタT11, T12, T13, T14と、一端がセルトランジスタT11, T12, T13, T14の第2ソース/ドレインに接続され、他端が第2方向に延びる第2ビット線BLB1, BLB2, BLB3, BLB4に接続される抵抗性記憶素子M11, M12, M13, M14とを有する。第1及び第2メモリセル内の第1ソース/ドレインは、共有化され、第3及び第4メモリセル内の第1ソース/ドレインは、共有化される。

(もっと読む)

限られたチャージ拡散を有するチャージトラップメモリ

【課題】隣接メモリセルへの漏洩電流を減らすフラッシュメモリ、特にチャージトラップメモリおよびそれを形成するプロセスフローの提供。

【解決手段】セルチャンネル620を含む半導体線が、STI領域120上に形成される。セルチャンネルは、トンネル酸化物層621、トラッピング誘電体層623、およびブロッキング誘電体層628を含む活性誘電体スタックで覆われる。結果として得られるセルチャンネルを分離するトレンチ625は、伝導層460で少なくとも部分的に充填され得る。活性誘電体層および/または伝導層の部分は、セルチャンネルの下、たとえば、セルチャンネルおよびSTI領域の間の界面695の下に位置し得る。そのような構成は、活性誘電体スタックおよび/または半導体層がセルチャンネルの下に位置しない構成に比べて、あるセルチャンネルから隣接セルチャンネルに拡散する荷電粒子670に対して経路長の増大をもたらす。

(もっと読む)

半導体装置及びその製造方法

【課題】接合リーク電流が低減されるとともに、セル容量への書き込み・読み出しに十分な電流駆動能力を確保することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1に形成された複数の埋め込みゲート型MOSトランジスタ2を有し、半導体基板1には素子分離領域と活性領域とが形成されており、ゲートトレンチの内部に形成され、少なくとも一部がワード線として設けられるとともに、その他の残部が、活性領域を複数の素子領域に分離する素子分離として設けられる埋め込みゲート電極31A、31Bと、ソース・ドレイン拡散層15、45とが備えられ、埋め込みゲート電極31A、31Bは、上部電極31aと下部電極31bとの積層構造とされ、且つ、半導体基板1の上面側のソース・ドレイン拡散層15、45側に配置される上部電極31aが、下部電極31bに比べて、仕事関数の低いゲート材料からなる。

(もっと読む)

半導体装置の製造方法

【課題】DRAM素子のような半導体装置において、半導体基板の溝部におけるゲート電極の埋設状態が良好となり、配線抵抗が低減され、素子特性に優れた半導体装置の製造方法を提供する。

【解決手段】シリコン基板1の表面にゲート電極溝13を形成する工程と、ゲート電極溝13の内面に第1のバリア膜16aを形成する工程と、第1のバリア膜16aをエッチバックして、ゲート電極溝13の底面に第1のバリア膜16aの一部を残存させながら除去する工程と、ゲート電極溝13の内面と残存した第1のバリア膜16aの表面に第2のバリア膜16bを形成する工程と、第2のバリア膜16aの表面にタングステン膜を形成する工程と、このタングステン膜及び第2のバリア膜16bをエッチバックしてゲート電極溝13内にそれぞれ一部を残存させながら各膜を一括除去する工程と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】配線層の加工マージンが大きく、微細化に適した半導体装置の製造方法を提供する。

【解決手段】半導体基板1にゲート電極溝を形成する工程と、ゲート電極溝の内壁面にゲート絶縁膜15を形成する工程と、ゲート電極溝の底部に埋め込みゲート電極23Aを形成する工程と、埋め込みゲート電極23Aの上面を覆うようにゲート電極溝の内部に絶縁膜を埋め込んだ後、エッチバックして当該ゲート電極溝の上部にキャップ絶縁膜22を形成する工程と、半導体基板1の上面に層間絶縁膜24を形成する工程と、層間絶縁膜24にビットコンタクト開口部を形成する工程と、を備え、半導体基板1の上面に層間絶縁膜24を形成する工程が、半導体基板1の上面とキャップ絶縁膜22の上面との間に生じた段差を埋め込むように層間絶縁膜24を成膜するとともに当該層間絶縁膜24の上面を平坦とすることを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明はビット配線と半導体基板上の不純物拡散層とのコンタクト抵抗を低減した構造の提供を目的とする。

【解決手段】本発明は、半導体基板の一面に形成されたトレンチ溝内に、ゲート絶縁膜を介しゲート電極を含む埋込ワード線とその上に位置する埋込絶縁膜とが埋め込まれ、前記トレンチ溝に隣接する半導体基板一面の表面領域に不純物拡散層が形成され、前記不純物拡散層が形成された領域上にビット配線が形成されるとともに、前記不純物拡散層に接続されたビット配線の少なくとも底部側が、不純物をドープした不純物ドープ型のポリシリコンに更に不純物イオンを打ち込みしてなる注入ポリシリコン膜からなることを特徴とする。

(もっと読む)

半導体記憶装置

【課題】メモリセルのコントロールゲートとして機能する電極層の電位が他領域に影響するのを抑制することができる半導体記憶装置を提供する。

【解決手段】本発明の半導体記憶装置は、半導体基板11上におけるメモリセル領域及び周辺回路領域にわたって設けられ複数の電極層WL1〜WL5と複数の絶縁層24とが交互に積層された積層体と、メモリセル領域における積層体を貫通して形成されたホールの内部に設けられ積層体の積層方向に延びる半導体層21と、半導体層21と電極層WL1〜WL5との間に設けられた電荷蓄積層17と、周辺回路領域における積層体の下に設けられ、電極層WL1〜WL5に電位を転送する転送トランジスタと、転送トランジスタと最下層の電極層WL1との間に設けられ、転送トランジスタの拡散層の電位に応じたシールド電位が与えられる下部シールド配線層SL1とを備えている。

(もっと読む)

1 - 20 / 54

[ Back to top ]