Fターム[5F083PR07]の内容

Fターム[5F083PR07]に分類される特許

81 - 100 / 734

半導体装置の製造方法

【課題】第1MISFETのゲート電極と第2MISFETのゲート電極とを別工程で形成する半導体装置の製造技術において、第1MISFETと第2MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板20上にゲート絶縁膜26、電荷蓄積膜27、絶縁膜28、ポリシリコン膜29、酸化シリコン膜30、窒化シリコン膜31およびキャップ絶縁膜32からなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して、低耐圧MISFET形成領域および高耐圧MISFET形成領域に形成されている積層膜を除去する。その後、半導体基板20上にゲート絶縁膜34、36、ポリシリコン膜37およびキャップ絶縁膜38を形成する。そして、低耐圧MISFET形成領域および高耐圧MISFET形成領域にゲート電極を形成した後、メモリセル形成領域にゲート電極を形成する。

(もっと読む)

半導体素子の形成方法

【課題】相互接続領域の具現が困難なパッドレイアウトを具現化し、オーバレイマージンを増大できる半導体素子の形成方法を提供する。

【解決手段】半導体基板に被食刻層、第1のハードマスク物質層、第1の分割パターン物質層及び第2のハードマスク物質層を形成して選択食刻し第2のハードマスクパターンを形成し、これをマスクとし第1の分割パターン物質層を食刻し第1の分割パターンを形成する。第1のハードマスク物質層の上部にスペーサ物質層及び第2の分割パターン物質層を形成し、第1の分割パターンが現われるまでスペーサ物質層及び第2の分割パターン物質層を部分食刻しスペーサ物質層を露出させ、複数の第1の分割パターン間に第2の分割パターンを形成し、第1、第2の分割パターンをマスクとしスペーサ物質層及び第1のハードマスク物質層を食刻し第1のハードマスクパターンを形成し、これをマスクとし被食刻層を食刻し微細パターンを形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】記憶密度を高めた不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1、2積層体、第1、2半導体ピラー、及び分断絶縁層を備えた不揮発性半導体記憶装置が提供される。第1、2積層体は、第1軸に沿って積層された複数の第1、2電極膜と、第1、2電極膜の間の第1、2電極間絶縁膜と、を含み、第1軸に沿う第1、2貫通ホールが設けられる。第2積層体は、第1軸と直交する第2軸に沿って第1積層体と並ぶ。第1、2半導体ピラーは第1、2貫通ホールに埋め込まれる。分断絶縁層は第1、2電極膜を分断する。第1、2貫通ホールの分断絶縁層の側の側面は、第1、2軸に直交する第3軸を含み第1軸を含む平面と平行な部分を有する。

(もっと読む)

配線の形成方法

【課題】側壁転写プロセスを用いて被加工膜を形成する場合に、従来に比して工程数を減少させ、製造コストの上昇を抑えることができる配線の形成方法を提供する。

【解決手段】実施形態によれば、まず、被加工膜11上にマスク膜12と所定の形状のパターンの芯材膜13とを形成し、その上にスペーサ膜14を形成する。ついで、スペーサ膜14を後のエッチング時のマスクとして残す位置から所定の距離の範囲にスペーサ膜14が位置するようにダミーのスペーサ膜143と、芯材膜13の側壁に側壁パターンとをリソグラフィ技術とエッチング技術とを用いて形成する。その後、芯材膜13を除去し、ダミーパターンが除去されるまでスペーサ膜14をエッチングし、所定の範囲に他のスペーサ膜14が存在しない位置にパターン変質部21を生成する。そして、パターン変質部21を除去し、スペーサ膜14をマスクとしてマスク膜12と被加工膜11をエッチングする。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】コンタクトと素子領域間にかかる電界を緩和し絶縁破壊を防ぐ。

【解決手段】実施形態の半導体装置は、基板上第1方向に延伸し並列し高さが同じ第1〜4分離、第1、2分離間の低い第1領域、高さが等しい第2、3分離間の第2領域、第3、4分離間の第3領域、第1領域上面、第1分離の第2分離に対向した側面および上面の一部、第2分離の第1分離に対向した側面および上面の一部に接する第1電極15−1、その第2方向で第3領域上面、第3分離の第4分離に対向した側面および上面の一部、第4分離の第3分離に対向した側面および上面の一部に接する第2電極15−2を有す。半導体装置は、第1電極の第2方向とは異なる方向に位置し第2領域上面、第2分離の第3分離に対向した側面および上面の一部、第3分離の第2分離に対向した側面および上面の一部に接する第3電極を有す。

(もっと読む)

半導体装置の製造方法

【課題】露光パターンのピッチの1/4のピッチのパターンを形成する方法でありながら、形成されたパターンの本数を4の倍数以外の数にする。

【解決手段】第2のパターンおよび第2のマスクパターンを覆うと共に第1の膜の上に第3の膜を形成する工程と、第3の膜をエッチバック処理することにより、第2のパターンおよび第2のマスクパターンの側壁に第1の側壁ラインパターンおよび第1の側壁マスクパターンをそれぞれ形成する工程と、第2のマスクパターンおよび第1の側壁マスクパターンを覆うように第3のマスクパターンを形成する工程と、第3のマスクパターンをマスクとし、第2のパターンを第1の側壁ラインパターンに対して選択的にエッチングして除去した後、第3のマスクパターンを除去する工程とを備えた。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、ハードマスクに対して、2枚のレジスト膜を用いて、ライン&スペースパターンおよび隣接ゲート電極間切断領域パターンのパターニングを実行し、パターニングされたハードマスクを用いて、ゲート積層膜のエッチングを実行するものである。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体記憶装置およびその作製方法

【課題】半導体記憶装置におけるデータ保持のためのリフレッシュ動作の回数を低減し、消費電力の小さい半導体記憶装置を提供する。また、三次元の形状を適用することで、集積度を高めても短チャネル効果の影響が低減され、かつ従来に比べてフォトリソグラフィ工程数の増加を抑えた半導体記憶装置を提供する。

【解決手段】溝部の設けられた絶縁膜103と、溝部を挟んで離間した一対の電極116と、溝部の側面および底面と接し、溝部の深さよりも厚さの薄い、一対の電極116と接する酸化物半導体膜106と、酸化物半導体膜106を覆うゲート絶縁膜112と、ゲート絶縁膜112を介して酸化物半導体膜106と重畳して設けられたゲート電極112と、を有するトランジスタ150と、キャパシタ160と、を有する半導体記憶装置である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量コンタクトプラグと半導体基板の活性領域との間の重ねマージンを十分に確保して、低抵抗且つ接続信頼性の高い半導体装置を提供する。

【解決手段】埋め込みゲート電極19A及びキャップ絶縁膜20Aと、活性領域1Aの上面に設けられたビットコンタクト27A及びビット線27と、半導体基板1上に設けられた絶縁層32,40と、第1容量コンタクトプラグ39Aと、を備え、第1容量コンタクトプラグ39Aは、柱状部39aとこの柱状部39aの下方に設けられた板状部39bとを有し、板状部39bの底面と、素子分離領域及びキャップ絶縁膜20Aによって区画された活性領域1Aの表面1a,1cとが全面で接触するように設けられていることを特徴とする半導体装置を選択する。

(もっと読む)

半導体記憶装置

【課題】総工程数を低減することができ、コストを低廉なものにする半導体記憶装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体記憶装置10は、半導体基板13と、第1不純物領域17と、第2不純物領域15と、第1不純物領域17と第2不純物領域15との間に形成されたチャネル領域75と、チャネル領域75が位置する半導体基板13の主表面上のうち、第1不純物領域17側の主表面上に形成された第1ゲート42と、チャネル領域75が位置する半導体基板13の主表面上にうち、第2不純物領域側15の主表面上に第2絶縁膜44を介して形成された第2ゲート45と、第1ゲート45に対して第2ゲート42と反対側に位置する半導体基板の主表面上に位置し、第1ゲート42の側面上に形成された第3絶縁膜46と、第3絶縁膜46とその直下に位置する半導体基板13との界面が、第2絶縁膜44とその直下に位置する半導体基板の主表面との界面より上方に位置する。

(もっと読む)

記憶装置およびその製造方法

【課題】メモリセルの構造を最適化することにより、更なる微細化を可能にする記憶装置を提供する。

【解決手段】複数の第1の電極配線と、第1の電極配線と交差する複数の第2の電極配線と、1本の第2の電極配線と、互いに隣接する2本の第1の電極配線との間に形成される1個のビアプラグであって、前記第1の電極配線に対向する底面の、第1の電極配線の伸長方向に垂直な方向の最大径が、第1の電極配線幅の2倍と第1の電極配線間の幅を加えた長さよりも小さいビアプラグと、ビアプラグと2本の第1の電極配線の一方との間に形成される第1の記憶素子と、ビアプラグと2本の第1の電極配線の他方との間に形成される第2の記憶素子とを有する記憶装置。

(もっと読む)

フローティングゲート半導体メモリデバイスおよびそのようなデバイスの製造方法

【課題】NANDフラッシュメモリデバイスを電気的、物理的に小型化し、良好なデータ保持と電気的特性を備えたフローティングゲートデバイスを提供する。

【解決手段】フローティングゲートメモリデバイスの製造方法に関し、ベース基板100、埋め込み絶縁層、および単結晶半導体上部層から形成される、半導体−オン−絶縁体基板が提供される。トレンチが基板中に形成され、フローティングゲートとして働く単結晶上部部分を有する高層フィン型構造111−114を形成する。埋め込み絶縁層の一部は、フローティングゲートデバイスのトンネル酸化物層101’として働く。ゲート誘電体層160は、熱酸化により単結晶上部部分の側壁の上に形成され、薄い膜厚のゲート誘電体層を可能にする。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲート電極および当該選択ゲート電極に隣接する他のゲート電極間の間隔を所望の距離に調整できるようにした不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】複数本のラインパターンのうち選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてマスクした条件にて複数本のラインパターンの側壁面をスリミングし、選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてパターン間膜を埋込むと共にスリミングされたラインパターンの側壁面に沿ってパターン間膜を形成し、選択ゲート電極の形成領域のラインパターンをマスクした条件にて当該ラインパターン以外のラインパターンを除去しマスクされたラインパターンを残留させ、パターン間膜および残留したラインパターンをマスクとして第1膜を異方性エッチングし、第1膜をマスクとして導電膜をエッチングする不揮発性半導体記憶装置の製造方法を提供する。

(もっと読む)

半導体メモリ素子及びその製造方法

【課題】垂直型トランジスタを形成する過程において、ゲートと接触する活性領域の面積を増加させてゲートの接触抵抗特性を改善し、チャネル幅を増加させる半導体メモリ素子及びその製造方法を提供する。

【解決手段】第1の方向に延長するように形成された下部ピラーと、下部ピラー上に第1の方向と垂直な第2の方向に突出するように形成された上部ピラー290と、下部ピラーの一側壁に配置された埋め込みビットライン接合領域265と、トレンチを一部埋め込む埋め込みビットライン280と、エッチング停止膜285a上に形成された少なくとも上部ピラーの外周側面の一部を露出するようにリセスされた第1の層間絶縁膜290と、第1の層間絶縁膜上に形成された第2の層間絶縁膜295と、側面の一部が露出した上部ピラーの外周側面を覆いつつ、埋め込みビットラインと相互交差するゲート320aとを備えるように形成される。

(もっと読む)

不揮発性記憶素子および不揮発性記憶装置

【課題】電極と抵抗変化層の界面に小さな突起を形成することなく、低電圧での初期化が可能な不揮発性記憶素子を提供する。

【解決手段】下部電極105と上部電極107との間に介在され、両電極間に与えられる電気的信号に基づいて可逆的に抵抗値が変化する抵抗変化層116を備える。抵抗変化層116は、第1の抵抗変化層1161と第2の抵抗変化層1162との少なくとも2層から構成され、第1の抵抗変化層1161は第1の遷移金属酸化物116bから構成され、第2の抵抗変化層1162は、第2の遷移金属酸化物116aと第3の遷移金属酸化物116cとから構成され、第2の遷移金属酸化物116aの酸素不足度は第1の遷移金属酸化物116bの酸素不足度及び第3の遷移金属酸化物116cの酸素不足度のいずれよりも高く、第2の遷移金属酸化物116a及び第3の遷移金属酸化物116cは、第1の抵抗変化層1161と接している。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を高い歩留りで製造し得る半導体装置の製造方法を提供する。

【解決手段】ゲート配線16aを形成するのと同時に形成された位置合わせマーク16fに対して位置合わせして、コンタクトホールの第1の部分パターン61a1をゲート配線の一部と重なり合うようにフォトレジスト膜に露光する工程と、活性領域11bを形成するのと同時に形成された位置合わせマーク11fに対して位置合わせして、コンタクトホールの第2の部分パターン61a2を活性領域の一部と重なり合うようにフォトレジスト膜に露光する工程と、フォトレジスト膜を現像し、第1の部分パターンと第2の部分パターンとが露光された箇所に開口部を形成する工程と、フォトレジスト膜をマスクとして絶縁膜をエッチングし、ゲート配線とソース/ドレイン拡散層20とに達するコンタクトホールを形成する工程とを有している。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

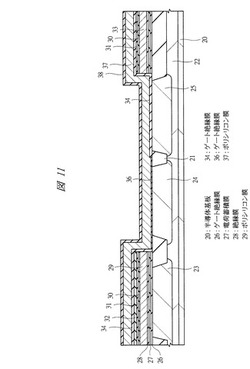

不揮発性半導体記憶装置及びその製造方法

【課題】動作特性の向上を図ることができる不揮発性半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコンを含む基板と、前記基板上に間隔をあけて設けられた複数のメモリセルと、前記メモリセルの側壁に形成された絶縁膜と、を備えている。そして、前記絶縁膜は、前記メモリセル同士の間に形成された空隙部の上方において、隣接する前記メモリセルに向けて突出する突出部を有している。

(もっと読む)

81 - 100 / 734

[ Back to top ]