Fターム[5F083PR07]の内容

Fターム[5F083PR07]に分類される特許

161 - 180 / 734

半導体装置の製造方法

【課題】側壁接合領域を有した半導体装置の製造方法を提供する。

【解決手段】基板をエッチングしてトレンチを形成するステップと、前記トレンチ底面の基板内に接合領域を形成するステップと、前記トレンチ底面を一定の深さエッチングして側壁接合領域を形成するステップと、前記側壁接合領域に接続するビットラインを形成するステップと、を含む半導体装置の製造方法。

(もっと読む)

不揮発性記憶装置

【課題】基板の活性領域と制御ゲート電極との間の高い耐電圧特性を有する不揮発性記憶装置を提供する。

【解決手段】素子分離絶縁溝を有する基板と、前記基板上の前記素子分離溝の両側に形成された第1および第2のトンネル絶縁膜、第1および第2の浮遊ゲート電極と、前記第1および第2の浮遊ゲート電極の上面を覆い、かつ前記第1の浮遊ゲート電極と第2の浮遊ゲート電極との間、前記第1のトンネル絶縁膜と第2のトンネル絶縁膜との間、および前記素子分離絶縁溝の少なくとも上部を埋めるように形成されたゲート間絶縁膜と、前記ゲート間絶縁膜上に形成された制御ゲート電極と、を有する不揮発性記憶装置を提供する。前記ゲート間絶縁膜は、電子トラップ性を有する第1の絶縁材料からなる電子トラップ層と、前記第1の材料よりも電子トラップ性が低い第2の絶縁材料からなり、前記電子トラップ層を挟む第1および第2の絶縁層とを含む。

(もっと読む)

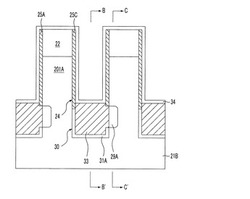

半導体装置

【課題】コンタクト抵抗の上昇を防止することが可能な半導体装置を提供すること。

【解決手段】シリコン基板に形成される複数の拡散領域と、複数の拡散領域にボトム部が接続して形成される複数のコンタクトプラグ33と、ボトム部を含んでシリコン基板上に形成されるアモルファスカーボン膜24とを備え、ボトム部はアモルファスカーボン膜24を貫通して拡散領域に接合される。アモルファスカーボン層24をコンタクトプラグ33形成時のエッチングストッパ層として用いることで、拡散領域がオーバーエッチングによりダメージを受けることが防止される。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

【解決手段】基板上で第1方向に延在するラインパターンと、ラインパターンの端部から、第1方向と異なる方向に延在する分岐ラインパターンとをそれぞれ含む第1導電ライン;第2導電ライン;第3導電ラインとを含む半導体素子であり、中間に位置する導電ラインの分岐ラインパターンは、他の導電ラインの分岐ラインパターン間に位置し、長さもさらに短い。これにより、コンタクト・パッドが、導電ラインの分岐ラインパターンと一体に形成されうる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】書込・消去特性が高く、動作の信頼性が高い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板と、前記半導体基板上に設けられたトンネル絶縁膜と、前記トンネル絶縁膜上に設けられた第1電極と、前記第1電極上に設けられた電極間絶縁膜と、前記電極間絶縁膜上に設けられた第2電極と、を備える。前記電極間絶縁膜は、積層絶縁層と、前記積層絶縁層上に設けられ、前記積層絶縁層よりもバリアハイトが低い電荷蓄積層と、前記電荷蓄積層上に設けられ、前記電荷蓄積層よりもバリアハイトが高いブロック絶縁層と、を有する。前記積層絶縁層は、第1絶縁層と、前記第1絶縁層上に設けられ、前記第1絶縁層よりもバリアハイトが低い量子効果層と、前記量子効果層上に設けられ、前記量子効果層よりもバリアハイトが高い第2絶縁層と、を有する。

(もっと読む)

垂直型トランジスタの不純物領域の形成方法及びこれを利用する垂直型トランジスタの製造方法

【課題】位置及び不純物濃度を精密に制御できるようにする垂直型トランジスタの不純物領域の形成方法及びこれを利用する垂直型トランジスタの製造方法を提供すること。

【解決手段】半導体基板に対するイオン注入を行って半導体基板の下部に不純物イオン接合領域を形成するステップと、そして、半導体基板に対するエッチングによりトレンチを形成し、エッチングは、不純物イオン接合領域の一部が除去されるようにして、不純物イオン接合領域のうち、除去されずに残っている領域がトレンチ下部で露出して埋め込みビットライン接合領域として機能するように行うステップとを含むことを特徴とする。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】生産性を向上した一括加工型3次元積層メモリ構成の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、積層構造体MLと、選択ゲート電極SGと、半導体ピラーSPと、記憶層48と、内側絶縁膜42と、外側絶縁膜43と、選択ゲート絶縁膜SGIと、を備えた不揮発性半導体記憶装置が提供される。積層構造体は、第1方向に積層された複数の電極膜61と、電極間絶縁膜62と、を有する。選択ゲート電極は、積層構造体と積層された複数の選択ゲート導電膜71と、選択ゲート導電膜間絶縁膜72と、を有する。半導体ピラーは、積層構造体及び選択ゲート電極を第1方向に貫通する。記憶層は、電極膜と半導体ピラーとの間に、内側絶縁膜は、記憶層と半導体ピラーとの間に、外側絶縁膜は、記憶層と電極膜との間に、選択ゲート絶縁膜は、選択ゲート導電膜と半導体ピラーとの間に設けられる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 上部電極の膜減りが生じ難いプレーナ型強誘電体キャパシタの製造方法を提供する。

【解決手段】 半導体基板の上に、下部電極層、強誘電体層、上部電極層を形成する。上部電極層の上に、第1の方向に並ぶハードマスクパターンを形成する。ハードマスクパターンをエッチングマスクとして、上部電極層及び強誘電体層をエッチングすることにより、上部電極及びキャパシタ誘電体膜を形成する。第1の方向に並んだハードマスクパターン及び下部電極層の一部を、連続したレジストパターンで覆う。レジストパターン及びキャパシタ誘電体膜をエッチングマスクとして、下部電極層をエッチングすることにより、下部電極を形成する。下部電極の、第1の方向に延在する両側の縁が、ハードマスクパターンの間の領域において、内側に向かって窪むように、レジストパターン及びハードマスクパターンの形状及び寸法が設定されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】歩留まりに優れた構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、基板内の記憶回路領域に形成されており、多層配線層内に埋め込まれた少なくとも1以上の容量素子および周辺回路を有する記憶回路と、平面視において、基板内の憶回路領域とは異なる領域である論理回路領域に形成された論理回路と、を備え、容量素子は、下部電極、容量絶縁膜、上部電極、埋設電極および、上部接続配線で構成されており、上部接続配線と埋設電極とは、同一の材料かつ一体に構成されており、上部接続配線と下部電極との間には、論理回路を構成する前記配線が少なくとも1以上設けられており、上部接続配線の上面と、上部接続配線と同じ配線層に形成された論理回路を構成する配線の上面とが、同一面を構成する。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタ特性の劣化を抑制し、かつ耐疲労特性を制御可能とする。

【解決手段】半導体基板10の上方に下部電極16を形成する工程と、下部電極16上に第1誘電体膜18を形成する工程と、酸化性ガスを含む雰囲気中で605℃以上の温度において熱処理することにより、第1誘電体膜18を結晶化する工程と、第1誘電体膜18上に第2誘電体膜20を形成する工程と、第2誘電体膜20を形成した後に熱処理を行なわず上部電極の少なくとも一部の層22を形成する工程と、酸化性ガスを含む雰囲気で熱処理することにより、第2誘電体膜20を結晶化する工程と、第2誘電体膜20および第1誘電体膜18をエッチングする工程と、エッチングする工程の後、側面が露出した状態において酸化性ガスを含む雰囲気中で550℃以上の温度で熱処理する工程と、を含み、第2誘電体膜20の膜厚は第1誘電体膜18の膜厚の30%以上である半導体装置の製造方法。

(もっと読む)

半導体記憶装置

【課題】メモリセルから正確にデータを読み出すことができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1ワード線1と、ビット線2と、抵抗変化材4とを備える。ビット線2は第1の面が第1ワード線1と対向するように第1ワード線1と交差する。抵抗変化材4は第1ワード線1とビット線2との各交差部に配置される。また半導体記憶装置は、第2ワード線3と、絶縁膜5とを備える。第2ワード線3はビット線2の第1の面とは反対側の第2の面と対向するようにビット線2と交差する。絶縁膜5は第2ワード線3とビット線2との各交差部に配置される。1つの第1ワード線1と1つの第2ワード線3とは、ビット線2を挟み込むように配置される。第2ワード線3、ビット線2、及び絶縁膜5は、各交差部において電界効果トランジスタを構成する。電界効果トランジスタと抵抗変化材4とにより1つのメモリセルが構成される。

(もっと読む)

半導体装置およびその製造方法

【課題】オフ電流を低減し、特性ばらつきが抑制された多結晶半導体層をチャネル領域とする半導体装置の製造方法を提供する。

【解決手段】半導体基板の上に絶縁体層を形成する工程と、絶縁体層上に狭窄部を有する非晶質または多結晶質の半導体層を形成する工程と、半導体層上に半導体層よりも熱膨張係数の大きい絶縁体層を形成する工程と、熱処理を行う工程と、絶縁体層を除去する工程と、狭窄部の側面にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、半導体層中にソース・ドレイン領域を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】デバイス特性及びプロセスのばらつきを低減できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板10と、下部ゲート層BGと、積層体と、ダミー電極層DWLと、絶縁膜30と、チャネルボディ20,45とを備えた。下部ゲート層BGは、基板10上に設けられた。積層体は、下部ゲート層BG上にそれぞれ交互に積層された複数の絶縁層と複数の電極層WLとを有する。ダミー電極層DWLは、下部ゲート層BGと積層体との間に設けられ、電極層WLと同じ材料からなり、各々の電極層WLよりも厚い。絶縁膜30は、積層体及びダミー電極層を貫通して形成されたホールMHの側壁に設けられた電荷蓄積膜を含む。チャネルボディ20,45は、ホールMH内における絶縁膜30の内側に設けられた。

(もっと読む)

半導体装置の製造方法

【課題】溝内の一部のみを覆うマスクパターンを、フォトレジスト膜を用いて形成する必要のない半導体装置の製造方法を提供する。

【解決手段】半導体基板1に、第1溝7を形成する工程と、第1溝7に第1絶縁膜8を形成する工程と、上面が第1絶縁膜の上端よりも下方になるように第1溝7内に第1導電膜9を充填する工程と、第1溝7の側面にカーボン膜10を形成する工程と、第1溝7内を第2絶縁膜11で充填する工程と、第1溝7内の側面の一方を覆うカーボン膜10を除去し、第1絶縁膜8の一部を露出させる工程と、第2絶縁膜11と露出された第1絶縁膜8を除去し、半導体基板1の一部を露出する工程と、を有することを特徴とする。

(もっと読む)

埋め込みビットラインを備えた半導体装置およびその製造方法

【課題】埋め込みビットラインと接合を安定的にコンタクトさせることができ、埋め込みビットラインとコンタクトされる接合の深さを均一に形成できる半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置製造方法は、基板をエッチングして何れか1つの側壁がステアを有するトレンチを形成するステップと、前記ステアの表面下部に接合部を形成するステップと、前記接合部とコンタクトされる埋め込みビットラインを形成するステップと、を含むことを特徴とする。本発明は、垂直セル構造の埋め込みビットライン製造時に使用されるマスクの個数を顕著に減少させることができ、工程ステップを減少させ、行うことができるため工程の単純化および工程難易度、原価節減の側面で非常に有利である。

(もっと読む)

半導体装置の製造方法

【課題】ビット線材料埋設体の形状のばらつきに起因するビット線の配線抵抗値のばらつきを防ぐ半導体装置の製造方法を提供する。

【解決手段】製造方法は、第一溝4内に第一のビット線材料埋設体6および第二のビット線材料埋設体10からなるビット線11を形成する第一工程と、ビット線11に含まれる不純物を拡散させて第一不純物拡散領域13を形成する第二工程と、ピラー部1bを形成する第三工程と、ピラー部1bに対向する配線17を第二溝15内に形成する第四工程と、ピラー部1bの先端部に、第二不純物拡散領域19を形成する第五工程と、を具備し、第一工程が、第一溝4を完全に埋め込むように第一ビット線材料を形成した後に第一ビット線材料表面を平坦化し、第一溝4底部に残るように第一ビット線材料をエッチバックする工程を具備する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルに書き込み用のトランジスタ、読み出し用のトランジスタおよび選択用のトランジスタを備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置の製造方法

【課題】工程数が多く、煩雑になる問題を解決する半導体装置の製造方法を提供する。

【解決手段】半導体基板1に第1絶縁膜2を形成し、第1領域Aに第1導電型の第1ウエル層31を形成し、第1領域A以外の第1絶縁膜2上に第1半導体膜3を形成し、第1ウエル層31にトランジスタを形成し、第1半導体膜3及び第1領域Aの第1絶縁膜2の上に、トランジスタのビットコンタクトを兼ねる第2半導体膜7を形成する工程、第2半導体膜7上に、第2領域用B1のマスク8を積層してから、第1または第2導電型ドーパントを注入して第2ウエル層32を形成し、次いで、第2領域B1の少なくとも第2半導体膜7に、ドーパントを注入する工程、第2半導体膜7上に導電膜を積層してから、第1、第2半導体膜3,7及び導電膜を部分的にエッチングして、第1領域Aにトランジスタのビット配線層を、第2領域B1,B2に別の配線層を形成する工程、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】サイドウォールスペーサを利用してリソグラフィー解像限界未満のパターンと任意の寸法のパターンとが混在するパターンを形成する。

【解決手段】アモルファスカーボン膜3及びシリコン酸窒化膜4からなる被エッチング部材上に塗布膜5をスピン塗布法により成膜し、塗布膜5をパターニングすることによってサイドウォールコアを形成し、サイドウォールコアの少なくとも側面を覆うシリコン酸化膜7を成膜し、シリコン酸化膜7上に有機反射防止膜8をスピン塗布法により成膜する。次いで、有機反射防止膜8をエッチングすることによって、シリコン酸化膜7の凹部7aを覆う埋込マスクを形成し、シリコン酸化膜7をエッチングすることにより、サイドウォールコアまたは埋込マスクと重ならない被エッチング部材を露出させ、被エッチング部材をエッチングすることでフォトリソグラフィー解像限界未満のパターンを得る。

(もっと読む)

161 - 180 / 734

[ Back to top ]