Fターム[5F083ZA07]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリセルと周辺回路の関係 (1,873) | MOSFETの構造が異なるもの (1,090) | ゲート絶縁膜が異なるもの (403)

Fターム[5F083ZA07]に分類される特許

361 - 380 / 403

半導体装置

【課題】電源電圧1V程度のような低い電圧で動作するスタテックメモリにおいて、サブスレショルド電流による待機時の漏れ電流の問題を避けながら、低電力化と動作速度の向上を図る。電源電圧の低下によって減少するスタテックメモリのメモリセルの電圧マージンの確保を図る。

【解決手段】交差結合した比較的高いしきい電圧をもつMOSトランジスタからなるスタティックメモリセルにおいて、その給電線電圧を制御するMOSトランジスタを設けておく。非選択状態にあるメモリセル内の2つの記憶ノードの電圧差が、データ対線DL,/DLから選択メモリセル内の該2つのノードに書き込み情報に対応した電圧が印加された時の該2つのノードの電圧差よりも大きくなるように、ワード線電圧がオフになった後に該給電線電圧制御トランジスタをオンにして高電圧VCHを給電線に与える。

(もっと読む)

半導体記憶装置

【課題】DQゲートに確実にビット線選択信号CSLのパルス信号を供給し、さらにセンスアンプバンク内でのビット線選択信号CSLのスキューを抑え、高速な読み出し及び書き込み動作が可能な半導体記憶装置を提供する。

【解決手段】ビット線対BL、/BLとデータ線対DQ、/DQとの間に配置されたDQゲートは、ビット線選択信号LCSLによってビット線対とデータ線対との間を接続状態あるいは遮断状態のいずれかの状態に設定する。CSL制御回路13Aは、DQゲートに供給されるビット線選択信号LCSLを制御する。CSL制御回路13AとDQゲートとの間に配置されたリドライバRDは、CSL制御回路13Aから供給されたビット線選択信号GCSLを駆動して、信号LCSLをDQゲートへ出力する。センスアンプ、データ線対、DQゲートによりセンスアンプバンク12が構成され、リドライバRDはセンスアンプバンク12内に配置されている。

(もっと読む)

埋め込みDRAMメモリにおいて大きいキャパシタンスを得るための製造プロセス

【課題】水平方向のビットセルサイズを小さくしても比較的高いキャパシタンスを維持できる埋め込みDRAMとその製造方法を提供する。

【解決手段】深いトレンチアイソレーション領域で分離されたDRAMセルのアレイと、浅いトレンチアイソレーション領域で分離されたロジックトランジスタを有する埋め込みメモリシステムにおいて、イオン注入で形成された、部分的に深いトレンチアイソレーション領域のキャビティ360の側壁にも延在する電極を備えたキャパシタ構造を設けることで、水平方向の占有面積を大きくせずに、キャパシタの電極の重なりの面積を増加させてキャパシタンスを高くできる。この構造の製造プロセスは、従来のプロセスに、僅かなマスキング・エッチング工程の追加程度の改変を加えるだけで実現できる。。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高速動作が可能なLDD型MISFETと、かつ高電圧駆動が可能なLDD型MISFETとを内蔵する半導体集積回路装置を低コストで実現する。

【解決手段】高速動作が可能なMISFETは、ゲートサイドウオール層に自己整合された高濃度領域に金属シリサイド層を有し、高電圧駆動が可能なMISFETは、上記ゲートサイドウオール層の幅よりも大きい幅を有するLDD部を有し、そのLDD部に接して高濃度領域を有し、そしてその高濃度領域に金属シリサイド層を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】 高電圧MOSFETと低電圧MOSFETとが共存する半導体製造プロセスにおいて、結晶欠陥起因によるリークを低減する。

【解決手段】 半導体基板11に素子分離絶縁膜12に囲まれた第1および第2の活性領域1,2を形成する。次に、第1および第2の活性領域上に第1の熱酸化膜および化学的気相成長法による第1の酸化膜を形成する。次に、第2の活性領域上に形成された第1の熱酸化膜と第1の酸化膜を除去する。次に、第2の活性領域上に第2の熱酸化膜を形成して単層絶縁膜13bを形成するとともに、第1の活性領域上に第1の熱酸化膜および第1の酸化膜を含む積層絶縁膜13aを形成する。次に、積層絶縁膜および単層絶縁膜上にゲート電極14a,14bとなる導電膜を形成する。ここで、積層絶縁膜の膜厚を単層絶縁膜の膜厚よりも厚く形成し、第1の熱酸化膜は急速熱酸化法によって形成する。

(もっと読む)

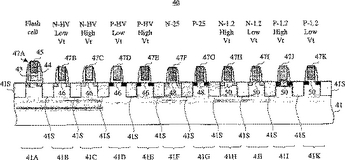

パンチスルー耐性を向上させた半導体集積回路装置およびその製造方法、低電圧トランジスタと高電圧トランジスタとを含む半導体集積回路装置

集積回路装置は、フラッシュメモリ素子が形成されるメモリセルウェルと、それぞれ高電圧トランジスタが形成される、互いに逆導電型の第1のウェルと第2のウェルと、それぞれ低電圧トランジスタが形成される、互いに逆導電型の第3のウェルと第4のウェルとを含み、前記第1および第2のウェルの少なくとも一方、および前記第3および第4のウェルの少なくとも一方は、前記メモリセルウェルの不純物濃度分布プロファイルよりも急峻な不純物濃度分布プロファイルを有する。  (もっと読む)

(もっと読む)

半導体記憶装置とその製造方法

【課題】DRAMのメモリセルを構成するトランジスタとして良好な特性を持ち、且つ微細化にも好適な構成の半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体基板11と、この半導体基板11上に形成された素子分離領域28と、この素子分離領域28の間の前記半導体基板上に形成され凸部を有する素子形成領域30と、この素子形成領域30の凸部に形成されたチャネル部を有するトランジスタTraと、このトランジスタTraに接続されて前記半導体基板内または半導体基板上に形成されたキャパシタCt、Csとを具備し、前記素子形成領域30の凸部は前記トランジスタTraのチャネル幅方向に沿って互いに対面する第1、第2斜面とこの第1、第2斜面間に形成された上面とを有し、この上面のチャネル幅方向の幅が60nm以下で、かつ前記第1、第2斜面の延長で作られる頂角が鋭角であることを特徴とする半導体記憶装置。

(もっと読む)

半導体装置

【課題】同一半導体基板上に形成された複数種類のゲート絶縁膜の膜厚及び電気的特性のバラツキを防止する。

【解決手段】同一半導体基板1上に、互いに膜厚が異なる複数種類のゲート絶縁膜5,11をもって複数の素子形成領域3a,3bが形成されている。ゲート絶縁膜5,11上にポリシリコンからなるゲート電極13a,13bが形成されている。ゲート絶縁膜5,11は単層膜で形成されている。各々のゲート絶縁膜5,11上に形成されたゲート電極13a,13bは同一のポリシリコン膜から同時に形成されたものである。

(もっと読む)

半導体装置とその製造方法

所望の特性を果たす複数種類のトランジスタを少ない工程数で製造する。 半導体装置は、第1の深さに達する素子分離領域と、第1導電型の第1および第2のウェルと、第1のウェルに形成され、第1の厚さのゲート絶縁膜と、第2導電型のソース/ドレイン領域およびゲート電極とを有する第1のトランジスタと、第2のウェルに形成され、第1の厚さより薄い第2の厚さのゲート絶縁膜と、第2導電型のソース/ドレイン領域およびゲート電極とを有する第2のトランジスタと、を有し、第1のウェルは、第1の深さと同等又はより深い深さにのみ極大値を有する第1の不純物濃度分布を有し、第2のウェルは、第1のウェルと同一の第1の不純物濃度分布に第1の深さより浅い第2の深さに極大値を有する不純物濃度分布を重ね合わせ、全体としても第2の深さにも極大値を示す第2の不純物濃度分布を有する。  (もっと読む)

(もっと読む)

半導体装置

【課題】周辺回路ゲート酸化膜の損傷を防止しつつ、メモリトランジスタの良好な書込みを行なうことができる半導体装置を提供する。

【解決手段】半導体基板1上に形成されたメモリゲート酸化膜15とメモリゲート酸化膜15上に形成された電気的に浮遊状態のポリシリコンからなる浮遊ゲート17をもつメモリトランジスタと、半導体基板1上に形成された選択ゲート酸化膜11とメモリゲート酸化膜11上に形成されたポリシリコンからなる選択ゲート13をもちメモリトランジスタに直列に接続された選択トランジスタを備えた不揮発性メモリセルと、半導体基板1上に形成された周辺回路ゲート酸化膜23と周辺回路ゲート酸化膜23上に形成されたポリシリコンからなる周辺回路ゲート25をもつ周辺回路トランジスタを備え、メモリゲート酸化膜15の膜厚は周辺回路ゲート酸化膜23の膜厚よりも薄く形成されている。

(もっと読む)

半導体装置とその製造方法

不揮発性メモリ素子と絶縁ゲートを有する電界効果トランジスタを含む周辺回路とを含む半導体装置とその製造方法に関する。保持能力の高いメモリ素子と、駆動電流の高い絶縁ゲートを有する電界効果トランジスタとを有する半導体装置とその製造方法を提供する。 半導体装置は、第1および第2の領域(AR1,AR2)を有する半導体基板(1)と、前記第1の領域上に形成された不揮発性メモリ素子用のフローティングゲート構造(4,5,6,7,8)と、前記フローティングゲート構造に結合して形成されたコントロールゲート構造(14)と、前記第2の領域上に形成された論理回路用の絶縁ゲート電極(12,14)と、を有し、前記フローティングゲート構造は前記絶縁ゲート電極よりも大きなバーズビークを有する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

一又は複数のピクセルが形成される画素領域と、各ピクセルからの出力信号を記憶する一又は複数のDRAMセルが形成されるDRAMセル領域とを含み、画素領域及びDRAMセル領域を構成する各層が同一の半導体プロセスによって形成されて成ることを特徴とする。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】 メモリセルの電荷蓄積層を窒化シリコン膜で構成する不揮発性半導体記憶装置において、窒化シリコン膜中の電荷トラップを増加させる。

【解決手段】 コントロールゲート8の一方の側壁にONO膜16を挟んでメモリゲート9を形成したメモリセル構造を有し、ONO膜16の電荷蓄積層を構成する窒化シリコン膜16bに電子を注入して書き込みを行い、正孔を注入して消去を行うMONOS型不揮発性メモリにおいて、窒化シリコン膜16bの成膜にプラズマALD法を用い、膜の密度を2.65g/cm3以上、好ましくは2.73g/cm3以上、より好ましくは2.8g/cm3以上とすることにより、正孔の捕獲効率が向上した窒化シリコン膜16bを得る。

(もっと読む)

半導体装置とその製造方法

【課題】 歩留まりが向上して信頼性の高いフラッシュメモリセルを備えた半導体装置とその製造方法を提供すること。

【解決手段】 第1窓70aを有する第1レジストパターン70を第2絶縁膜69上に形成する工程と、第1レジストパターン70をエッチングマスクにしてコンタクト領域CRが露出する第1開口69dを形成する工程と、第1レジスト部76aを有する第2レジストパターン76を第2導電膜74上に形成する工程と、第2レジストパターン76をエッチングマスクにし、第1、第2導電体67a、74a、フローティングゲート67d、及びコントロールゲート74dを形成する工程と、第3レジストパターン80を各領域I、IIに形成する工程と、第3レジストパターン80をエッチングマスクにして第2窓80a下の第2導電体74aを除去する工程と、を有する半導体装置の製造方法による。

(もっと読む)

半導体装置

【課題】高性能な書き込み消去特性を有する不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板のp型ウエル2上にゲート絶縁膜6を介して選択ゲート18が形成され、p型ウエル2上に酸化シリコン膜15a、窒化シリコン膜15bおよび酸化シリコン膜15cからなる積層膜15を介してメモリゲート17が形成される。メモリゲート17は、積層膜15を介して選択ゲート18に隣接する。p型ウエル2の選択ゲート18およびメモリゲート17の両側の領域には、ソース、ドレインとしてのn型の不純物拡散層20,21が形成されている。積層膜15に電子を注入することにより、書き込みが行われ、積層膜15にホールを注入することで消去が行われる。積層膜15にホールを注入する際には、積層膜15へのホール注入のための電圧パルスをメモリゲート17および不純物拡散層20に複数回印加する。

(もっと読む)

不揮発性半導体記憶装置

【課題】 信頼性を確保しつつ、書込み速度を確保することができる不揮発性半導体記憶装置を提供する。

【解決手段】 半導体基板40と、半導体基板上40に形成された絶縁膜39と、半導体基板40上に形成された複数のメモリセルと、絶縁膜40上に形成され、メモリセルに向けて延在する複数の第1アシストゲートと、第1アシストゲートの端部を接続し、絶縁膜上に形成された接続部7と、接続部よりメモリセル側に配置され、メモリセルに向けて延在する第2アシストゲート11と、第1アシストゲート下の領域に電圧を印加するか否かを制御する第1選択トランジスタと、第2アシストゲート11下の領域に電圧を印加するか否かを制御する第2選択トランジスタ10dと、第2アシストゲート11と第2選択トランジスタ10dとの間に形成された不純物領域とを備え、接続部7と不純物領域との交差領域下に形成された絶縁膜39を、第1アシストゲート下および第2アシストゲート11下に形成された絶縁膜39より厚くした。

(もっと読む)

半導体装置とその製造方法

【課題】 周辺回路領域に形成されるロジック回路等に不具合が発生するのを防ぐことができるフラッシュメモリセルを備えた半導体装置とその製造方法を提供すること。

【解決手段】 第1導電体25aのコンタクト領域CR上の第2絶縁膜26を除去する工程と、第2絶縁膜26の上に第2導電膜30を形成する工程と、第1導電体25aのコンタクト領域CR上の第2導電膜30を除去し、該第2導電膜30を第2導電体30aとする工程と、第2導電体30aを覆う層間絶縁膜(第3絶縁膜)44を形成する工程と、コンタクト領域CR上の層間絶縁膜44に第1ホール44aを形成する工程と、コンタクト領域CRと電気的に接続される導電性プラグ45aを第1ホール44a内に形成する工程と、を有することを特徴とする半導体装置の製造方法による。

(もっと読む)

半導体素子およびその製造方法

【課題】 本発明は、障壁金属層に電気的特性およびストレス特性に優れた金属物質を使用すると同時に、セル領域に形成されるメモリセルと周辺回路領域に形成されるトランジスタの段差を最小化しメモリセルのゲート高さを最小化することにより、後続の工程を容易にし、ゲートが高く形成されて発生した問題点を解決し、素子の電気的特性を向上させることが可能な半導体素子及びその製造方法を提供することを目的としている。

【解決手段】 本発明の半導体素子は、全体構造上に形成され、ダマシンパターンが形成された層間絶縁膜、ダマシンパターンに形成された金属層、及び金属層と層間絶縁膜との間に形成され、WNまたはTiSiNからなる障壁金属層を含む構成としたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】微細な領域におけるデバイスの信頼性を確保し、大容量で高速動作を可能とする。

【解決手段】半導体基板1の主表面の第1の領域にゲート絶縁膜2と、浮遊ゲート電極3,7と、層間絶縁膜15と、制御ゲート電極8と、第2導電型のソース領域11およびドレイン領域10からなるメモリセルをマトリックス状に配置し、メモリセルの素子分離を浅溝素子分離構造としたものである。素子分離に絶縁膜の埋込みによる浅溝構造を用いることにより微細領域での素子分離耐圧の低下を防止し、さらに選択トランジスタのしきい値ばらつきを低減でき、また、メモリマット内のメモリセルを選択トランジスタによって分割することによりメモリセルのディスターブ耐性を改善できる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】微細な領域におけるデバイスの信頼性を確保し、大容量で高速動作を可能とする。

【解決手段】半導体基板1の主表面の第1の領域にゲート絶縁膜2と、浮遊ゲート電極3,7と、層間絶縁膜15と、制御ゲート電極8と、第2導電型のソース領域11およびドレイン領域10からなるメモリセルをマトリックス状に配置し、メモリセルの素子分離を浅溝素子分離構造としたものである。素子分離に絶縁膜の埋込みによる浅溝構造を用いることにより微細領域での素子分離耐圧の低下を防止し、さらに選択トランジスタのしきい値ばらつきを低減でき、また、メモリマット内のメモリセルを選択トランジスタによって分割することによりメモリセルのディスターブ耐性を改善できる。

(もっと読む)

361 - 380 / 403

[ Back to top ]